# MOS INTEGRATED CIRCUIT $\mu$ PD78P083

#### 8-BIT SINGLE-CHIP MICROCOMPUTER

The  $\mu$ PD78P083 is a member of the  $\mu$ PD78083 subseries, which is part of the 78K/0 Series. It includes an on-chip 24-Kbyte one-time programmable (OTP)ROM or EPROM.

Because this device can be programmed by users, it is ideally suitable for application system evaluation in development stages, small-scale production of many different devices, and quick product release to a hot market.

For specific functions and other detailed information, consult the following user's manuals. These manuals are required reading for design work.

μPD78083 Subseries User's Manual : IEU-1407

78K/0 Series Users Manual — Instruction — : IEU-1372

#### Features

- Pin-compatible with mask ROM versions (except for VPP pin)

- Internal PROM: 24 Kbytes Note

- μPD78P083DU : reprogrammable (suitable for system evaluation)

- μPD78P083CU and μPD78P083GB : one-time programmable (suitable for small-scale production)

- Internal high-speed RAM: 512 bytes Note

- Operates over the same power supply voltage range as for mask ROM versions: 2.0 to 5.5 V

**Note** Internal PROM and internal high-speed RAM capacities can be changed with the internal memory switching register.

#### $\cdot$ This product differs from mask ROM versions in the following respects. -

Memory mapping is different. To get the same memory mapping as mask ROM versions, the internal memory switching register should be set.

#### **Ordering Information**

| Part No.         | Package                                          | Internal ROM  |

|------------------|--------------------------------------------------|---------------|

| μPD78P083CU      | 42-pin plastic shrink DIP (600 mil)              | One-Time PROM |

| μPDD78P083GB-3B4 | 44-pin plastic QFP (10 $	imes$ 10 mm)            | One-Time PROM |

| μPD78P083DU      | 42-pin ceramic shrink DIP (with window)(600 mil) | EPROM         |

#### In this document, all ROM descriptions common to one-time PROM and EPROM are referred to as PROM.

The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

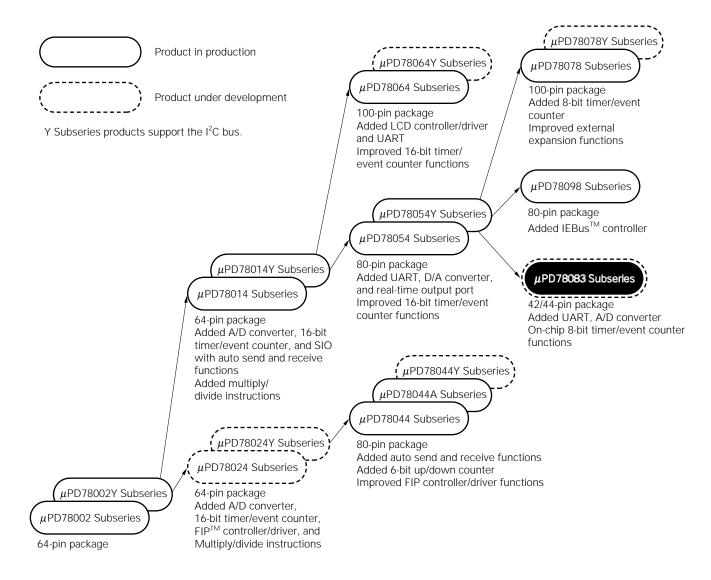

#### Development of 78K/0 Series

#### **Overview of Functions**

|                                   | ltem                       | Function                                                                                                                                                                                   |  |  |  |  |

|-----------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Internal memory                   |                            | <ul> <li>PROM: 24 K bytes Note</li> <li>RAM</li> <li>Internal high-speed RAM: 512 bytes Note</li> </ul>                                                                                    |  |  |  |  |

| Memory sp                         | pace                       | 64 K bytes                                                                                                                                                                                 |  |  |  |  |

| General reg                       | gister                     | Thirty-two 8-bit registers (8 bits $	imes$ 8 registers $	imes$ 4 banks)                                                                                                                    |  |  |  |  |

| Instruction                       | cycle                      | Variable instruction execution time:<br>0.4 μs/0.8 μs/1.6 μs/3.2 μs/6.4 μs/12.8 μs<br>(during 5.0 MHz operation of main system clock)                                                      |  |  |  |  |

| Instruction set                   |                            | <ul> <li>16-bit operation</li> <li>Multiply/divide (8 bits × 8 bits, 16 bits ÷ 8 bits)</li> <li>Bit manipulate (set, reset, test, Boolean operations)</li> <li>BCD adjust, etc.</li> </ul> |  |  |  |  |

| I/O ports                         |                            | Total: 33 lines• CMOS input :1 line• CMOS I/O: 32 lines                                                                                                                                    |  |  |  |  |

| A/D conver                        | ter                        | Eight channel 8-bit A/D converter                                                                                                                                                          |  |  |  |  |

| Serial inter                      | face                       | 3-wire/UART mode selectable: one channel                                                                                                                                                   |  |  |  |  |

| Timers                            |                            | <ul> <li>8-bit timer/event counters: two channels</li> <li>Watchdog timer : one channel</li> </ul>                                                                                         |  |  |  |  |

| Timer outp                        | uts                        | Two lines (Two 8-bit PWM output lines)                                                                                                                                                     |  |  |  |  |

| Clock outp                        | ut                         | 19.5 kHz, 39.1 kHz, 78.1 kHz, 156 kHz, 313 kHz, 625 kHz, 1.25 MHz, 2.5 MHz, and 5.0 MHz (@ 5.0 MHz with main system clock)                                                                 |  |  |  |  |

| Buzzer out                        | put                        | 1.2 kHz, 2.4 kHz, 4.9 kHz, and 9.8 kHz<br>(@ 5.0 MHz with main system clock)                                                                                                               |  |  |  |  |

| Vectored                          | Maskable interrupt         | Internal: 8 causes, external: 3 causes                                                                                                                                                     |  |  |  |  |

| interrupts Non-maskable interrupt |                            | Internal: 1 cause                                                                                                                                                                          |  |  |  |  |

| Software interrupt                |                            | Internal: 1 cause                                                                                                                                                                          |  |  |  |  |

| Operating                         | power supply voltage range | V <sub>DD</sub> = 2.0 to 5.5 V                                                                                                                                                             |  |  |  |  |

| Packages                          |                            | <ul> <li>42-pin plastic shrink DIP (600 mil)</li> <li>44-pin plastic QFP (10 × 10 mm)</li> <li>42-pin ceramic shrink DIP (with window)(600 mil)</li> </ul>                                 |  |  |  |  |

**Note** Internal PROM and internal high-speed RAM capacity can be changed with the internal memory switching register.

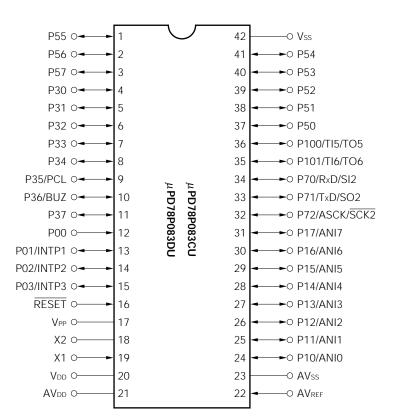

#### Pin Configuration (Top View)

#### (1) Normal operating mode

42-pin plastic shrink DIP (600 mil)

42-pin ceramic shrink DIP (with window)(600 mil)

#### Cautions 1. Connect the VPP pin to Vss directly.

- 2. Connect the AV  $\mbox{\sc b}$  pin to  $V \mbox{\sc d} \mbox{\sc b}$  .

- 3. Connect the AVss pin to Vss.

| P00 - P03     | : Port 0                     | PCL         | : Programmable Clock          |

|---------------|------------------------------|-------------|-------------------------------|

| P10 - P17     | : Port 1                     | BUZ         | : Buzzer Clock                |

| P30 - P37     | : Port 3                     | X1, X2      | : Crystal (Main System Clock) |

| P50 - P57     | : Port 5                     | RESET       | : Reset                       |

| P70 - P72     | : Port 7                     | ANIO - ANI7 | : Analog Input                |

| P100, P101    | : Port 10                    | AVDD        | : Analog Power Supply         |

| INTP1 - INTP3 | : Interrupt from Peripherals | AVss        | : Analog Ground               |

| TI5, TI6      | : Timer Input                | AVREF       | : Analog Reference Voltage    |

| TO5, TO6      | : Timer Output               | Vdd         | : Power Supply                |

| SI2           | : Serial Input               | Vpp         | : Programming Power Supply    |

| SO2           | : Serial Output              | Vss         | : Ground                      |

| SCK2          | : Serial Clock               | NC          | : Non-connection              |

| RxD           | : Receive Data               |             |                               |

| TxD           | : Transmit Data              |             |                               |

| ASCK          | : Asynchronous Serial Clock  |             |                               |

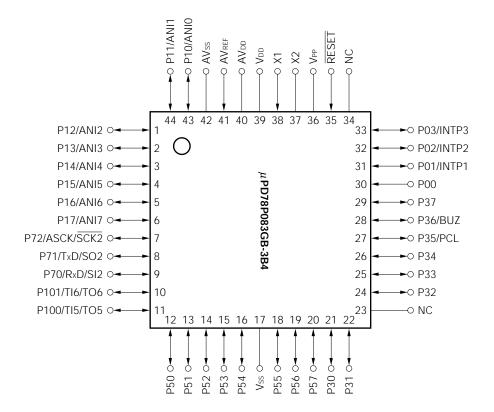

#### 44-pin plastic QFP (10 $\times$ 10 mm)

Cautions 1. Connect the VPP pin to Vss directly.

- 2. Connect the AVDD pin to VDD.

- 3. Connect the AVss pin to Vss.

- 4. Connect the NC pin to Vss as an anti-noise measure (however, it can also be left open).

| P00 - P03     | : | Port 0                     | PCL         | : | Programmable Clock          |

|---------------|---|----------------------------|-------------|---|-----------------------------|

| P10 - P17     | : | Port 1                     | BUZ         | : | Buzzer Clock                |

| P30 - P37     | : | Port 3                     | X1, X2      | : | Crystal (Main System Clock) |

| P50 - P57     | : | Port 5                     | RESET       | : | Reset                       |

| P70 - P72     | : | Port 7                     | ANIO - ANI7 | : | Analog Input                |

| P100, P101    | : | Port 10                    | AVdd        | : | Analog Power Supply         |

| INTP1 - INTP3 | : | Interrupt from Peripherals | AVss        | : | Analog Ground               |

| TI5, TI6      | : | Timer Input                | AVREF       | : | Analog Reference Voltage    |

| TO5, TO6      | : | Timer Output               | Vdd         | : | Power Supply                |

| SI2           | : | Serial Input               | Vpp         | : | Programming Power Supply    |

| SO2           | : | Serial Output              | Vss         | : | Ground                      |

| SCK2          | : | Serial Clock               | NC          | : | Non-connection              |

| RxD           | : | Receive Data               |             |   |                             |

| TxD           | : | Transmit Data              |             |   |                             |

ASCK : Asynchronous Serial Clock

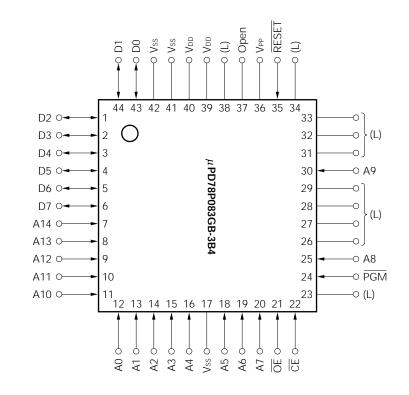

#### (2) PROM programming mode

42-pin plastic shrink DIP (600 mil)

42-pin ceramic shrink DIP (with window)(600 mil)

- Cautions 1. (L) : Connect to Vss via individual pull-down resistors.

- 2. Vss : Connect to ground.

- 3. **RESET** : Set to low level.

- 4. Open : Do not connect.

| A0 - A14 | : | Address Bus   | RESET | : | Reset                    |

|----------|---|---------------|-------|---|--------------------------|

|          | : | Data Bus      | Vdd   | : | Power Supply             |

| CE       | : | Chip Enable   | Vpp   | : | Programming Power Supply |

| OE       | : | Output Enable | Vss   | : | Ground                   |

| PGM      | : | Program       |       |   |                          |

#### 44-pin plastic QFP (10 $\times$ 10 mm)

Cautions 1. (L) : Connect to Vss via individual pull-down resistors.

- 2. Vss : Connect to ground.

- 3. RESET : Set to low level.

- 4. Open : Do not connect.

| A0 - A14 | : | Address Bus   | RESET | : | Reset                    |

|----------|---|---------------|-------|---|--------------------------|

| D0 - D7  | : | Data Bus      | Vdd   | : | Power Supply             |

| CE       | : | Chip Enable   | Vpp   | : | Programming Power Supply |

| OE       | : | Output Enable | Vss   | : | Ground                   |

- : Output Enable OE

- PGM : Program

### NEC

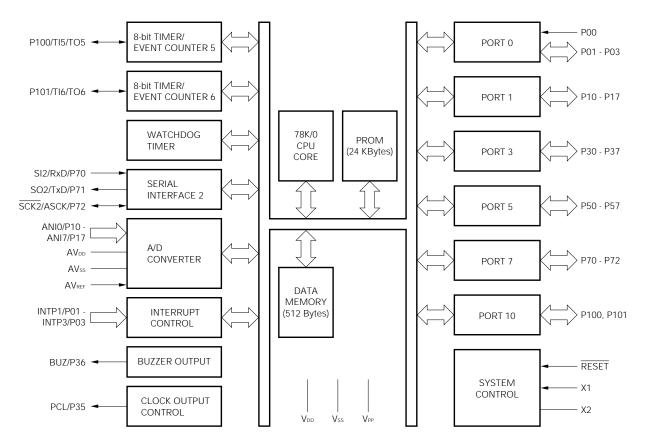

#### **Block Diagram**

#### CONTENTS

| 1. | DIFFERENCES BETWEEN $\mu$ PD78P083 AND MASK ROM VERSIONS                                                                                 | 10       |

|----|------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2. | LIST OF PIN FUNCTIONS2.1 Pins for Normal Operating Mode2.2 Pins for PROM Programming Mode2.3 Pin I/O Circuits and Unused Pin Connections | 11<br>13 |

| 3. | INTERNAL MEMORY SWITCHING (IMS) REGISTER                                                                                                 | 16       |

| 4. | PROM       PROGRAMMING         4.1       Operation Mode         4.2       PROM Write Procedure         4.3       PROM Read Procedure     | 17<br>19 |

| 5. | PROGRAM ERASURE (FOR $\mu$ PD78P083DU ONLY)                                                                                              | 24       |

| 6. | OPAQUE FILM ON ERASURE WINDOW (FOR $\mu\text{PD78P083DU}$ ONLY)                                                                          | 24       |

| 7. | SCREENING OF ONE-TIME PROM VERSIONS                                                                                                      | 24       |

| 8. | PACKAGE DRAWINGS                                                                                                                         | 25       |

| AP | PENDIX A. DEVELOPMENT TOOLS                                                                                                              | 28       |

| AP | PENDIX B. RELATED DOCUMENTS                                                                                                              | 32       |

#### 1. DIFFERENCES BETWEEN $\mu\text{PD78P083}$ and mask rom versions

The  $\mu$ PD78P083 has an on-chip 24-Kbyte one-time PROM or EPROM.

The internal memory switching register settings enable functions other than PROM specifications to be set as equivalent to those of mask ROM versions.

Table 1-1 lists the points of difference between the  $\mu$ PD78P083 and mask ROM versions.

#### Table 1-1. Differences between $\mu\text{PD78P083}$ and Mask ROM Versions

| ltem    | μPD78P083 | Mask ROM Versions |

|---------|-----------|-------------------|

| IC pin  | No        | Yes               |

| VPP pin | Yes       | No                |

- Cautions 1. In the μPD78P083, internal PROM and internal high-speed RAM capacity can be changed by using the internal memory switching register.

- 2. RESET input sets internal PROM to 24 Kbytes and internal high-speed RAM to 512 bytes.

#### 2. LIST OF PIN FUNCTIONS

#### 2.1 Pins for Normal Operating Mode

#### (1) Port pins

| Pin name  | I/O   |                                                                       | Function                                                                                         | After reset | Alternate function |

|-----------|-------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------|--------------------|

| P00       | Input | Port 0.                                                               | Input only                                                                                       |             | —                  |

| P01       | I/O   | 4-bit I/O port.                                                       | Can be specified for I/O in 1-bit units.                                                         | Input       | INTP1              |

| P02       | _     |                                                                       | If used as an input port, software pull-up                                                       |             | INTP2              |

| P03       | _     |                                                                       | resistor can be connected.                                                                       |             | INTP3              |

| P10 - P17 | I/O   | -                                                                     | ied for I/O in 1-bit units.<br>Input port, software pull-up resistor can be<br>e                 | Input       | ANIO - ANI7        |

| P30 - P34 | I/O   | Port 3.                                                               |                                                                                                  | Input       | _                  |

| P35       | -     | 8-bit I/O port.                                                       |                                                                                                  | -           | PCL                |

| P36       |       | •                                                                     | ied for I/O in 1-bit units.<br>nput port, software pull-up resistor can be                       |             | BUZ                |

| P37       |       | connected.                                                            |                                                                                                  |             | —                  |

| P50 - P57 | I/O   | Can be specif                                                         | rive up to 7 LEDs.<br>ied for I/O in 1-bit units.<br>nput port, software pull-up resistor can be | Input       | _                  |

| P70       | I/O   | Port 7.<br>3-bit I/O port.                                            |                                                                                                  |             | SI2/RxD            |

| P71       |       | Can be specif                                                         | ied for I/O in 1-bit units.                                                                      |             | SO2/TxD            |

| P72       |       | If used as an input port, software pull-up resistor can be connected. |                                                                                                  |             | SCK2/ASCK          |

| P100      | I/O   | Port 10.<br>2-bit I/O port.                                           | ind for $1/0$ in 1 bit units                                                                     | Input       | TI5/TO5            |

| P101      |       |                                                                       | ied for I/O in 1-bit units.<br>Input port, software pull-up resistor can be                      |             | TI6/TO6            |

**Note** When using P10/ANI0-P17/ANI7 pins as an analog input for an A/D converter, set port 1 to input mode. The pull-up resistors will automatically be disconnected.

#### (2) Non-port pins

| Pin name    | I/O    | Function                                                                                                        | After reset | Alternate function |

|-------------|--------|-----------------------------------------------------------------------------------------------------------------|-------------|--------------------|

| INTP1       | Input  | Can be set for effective edge (rising edge, falling edge,                                                       | Input       | P01                |

| INTP2       |        | or both rising and falling edges). Inputs specifiable                                                           |             | P02                |

| INTP3       |        | external interrupts.                                                                                            |             | P03                |

| SI2         | Input  | Input of serial data for serial interface.                                                                      | Input       | P70/RxD            |

| SO2         | Output | Output of serial data for serial interface.                                                                     | Input       | P71/TxD            |

| SCK2        | I/O    | Serial clock input/output for serial interface.                                                                 | Input       | P72/ASCK           |

| RxD         | Input  | Input of serial data for asynchronous serial interface.                                                         | Input       | P70/SI2            |

| TxD         | Output | Output of serial data for asynchronous serial interface.                                                        | Input       | P71/SO2            |

| ASCK        | Input  | Serial clock input for asynchronous serial interface.                                                           | Input       | P72/SCK2           |

| TI5         | Input  | External count clock input to 8-bit timer (TM5).                                                                | Input       | P100/TO5           |

| TI6         |        | External count clock input to 8-bit timer (TM6).                                                                | _           | P101/TO6           |

| TO5         | Output | 8-bit timer output.                                                                                             | Input       | P100/TI5           |

| TO6         |        |                                                                                                                 |             | P101/TI6           |

| PCL         | Output | Clock output (for trimming main system clock or sub system clock)                                               |             | P35                |

| BUZ         | Output | Buzzer output.                                                                                                  | Input       | P36                |

| ANIO - ANI7 | Input  | Analog input for A/D converter                                                                                  | Input       | P10 - P17          |

| AVREF       | Input  | Reference voltage input for A/D converter                                                                       | _           | _                  |

| AVdd        | _      | Analog power supply for A/D converter. Connect to VDD.                                                          | _           | _                  |

| AVss        | _      | Ground for A/D converter. Connect to Vss.                                                                       | _           | _                  |

| RESET       | Input  | System reset input.                                                                                             | _           | _                  |

| X1          | Input  | Crystal connection for main system clock oscillation.                                                           | _           | _                  |

| X2          | _      |                                                                                                                 | _           | _                  |

| Vdd         | —      | Positive power supply.                                                                                          | _           | _                  |

| Vpp         | _      | High-voltage power supply during program write/verify.<br>Connect directly to Vss during normal operation mode. | _           | _                  |

| Vss         | _      | Ground.                                                                                                         | _           | _                  |

| NC          | —      | No internal connection. Connect to Vss (may also be left open).                                                 | _           | _                  |

#### 2.2 Pins for PROM Programming Mode

| Pin name | I/O   | Function                                                                                                                                                                |  |

|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RESET    | Input | PROM programming mode selection.<br>PROM programming mode is selected when +5 V or +12.5 V is applied to the VPP pin or<br>low-level input is applied to the RESET pin. |  |

| Vpp      | Input | PROM programming mode selection and high-voltage input during program write or verification.                                                                            |  |

| A0 - A14 | Input | Address bus.                                                                                                                                                            |  |

| D0 - D7  | I/O   | Data bus.                                                                                                                                                               |  |

| CE       | Input | PROM enable input/program pulse input.                                                                                                                                  |  |

| OE       | Input | Read strobe input to PROM.                                                                                                                                              |  |

| PGM      | Input | Program/program inhibit input during PROM programming mode.                                                                                                             |  |

| Vdd      | _     | Positive power supply.                                                                                                                                                  |  |

| Vss      | _     | Ground.                                                                                                                                                                 |  |

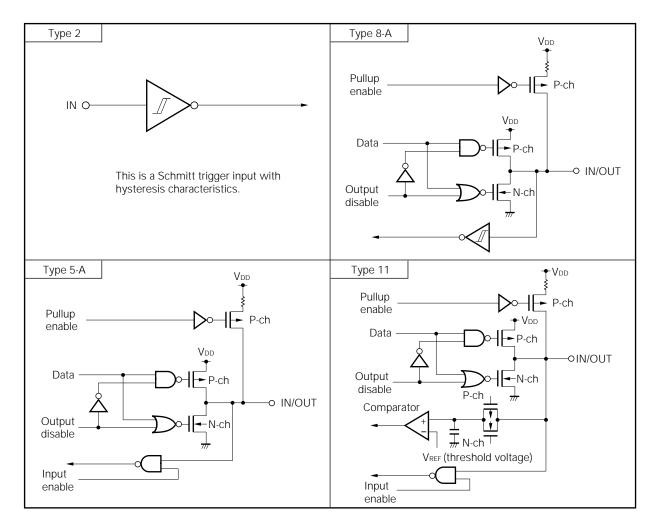

#### 2.3 Pin I/O Circuits and Unused Pin Connections

Table 2-1 lists the I/O circuit types for all pins and recommended connections for all unused pins. Figure 2-1 shows the pin I/O circuits.

| Pin name            | I/O circuit type | I/O   | Recommended connection for unused pins  |

|---------------------|------------------|-------|-----------------------------------------|

| P00                 | 2                | Input | Connect to Vss.                         |

| P01/INTP1           | 8-A              | I/O   | For input : Connect to Vss.             |

| P02/INTP2           |                  |       | For output: Open                        |

| P03/INTP3           |                  |       |                                         |

| P10/ANI0 - P17/ANI7 | 11               | I/O   | For input : Connect to VDD or Vss.      |

| P30 - P32           | 5-A              | I/O   | For output: Open                        |

| P33, P34            | 8-A              |       |                                         |

| P35/PCL             | 5-A              |       |                                         |

| P36/BUZ             |                  |       |                                         |

| P37                 |                  |       |                                         |

| P50 - P57           | 5-A              | I/O   | _                                       |

| P70/SI2/RxD         | 8-A              | I/O   | _                                       |

| P71/SO2/TxD         | 5-A              |       |                                         |

| P72/SCK2/ASCK       | 8-A              |       |                                         |

| P100/TI5/TO5        | 8-A              | I/O   | _                                       |

| P101/TI6/TO6        |                  |       |                                         |

| RESET               | 2                | Input | _                                       |

| AVREF               | _                | _     | Connect to Vss.                         |

| AVdd                |                  |       | Connect to VDD.                         |

| AVss                |                  |       | Connect to Vss.                         |

| Vpp                 |                  |       | Connect to Vss.                         |

| NC                  |                  |       | Connect to Vss. (can also be left open) |

Figure 2-1. Pin I/O Circuits

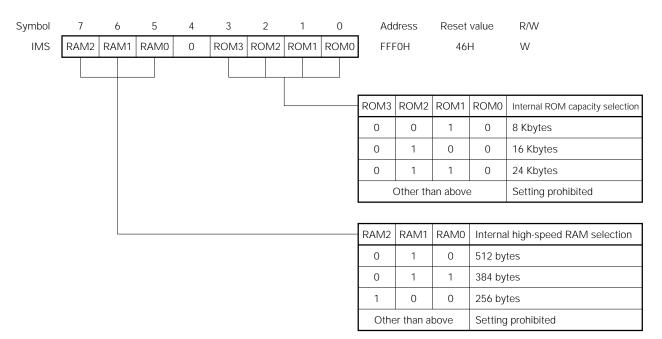

#### 3. INTERNAL MEMORY SWITCHING (IMS) REGISTER

This register enables the software to avoid using part of the internal memory. The IMS register can be set to establish the same memory mapping as used in ROM versions that have different internal memory (ROM and RAM) configurations.

The IMS register is set using 8-bit memory operation instructions.

RESET input sets a value of 46H.

Table 3-1 lists IMS register settings for memory mapping equivalent to mask ROM versions.

| Target mask ROM version | IMS setting |

|-------------------------|-------------|

| μPD78081                | 82H         |

| μPD78082                | 64H         |

#### 4. PROM PROGRAMMING

The  $\mu$ PD78P083 has an on-chip 24-Kbyte PROM device for use as program memory. When programming, set the VPP and RESET pins for PROM programming mode. See the pin configuration (Top View) under section "(2) PROM programming mode" with regard to recommended connections for unused pins.

# Caution Program write operations should take place in the address range 0000H to 5FFFH (i.e., specify 5FFFH as the end address). Write is not possible when using PROM programmers that do not enable write addresses to be set.

#### 4.1 Operation Mode

PROM programming mode is selected when +5 V or +12.5 V is applied to the VPP pin or low-level input is applied to the  $\overline{\text{RESET}}$  pin. This mode can be set to operation mode by setting the  $\overline{\text{CE}}$  pin,  $\overline{\text{OE}}$  pin, and  $\overline{\text{PGM}}$  pin as shown in Table 4-1 below.

In addition, the PROM contents can be read by setting read mode.

| Pin<br>Operation mode | RESET | Vpp     | Vdd    | CE | ŌĒ | PGM | D0-D7          |  |

|-----------------------|-------|---------|--------|----|----|-----|----------------|--|

| Page data latch       | L     | +12.5 V | +6.5 V | Н  | L  | Н   | Data input     |  |

| Page write            |       |         |        | Н  | н  | L   | High-impedance |  |

| Byte write            |       |         |        | L  | Н  | L   | Data input     |  |

| Program verify        |       |         |        | L  | L  | Н   | Data output    |  |

| Program inhibit       |       |         |        | ×  | Н  | н   | High-impedance |  |

|                       |       |         |        | ×  | L  | L   |                |  |

| Read                  |       | +5 V    | +5 V   | L  | L  | Н   | Data output    |  |

| Output disable        |       |         |        | L  | Н  | ×   | High-impedance |  |

| Standby               |       |         |        | Н  | ×  | ×   | High-impedance |  |

#### Table 4-1. PROM Programming Operation Mode

**Remark**  $\times$  = L or H

#### (1) Read mode

Set  $\overline{CE}$  to L and  $\overline{OE}$  to L to set read mode.

#### (2) Output disable mode

Set  $\overline{OE}$  to H to set high impedance for data output and output disable mode. Consequently, if several µPD78P083 devices are connected to a data bus, the  $\overline{OE}$  pins can be controlled to read data from any one of the devices.

#### (3) Standby mode

Set  $\overline{CE}$  to H to set standby mode. In this mode, data output is set to high impedance regardless of the  $\overline{OE}$  setting.

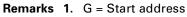

#### (4) Page data latch mode

At the beginning of page write mode, set  $\overline{CE}$  to H,  $\overline{PGM}$  to H, and  $\overline{OE}$  to L to set page data latch mode. In this mode, 1 page (4 bytes) of data are latched to the internal address/data latch circuit.

#### (5) Page write mode

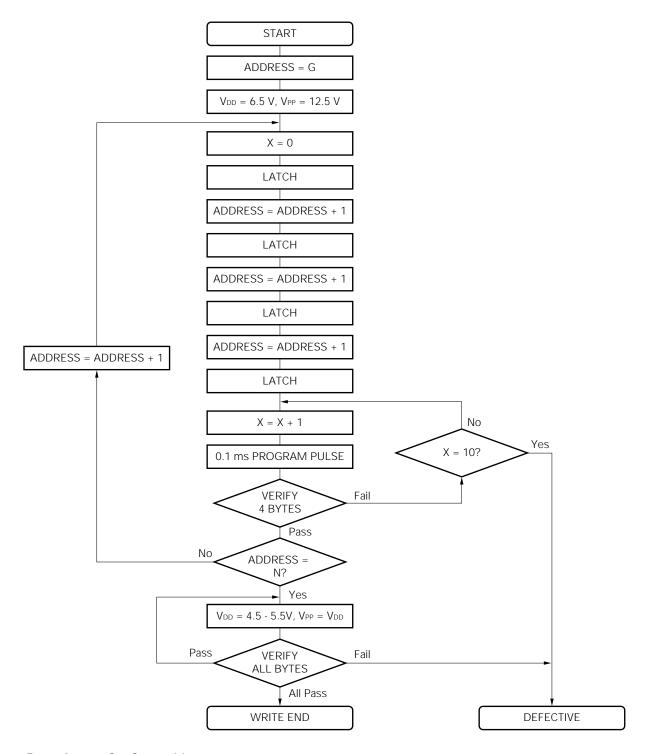

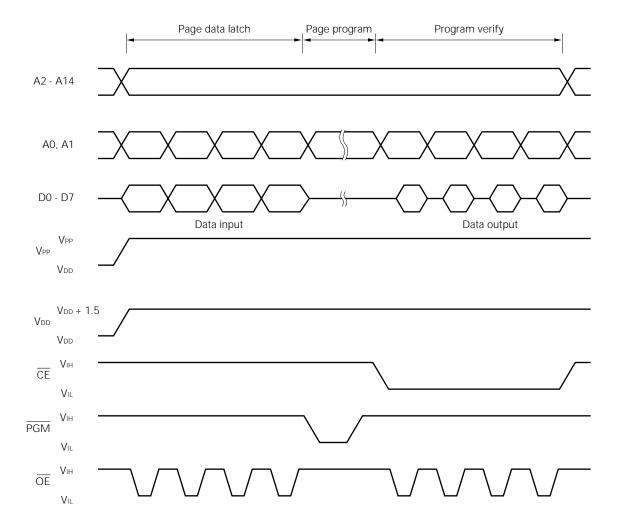

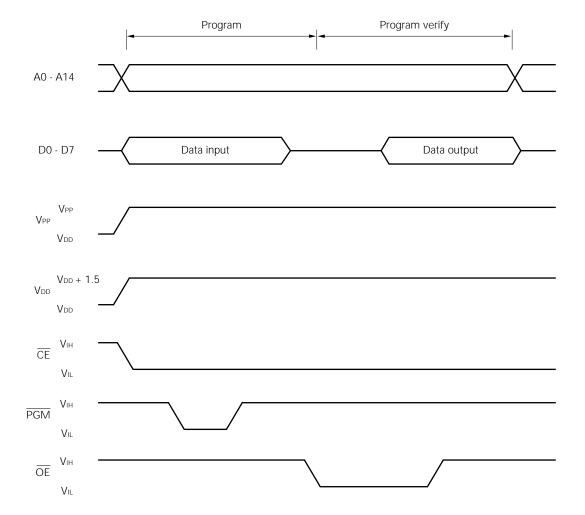

After latching the address and data for one page (4 bytes) using page latch mode, execute page write by providing a 0.1-ms program pulse (active low) to the  $\overrightarrow{PGM}$  pin with both  $\overrightarrow{CE}$  and  $\overrightarrow{OE}$  set to H. Next, execute program verification by setting both  $\overrightarrow{CE}$  and  $\overrightarrow{OE}$  to L.

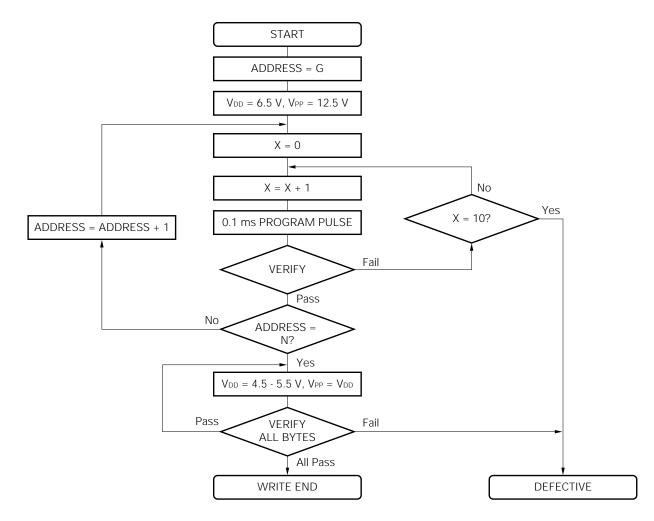

If programming is not completed after one program pulse, the write and verify operations may be repeated X times (where X - 10).

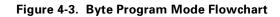

#### (6) Byte write mode

Provide a 0.1-ms program pulse (active low) to the  $\overline{PGM}$  terminal with both  $\overline{CE}$  and  $\overline{OE}$  set to H to execute page write. Next, execute program verification by setting  $\overline{OE}$  to L.

If programming is not completed after one program pulse, the write and verify operations may be repeated X times (where X - 10).

#### (7) Program verify mode

Set  $\overline{CE}$  to L,  $\overline{PGM}$  to H, and  $\overline{OE}$  to L to set program verify mode. Use verify mode for verification following each write operation.

#### (8) Program inhibit mode

Program inhibit mode is used to write to a single device when  $\overline{OE}$ , VPP, and D0 to D7 pins of several  $\mu$ PD78P083 devices are connected in parallel.

Use the page write mode or byte write mode described above for each write operation. Write operations cannot be done for devices in which the  $\overline{PGM}$  pin has been set to H.

#### 4.2 PROM Write Procedure

Figure 4-1. Page Program Mode Flowchart

2. N = Program end address

Figure 4-2. Page Program Mode Timing

Remarks 1. G = Start address

2. N = Program end address

Figure 4-4. Byte Program Mode Timing

- Cautions 1. VDD must be supplied before applying VPP, it should be removed after removing VPP.

- 2. VPP must not exceed +13.5V, including overshoot.

- 3. Reliability problems or other adverse effects may result if VPP is removed while applying +12.5 V.

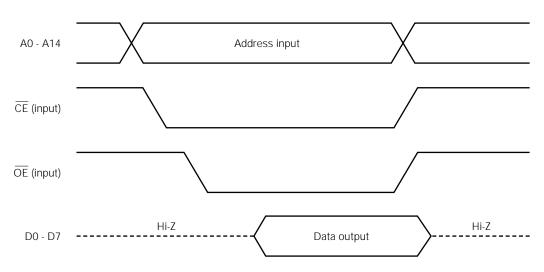

#### 4.3 PROM Read Procedure

Follow this procedure to read the PROM contents to an external data bus (D0 to D7).

- (1) Set the RESET pin to low level and supply +5 V to the VPP pin. Refer to the pin configuration (Top View) under section "(2) PROM programming mode" for connections of other unused pins.

- (2) Supply +5V to the VDD and VPP pins.

- (3) Input the address of the data to be read to pins A0 to A14.

- (4) Set read mode.

- (5) Data is output to pins D0 to D7.

Figure 4-5 shows the timing of steps (2) to (5) above.

#### Figure 4-5. PROM Read Timing

#### 5. PROGRAM ERASURE (FOR µPD78P083DU ONLY)

In the  $\mu$ PD78P083DU it is possible to erase (FFH) data that has been written to program memory and to write new data.

Erasure is made by exposing the window to light having a very short wavelength of shorter than 400 nm. The program memory contents are usually erased by ultraviolet rays having a wavelength of 254 nm. The amount of exposing needed to completely erase the programmed data is shown below.

- Ultraviolet ray strength × erasure time: 15 W•s/cm<sup>2</sup> or more

- Erasure time: 15 to 20 minutes (when using a 12,000  $\mu$ W/cm<sup>2</sup> ultraviolet lamp. However, the required erasure time may be longer in some cases, such as when there has been deterioration of ultraviolet lamp performance or when the erasure window is dirty.)

When erasing, place the ultraviolet lamp within 2.5 cm of the erasure window. If a filter has been attached to the ultraviolet lamp, remove the filter before erasing.

#### 6. OPAQUE FILM ON ERASURE WINDOW (FOR $\mu$ PD78P083DU ONLY)

Except when erasing EPROM contents, be sure to leave the opaque film on the erasure window to prevent unintentional erasure of EPROM contents from light sources other than the ultraviolet lamp and to prevent light sources from inadvertently affecting internal circuits other than the EPROM.

#### 7. SCREENING OF ONE-TIME PROM VERSIONS

Due to the structure of the one-time PROM ( $\mu$ PD78P083CU or 78P083GB-3B4), it is impossible to fully test the device prior to shipment. It is therefore recommended that the device be stored in high temperature conditions shown below, followed by screening to verify the PROM after writing the required data.

| Storagetemperature | Storage time |  |  |

|--------------------|--------------|--|--|

| 125½C              | 24 hours     |  |  |

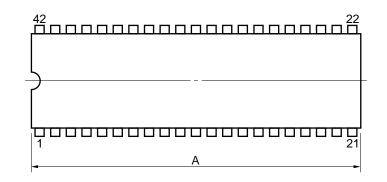

8. PACKAGE DRAWINGS

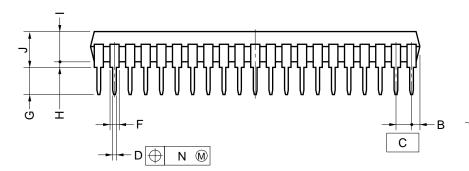

#### 42PIN PLASTIC SHRINK DIP (600 mil)

#### NOTES

1) Each lead centerline is located within 0.17 mm (0.007 inch) of its true position (T.P.) at maximum material condition.

2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| А    | 39.13 MAX.             | 1.541 MAX.                |

| В    | 1.78 MAX.              | 0.070 MAX.                |

| С    | 1.778 (T.P.)           | 0.070 (T.P.)              |

| D    | 0.50±0.10              | $0.020^{+0.004}_{-0.005}$ |

| F    | 0.9 MIN.               | 0.035 MIN.                |

| G    | 3.2±0.3                | 0.126±0.012               |

| Н    | 0.51 MIN.              | 0.020 MIN.                |

| I    | 4.31 MAX.              | 0.170 MAX.                |

| J    | 5.08 MAX.              | 0.200 MAX.                |

| К    | 15.24 (T.P.)           | 0.600 (T.P.)              |

| L    | 13.2                   | 0.520                     |

| М    | $0.25^{+0.10}_{-0.05}$ | $0.010^{+0.004}_{-0.003}$ |

| N    | 0.17                   | 0.007                     |

| R    | 0~15°                  | 0~15°                     |

|      |                        | P42C-70-600A-1            |

42-pin ceramic shrink DIP (with window) (600 mil)

# T.B.D.

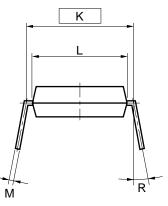

#### 44 PIN PLASTIC QFP (□10)

#### ΝΟΤΕ

Each lead centerline is located within 0.15 mm (0.006 inch) of its true position (T.P.) at maximum material condition.

|      |                                 | P44GB-80-3B4-2                            |  |

|------|---------------------------------|-------------------------------------------|--|

| ITEM | MILLIMETERS                     | INCHES                                    |  |

| А    | 13.6±0.4                        | $0.535\substack{+0.017\\-0.016}$          |  |

| В    | 10.0±0.2                        | $0.394^{+0.008}_{-0.009}$                 |  |

| С    | 10.0±0.2                        | 0.394 <sup>+0.008</sup> 0.009             |  |

| D    | 13.6±0.4                        | $0.535\substack{+0.017\\-0.016}$          |  |

| F    | 1.0                             | 0.039                                     |  |

| G    | 1.0                             | 0.039                                     |  |

| Н    | 0.35±0.10                       | $0.014^{+0.004}_{-0.005}$                 |  |

| I    | 0.15                            | 0.006                                     |  |

| J    | 0.8 (T.P.)                      | 0.031 (T.P.)                              |  |

| К    | 1.8±0.2                         | 0.071 <sup>+0.008</sup> <sub>-0.009</sub> |  |

| L    | 0.8±0.2                         | 0.031+0.009                               |  |

| М    | $0.15\substack{+0.10 \\ -0.05}$ | 0.006 <sup>+0.004</sup> 0.003             |  |

| Ν    | 0.12                            | 0.005                                     |  |

| Р    | 2.7                             | 0.106                                     |  |

| Q    | 0.1±0.1                         | 0.004±0.004                               |  |

| S    | 3.0 MAX.                        | 0.119 MAX.                                |  |

#### APPENDIX A. DEVELOPMENT TOOLS

The following development tools are available for system development using the µPD78P083.

#### Language processing software

| RA78K/0 Notes 1, 2, and 3   | Assembler package for 78K/0 Series              |

|-----------------------------|-------------------------------------------------|

| CC78K/0 Notes 1, 2, and 3   | C compiler package for 78K/0 Series             |

| DF78083 Notes 1, 2, 3 and 6 | Device file for μPD78083 Subseries              |

| CC78K/0-L Notes 1, 2, and 3 | C compiler library source file for 78K/0 Series |

#### PROM write tools

| PG-1500                          | PROM programmer                         |  |

|----------------------------------|-----------------------------------------|--|

| PA-78P083CU Note 6               | Programmer adapter, connects to PG-1500 |  |

| PA-78P083GB Note 6               |                                         |  |

| PG-1500 controller Notes 1 and 2 | Control program for PG-1500             |  |

#### **Debugging tools**

| IE-78000-R                         | In-circuit emulator for 78K/0 Series                                 |

|------------------------------------|----------------------------------------------------------------------|

| IE-78000-R-BK                      | Break board for 78K/0 Series                                         |

| IE-78078-R-EM Note 6               | Emulation board for µPD78078 Subseries                               |

| EP-78083CU-R <sup>Note 6</sup>     | Emulation probe for µPD78083 Subseries                               |

| EP-78083GB-R Note 6                |                                                                      |

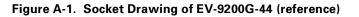

| EV-9200G-44                        | Socket for mounting on user system board made for 44-pin plastic QFP |

| SD78K/0 Notes 1 and 2              | Screen debugger for IE-78000-R                                       |

| SM78K/0 Notes 3, 4, 5, and 6       | System simulator for 78K/0 Series                                    |

| DF78083 Notes 1, 2, 3, 4, 5, and 6 | Device file for µPD78083 Subseries                                   |

#### Fuzzy inference development support systems

| FE9000 Note 1/FE9200 Note 5 | Fuzzy knowledge data generation tool |  |

|-----------------------------|--------------------------------------|--|

| FT9080 Note 1/FT9085 Note 2 | Translator                           |  |

| FI78K0 Notes 1 and 2        | Fuzzy inference module               |  |

| FD78K0 Notes 1 and 2        | Fuzzy inference debugger             |  |

Notes 1. Based on PC-9800 Series (running MS-DOS™)

- 2. Based on IBM PC/AT<sup>™</sup> (running PC-DOS<sup>™</sup>)

- **3.** Based on HP9000 Series 300<sup>™</sup> and Series 700<sup>™</sup> (running HP-UX<sup>™</sup>), SPARCstation<sup>™</sup> (running Sun OS<sup>™</sup>), and EWS-4800 Series (running EWS-UX/V).

- 4. Based on PC-9800 Series (running MS-DOS + Windows™)

- **5**. Based on IBM PC/AT (running PC-DOS + Windows)

- 6. Currently under development

Remark The RA78K/0, CC78K/0, SD78K/0, or SM78K/0 can be used in combination with the DF78083.

#### **Development Tools by Third-party Manufacturers**

| Company                                                      | Emulator             | Assembler             | C Compiler                              | Simulator             | Debugger              |

|--------------------------------------------------------------|----------------------|-----------------------|-----------------------------------------|-----------------------|-----------------------|

| Advanced Data Controls Co., Ltd.<br>(TEL: 03-3576-5351)      | _                    | Note                  | Available<br>(C cross 78K0<br>compiler) | Available<br>(CXDB/S) | Available<br>(CSDB/E) |

| Gaio Technology Co., Ltd.<br>(TEL: 03-3662-3041)             | _                    | Available<br>(XASS-V) | _                                       | Available<br>(XDEB-V) | Available<br>(XDDI-V) |

| Lifeboat, Inc.<br>(TEL: 03-3293-4714)                        | _                    | _                     | Note<br>(ICC78000)                      | _                     | _                     |

| Yokogawa Digital Computer Corporation<br>(TEL: 0422-56-9101) | Available<br>(AD200) | _                     | _                                       |                       | Available<br>(μVIEW)  |

**Note** Assemblers are bundled with C compiler packages.

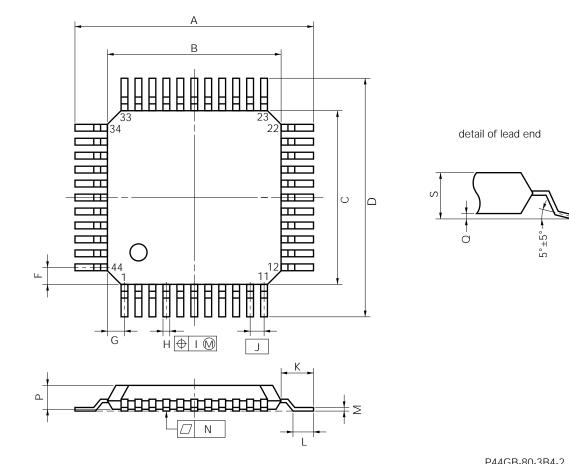

#### Drawing of conversion socket (EV-9200G-44) and footprint

| M |   |   |

|---|---|---|

| N | 0 |   |

|   | a | _ |

|   |   |   |

| ITEM | MILLIMETERS  | EV-9200G-44-G0            |

|------|--------------|---------------------------|

| A    | 15.0         | 0.591                     |

| В    | 10.3         | 0.406                     |

| С    | 10.3         | 0.406                     |

| D    | 15.0         | 0.591                     |

| E    | 4-C 3.0      | 4-C 0.118                 |

| F    | 0.8          | 0.031                     |

| G    | 5.0          | 0.197                     |

| Н    | 12.0         | 0.472                     |

| I    | 14.7         | 0.579                     |

| J    | 5.0          | 0.197                     |

| К    | 12.0         | 0.472                     |

| L    | 14.7         | 0.579                     |

| Μ    | 8.0          | 0.315                     |

| 0    | 7.8          | 0.307                     |

| Ν    | 2.0          | 0.079                     |

| Р    | 1.35         | 0.053                     |

| Q    | 0.35±0.1     | $0.014^{+0.004}_{-0.005}$ |

| R    | <b>ø</b> 1.5 | ø0.059                    |

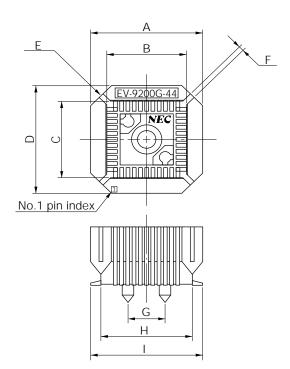

#### Figure A-2. Footprint for EV-9200G-44 (reference)

| ITEM | MILLIMETERS                       | INCHES                                                             |

|------|-----------------------------------|--------------------------------------------------------------------|

| A    | 15.7                              | 0.618                                                              |

| В    | 11.0                              | 0.433                                                              |

| С    | 0.8±0.02×10=8.0±0.05              | $0.031^{+0.002}_{-0.001} \times 0.394 {=} 0.315^{+0.002}_{-0.002}$ |

| D    | $0.8\pm0.02 \times 10=8.0\pm0.05$ | $0.031^{+0.002}_{-0.001} \times 0.394 {=} 0.315^{+0.002}_{-0.002}$ |

| E    | 11.0                              | 0.433                                                              |

| F    | 15.7                              | 0.618                                                              |

| G    | 5.00±0.08                         | $0.197^{+0.003}_{-0.004}$                                          |

| Н    | 5.00±0.08                         | $0.197^{+0.003}_{-0.004}$                                          |

| I    | 0.5±0.02                          | 0.02 <sup>+0.001</sup> <sub>-0.002</sub>                           |

| J    | Ø1.57±0.03                        | Ø0.062 <sup>+0.001</sup><br>-0.002                                 |

| К    | Ø2.2±0.1                          | Ø0.087 <sup>+0.004</sup><br>-0.005                                 |

| L    | Ø1.57±0.03                        | Ø0.062 <sup>+0.001</sup><br>-0.002                                 |

Caution Dimensions of mount pad for EV-9200 and that for target device (QFP) may be different in some parts. For the recommended mount pad dimensions for QFP, refer to "SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL" (IEI-1207).

#### APPENDIX B. RELATED DOCUMENTS

#### **Device-related documents**

| Document name                                                     | Document No.     |                 |

|-------------------------------------------------------------------|------------------|-----------------|

|                                                                   | Japanese version | English version |

| μPD78083 Subseries User's Manual                                  | IEU-886          | _               |

| 78K/0 Series User's Manual: Instructions                          | IEU-849          | IEU-1372        |

| 78K/0 Series Instruction Use Manual                               | IEM-5522         | _               |

| 78K/0 Series Instruction Set                                      | IEM-5521         | —               |

| $\mu$ PD78083 Subseries Special Function Register Reference Table | IEM-5599         | _               |

#### Development tool-related documents (user's manuals)

| Document name                                  |                    | Document No.     |                 |

|------------------------------------------------|--------------------|------------------|-----------------|

|                                                |                    | Japanese version | English version |

| RA78K Series Assembler Package                 | Operation manual   | EEU-809          | EEU-1399        |

|                                                | Source code manual | EEU-815          | EEU-1404        |

| RA78K Series Structured Assembler Preprocessor |                    | EEU-817          | EEU-1402        |

| CC78K Series C Compiler                        | Operation manual   | EEU-656          | EEU-1280        |

|                                                | Source code manual | EEU-655          | EEU-1284        |

| CC78K Series Library Source File               |                    | EEU-777          | _               |

| PG-1500 PROM Programmer                        |                    | EEU-651          | EEU-1335        |

| PG-1500 Controller                             |                    | EEU-704          | EEU-1291        |

| IE-78000-R                                     |                    | EEU-810          | EEU-1398        |

| IE-78000-R-BK                                  |                    | EEU-867          | EEU-1427        |

| IE-78078-R-EM                                  |                    | EEU-978          | _               |

| SD78K/0 Screen Debugger                        | Introduction       | EEU-852          | EEU-1414        |

|                                                | Reference manual   | EEU-816          | EEU-1413        |

#### Related documents (user's manuals) for embedded software

| Document name                                                                        | Document No.     |                 |

|--------------------------------------------------------------------------------------|------------------|-----------------|

|                                                                                      | Japanese version | English version |

| Fuzzy knowledge data generation tool                                                 | EEU-829          | EEU-1438        |

| 78K/0, 78K/II, 87AD Series Fuzzy Inference Development<br>Support System: Translator | EEU-862          | EEU-1444        |

| 78K/0 Series Fuzzy Inference Development Support System:<br>Fuzzy Inference Module   | EEU-858          | _               |

| 78K/0 Series Fuzzy Inference Development Support System:<br>Fuzzy Inference Debugger | EEU-921          | _               |

## Caution The contents of the above documents are subject to change without prior notice. Be sure to use the latest edition for purposes such as design work.

#### Other related documents

| Document name                                                         | Document No.     |                 |

|-----------------------------------------------------------------------|------------------|-----------------|

|                                                                       | Japanese version | English version |

| Package manual                                                        | IEI-635          | IEI-1213        |

| Semiconductor Device Mounting Manual                                  | IEI-616          | IEI-1207        |

| NEC Semiconductor Device Quality Grades                               | IEI-620          | IEI-1209        |

| NEC Semiconductor Device Reliability and Quality Control              | IEM-5068         | _               |

| Electrostatic Discharge (ESD) Tests                                   | MEM-539          | —               |

| Semiconductor Device Quality Assurance Guide                          | MEI-603          | MEI-1202        |

| Microcomputer-related Product Guide (Products by other Manufacturers) | MEI-604          | _               |

Caution The contents of the above documents are subject to change without prior notice. Be sure to use the latest edition for purposes such as design work.

[MEMO]

#### NOTES FOR CMOS DEVICES -

#### **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note: Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### **(2)** HANDLING OF UNUSED INPUT PINS FOR CMOS

Note: No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note: Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function. The related document in this publication may include preliminary versions. However, preliminary versions are not marked as such.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

The devices listed in this document are not suitable for use in aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. If customers intend to use NEC devices for above applications or they intend to use "Standard" quality grade NEC devices for applications not intended by NEC, please contact our sales people in advance.

Application examples recommended by NEC Corporation

Standard: Computer, Office equipment, Communication equipment, Test and Measurement equipment, Machine tools, Industrial robots, Audio and Visual equipment, Other consumer products, etc.

Special: Automotive and Transportation equipment, Traffic control systems, Antidisaster systems, Anticrime systems, etc.

M4 92.6

FIP is a trademark of NEC Corporation.

IEBus is a trademark of NEC Corporation.

MS-DOS and Windows are trademarks of Microsoft Corporation.

PC/AT and PC-DOS are trademarks of IBM Corporation.

HP9000 Series 300, HP9000 Series 700, and HP-UX are trademarks of Hewlett-Packard, Inc.

SPARCstation is a trademark of SPARC International, Inc.

SunOS is a trademark of Sun Microsystems, Inc.