# VadaTech AMC511

# User's Manual

May 14, 2010 Version 1.2.0

Copyright © 2010 VadaTech Incorporated All rights reserved VadaTech and the globe image are trademarks of VadaTech Incorporated. All other product or service names mentioned in this document are the property of their respective owners.

#### Notice

While reasonable efforts have been made to assure the accuracy of this document, VadaTech, Inc. assumes no liability resulting from any omissions in this document or from the use of the information obtained herein. VadaTech reserves the right to revise this document and to make changes periodically and the content hereof without obligation of VadaTech to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to the VadaTech Incorporated Web site. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of VadaTech, Inc.

It is possible that this publication may contain reference to or information about VadaTech products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that VadaTech intends to announce such products, programming, or services in your country.

#### Trademarks

The VadaTech, Inc name and logo are registered trademarks of VadaTech Incorporated in the U.S.A. All other product or service names mentioned in this document are the property of their respective owners.

© 2010, VadaTech Incorporated. Printed in the U.S.A., All Rights Reserved.

# Revision History

| Doc<br>Rev | Description of Change                                                                                                                           | Revision Date |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|

| 1.0.0      | Document Created                                                                                                                                | 6/8/2009      |  |  |

| 1.1.0      | Updated with latest board and reference design information                                                                                      | 2/10/2010     |  |  |

| 1.1.1      | Changed the reference design's PCIe width to x4 instead of x8 to more closely match the initial customer's configuration.                       | 3/10/2010     |  |  |

| 1.2.0      | Added discussion of how to set up the reference design FPGA 5/14/201<br>and software code for different available VCXO / Ref Clock frequencies. |               |  |  |

# Table of Contents

| 1 | Ove  | rview | l                                         | 8  |

|---|------|-------|-------------------------------------------|----|

|   | 1.1  | Арр   | licable Products                          | 8  |

|   | 1.2  |       | ument References                          |    |

|   | 1.3  | Acro  | onyms Used in this Document               | 9  |

| 2 | Hard | dwar  | e Overview                                | 10 |

|   | 2.1  | Bac   | kplane SERDES Interfaces                  | 11 |

|   | 2.2  | AMC   | C Card-edge Pin-out                       | 13 |

|   | 2.3  | Fror  | nt Panel Interfaces                       | 14 |

|   | 2.3. | 1     | Front Panel Management Interfaces         | 15 |

|   | 2.3. | 2     | Front Panel A/D Inputs                    | 15 |

|   | 2.3. | 3     | Front Panel Synchronization Interfaces    | 15 |

|   | 2.3. | 4     | Front Panel Channel Status LEDs           | 16 |

|   | 2.4  | Swit  | tches / Jumpers / Headers                 | 17 |

| 3 | Refe |       | ce FPGA Design Overview                   |    |

|   | 3.1  | PCIe  | e Bridge w/ DMA Burst Engine              | 21 |

|   | 3.2  |       | A Burst Arbiter                           |    |

|   | 3.3  |       | Controller w/ DMA Burst Scheduler         | 21 |

|   | 3.3. |       | Capture Stage                             |    |

|   | 3.3. |       | Formatting Stage                          |    |

|   | 3.3. |       | Pattern Generation Stage                  |    |

|   | 3.3. |       | Half-Band FIR Low-Pass Filter Stage       |    |

|   | 3.3. |       | Decimation Stage                          |    |

|   | 3.3. |       | Packing Stage                             |    |

|   | 3.3. |       | FIFO Stage                                |    |

|   | 3.3. |       | DMA Burst Scheduler                       |    |

|   | 3.4  |       | rrupt Controller                          |    |

|   | 3.5  |       | k Synchronizer Controller                 |    |

|   | 3.5. |       | SPI Master                                |    |

|   | 3.6  |       | ck/Signal Router                          |    |

|   | 3.7  |       | Controller                                |    |

|   | 3.8  |       | Flash Controller                          |    |

|   | 3.9  |       | ty Functions                              |    |

| 4 |      |       | ce Software Overview                      |    |

|   | 4.1  |       | C511 Device Driver                        |    |

|   | 4.2  |       | C511 Tool Application                     |    |

| 5 | 2    |       | Performance Considerations                |    |

|   | 5.1  |       | ware Optimization Tips                    |    |

| 6 |      |       | stomization                               |    |

| 7 |      |       | zing the VCXO / Ref Clock Configuration   |    |

| 8 |      |       | A: FPGA Register Specification            |    |

|   | 8.1  |       | SR – Global Interrupt Mask Set Register   |    |

|   | 8.2  | GIM   | CR – Global Interrupt Mask Clear Register | 40 |

|   | 8.3               | GISR – Global Interrupt Status Register                                                                                 | 41                         |

|---|-------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   | 8.4               | BCSR – Bit Change Status Register                                                                                       | 42                         |

|   | 8.5               | CHCTRLx - Channel X Control Register                                                                                    | 43                         |

|   | 8.6               | CHSTATx – Channel X Status Register                                                                                     | 44                         |

|   | 8.7               | CHMASKx – Channel X Mask Register                                                                                       | 45                         |

|   | 8.8               | CHHWMx – Channel X High Water Mark Register                                                                             | 46                         |

|   | 8.9               | CHLVLx – Channel X Level Register                                                                                       |                            |

|   | 8.10              | CHDMACTRLx – Channel X DMA Control/Status Register                                                                      | 48                         |

|   | 8.11              | CHDMACOUNTx – Channel X DMA Count Register                                                                              | 50                         |

|   | 8.12              | CHDEBUGAx – Channel X Debug A Register                                                                                  | 51                         |

|   | 8.13              | CHDEBUGBx – Channel X Debug B Register                                                                                  | 52                         |

|   | 8.14              | CHDEBUGCx – Channel X Debug C Register                                                                                  | 54                         |

|   | 8.15              | CHFIFOx – Channel X FIFO Read Port                                                                                      |                            |

|   | 8.16              | CHDMADESCx – Channel X DMA Descriptors Port                                                                             |                            |

|   | 8.17              | SYNCCTRL – Clock Synchronizer Control/Status Register                                                                   |                            |

|   | 8.18              | SYNCSPIO – Clock Synchronizer SPI Data 0 Register                                                                       |                            |

|   | 8.19              | SYNCSPI1 – Clock Synchronizer SPI Data 1 Register                                                                       |                            |

|   | 8.20              | SYNCSPI2 – Clock Synchronizer SPI Data 2 Register                                                                       |                            |

|   | 8.21              | SYNCSPI3 – Clock Synchronizer SPI Data 3 Register                                                                       |                            |

|   | 8.22              | CRSYNC, CRTCLKA/B/C/D, CRTRIGINx, CRPRIREF, CRSECREF -                                                                  | Clock Routing              |

|   | Regist            | ers64                                                                                                                   |                            |

|   | 8.23              | CREN – Clock Routing Enable Register                                                                                    |                            |

|   | 8.24              | GREENLEDx – Green Status LED Control Registers                                                                          |                            |

|   | 8.25              | AMBERLEDx – Amber Status LED Control Registers                                                                          |                            |

|   | 8.26              | ARBSTAT – DMA Arbiter Status Register                                                                                   |                            |

|   | 8.27              | BPICTRL – BPI Flash Control Register                                                                                    |                            |

|   | 8.28              | BPIADDR – BPI Flash Address Register                                                                                    |                            |

|   | 8.29              | BPIDATA – BPI Flash Data Register                                                                                       |                            |

|   | 8.30              | SCRATCH – Scratch Register                                                                                              |                            |

|   | 8.31              | VER – Version Register                                                                                                  |                            |

| _ | 8.32              | SIG – Signature Register                                                                                                |                            |

| 9 |                   | endix B: Device Driver IOCTL Specification                                                                              |                            |

|   | 9.1               | AMC511_IOC_GET_INFO                                                                                                     |                            |

|   | 9.2               | AMC511_IOC_GET/SET_LEDS                                                                                                 |                            |

|   | 9.3               | AMC511_IOC_GET/SET_CLOCK_ROUTING                                                                                        |                            |

|   | 9.4               |                                                                                                                         |                            |

|   |                   | AMC511_IOC_GET/SET_CLOCK_SYNC                                                                                           | 77                         |

|   | 9.5               | AMC511_IOC_GET/SET_CLOCK_SYNC<br>AMC511_IOC_GET/SET_CHAN_CTRL                                                           | 77<br>79                   |

|   | 9.5<br>9.6        | AMC511_IOC_GET/SET_CLOCK_SYNC<br>AMC511_IOC_GET/SET_CHAN_CTRL<br>AMC511_IOC_GET_CHAN_STATUS                             | 77<br>79<br>79             |

|   | 9.5<br>9.6<br>9.7 | AMC511_IOC_GET/SET_CLOCK_SYNC<br>AMC511_IOC_GET/SET_CHAN_CTRL<br>AMC511_IOC_GET_CHAN_STATUS<br>AMC511_IOC_GET_CHAN_DATA | 77<br>79<br>79<br>80       |

|   | 9.5<br>9.6        | AMC511_IOC_GET/SET_CLOCK_SYNC<br>AMC511_IOC_GET/SET_CHAN_CTRL<br>AMC511_IOC_GET_CHAN_STATUS                             | 77<br>79<br>79<br>80<br>80 |

# Figures

| Figure 1: AMC511 top-side layout                   | 10 |

|----------------------------------------------------|----|

| Figure 2: AMC511 block diagram                     |    |

| Figure 3: Virtex 5 GTP clock forwarding for AMC511 |    |

| Figure 4: AMC511 front panel                       |    |

| Figure 5: ADC pipeline                             |    |

| Figure 6: Half-band FIR filter response            |    |

# Tables

| Table 1: Acronyms                                | 9  |

|--------------------------------------------------|----|

| Table 2: Possible packplane SERDES interfaces    | 11 |

| Table 3: AMC card-edge pin-out                   | 13 |

| Table 4: AMC LED behavior                        | 15 |

| Table 5: STATUS LEDs power-on behavior           | 16 |

| Table 6: STATUS LEDs normal run-time behavior    | 16 |

| Table 7: SW2-3 JTAG routing selection            | 17 |

| Table 8: SW2-4 BPI Flash write protection        | 17 |

| Table 9: JP1 and JP2 optional input termination  |    |

| Table 10: J4 pin-out                             | 18 |

| Table 11: PCle configuration                     |    |

| Table 12: Supported VCXO / Ref Clock frequencies |    |

| Table 13: FPGA register map                      |    |

| <b>o</b> ,                                       |    |

# Overview

This document describes the AMC511 board and the A/D FPGA Reference Design including the associated software tool and driver. It also describes how to go about customizing the FPGA design for customer specific needs such as adding additional DSP into the FPGA. The FPGA and software are suitable for use as-is for some customer applications or may be customized by the customer to meet their own performance and functional requirements as needed.

### 1.1 Applicable Products

- VadaTech AMC511

- Related product: VadaTech AMC510

### 1.2 Document References

- Linear Technology LTC2209 16-bit, 160Msps ADC Datasheet

- <u>Texas Instruments CDCM7005 3.3-V High Performance Clock Synchronizer and Jitter</u> <u>Cleaner Datasheet</u>

- Xilinx Virtex-5 User's Guide (UG190)

- Xilinx Solutions Guide for PCI Express User Guide (UG493)

- Xilinx LogiCORE<sup>™</sup> Endpoint Block Plus v1.9 for PCI Express (DS551)

- Xilinx LogiCORE™ IP Endpoint Block Plus v1.9 for PCI Express® Getting Started Guide (UG343)

- Xilinx LogiCORE™ IP Endpoint Block Plus v1.9 for PCI Express® User Guide (UG341)

- Xilinx Virtex-5 Integrated Endpoint Block for PCI Express Designs User Guide (UG197)

- <u>Xilinx Virtex-5 Embedded Tri-Mode Ethernet MAC Wrapper 1.6 (DS550)</u>

- Xilinx Virtex-5 Embedded Tri-Mode Ethernet MAC User Guide (UG194)

- PICMG® AMC.0 R2.0 Advanced Mezzanine Card Base Specification

NOTE: When reading the Linear Tech datasheet keep in mind that the AMC511 uses screened parts from Linear Tech running at 180 Msps so the stated maximum of 160 Msps in the datasheet should be read as 180 Msps. The increased clock rate does not otherwise change the performance specifications of the chips, but provides improved oversampling performance in downstream DSP algorithms.

# 1.3 Acronyms Used in this Document

| Acronym               | Description                                         |

|-----------------------|-----------------------------------------------------|

| Acronym<br>A/D or ADC | Analog to Digital Converter                         |

| AMC                   | Advanced Mezzanine Card                             |

| BAR                   | Base Address Register                               |

| BE                    | Big Endian                                          |

| BPI                   | Byte Peripheral Interface                           |

| CPU                   | Central Processing Unit                             |

| DMA                   | Direct Memory Access                                |

| DSP                   | Digital Signal Processing                           |

| DWORD                 | Double Word (32-bits)                               |

| FIFO                  | First-In First-Out (Memory structure)               |

| FIR                   | Finite Impulse Response (Filter)                    |

| FPGA                  | Field Programmable Gate Array                       |

|                       |                                                     |

| Gbps                  | Giga-bits Per Second                                |

| GBps<br>HWM           | Giga-Bytes Per Second                               |

|                       | High Water Mark                                     |

| ioctl                 | Input/Output/Control                                |

| IP                    | Intellectual Property                               |

| LE                    | Little Endian                                       |

| LED                   | Light Emitting Diode                                |

| LPF                   | Low Pass Filter                                     |

| LSB                   | Least Significant Byte                              |

| LVCMOS                | Low-Voltage Complementary Metal Oxide Semiconductor |

| MAC                   | Media Access Controller                             |

| M-LVDS                | Multi-point Low Voltage Differential Signaling      |

| mmap                  | Memory Map                                          |

| MMC                   | Module Management Controller                        |

| MSB                   | Most Significant Byte                               |

| Msps                  | Mega-Samples Per Second                             |

| MUX                   | Multiplexer                                         |

| PCI                   | Peripheral Component Interconnect                   |

| PCIe                  | Peripheral Component Interconnect Express           |

| PHY                   | Physical Layer Device                               |

| PICMG                 | PCI Industrial Computer Manufacturer's Group        |

| PIO                   | Programmed Input/Output                             |

| PLL                   | Phase Locked Loop                                   |

| SERDES                | Serializer/Deserializer                             |

| SMB                   | SubMiniature version B (connector)                  |

| SPI                   | Serial Peripheral Interface                         |

| SRAM                  | Static Random Access Memory                         |

| TCLK                  | Telephony Clock                                     |

| VCXO                  | Voltage Controlled Crystal Oscillator               |

|                       | Table 1: Acronyms                                   |

# 2 Hardware Overview

The AMC511 card includes the following primary components (your ordering option may vary slightly):

- AMC MMC controller

- Xilinx Virtex-5 XC5VLX110T-1 FF1136 FPGA w/ BPI flash (Intel JS28F256P30T95)

- Texas Instruments CDCM7005 Clock Synchronizer

- Linear Tech LTC2209 180 Msps 16-bit A/D x4

- QDRII SRAM (2 x CY1515V18-250BZXC)

- Secondary Reference In, Trigger In, Sync Out

- Four channel M-LVDS clock transceiver

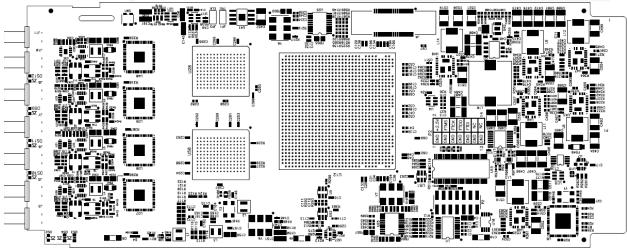

The top-side layout of the card is shown below:

Figure 1: AMC511 top-side layout

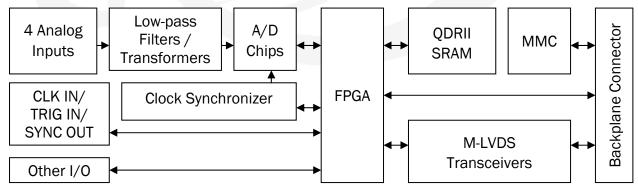

A simplified block diagram of the card is shown below:

Figure 2: AMC511 block diagram

## 2.1 Backplane SERDES Interfaces

The card is designed to support flexible system interfacing to the backplane via the reprogrammable FPGA. Interfaces such as PCIe x1/x2/x4/x8, 1000Base-X, XAUI, SRIO, Aurora, and others are realizable. The FPGA reference design demonstrates PCIe x8 and 1000Base-X interfaces. The primary interface for the reference design is PCIe x4 while the 1000Base-X base channels are simply there to show a SYNC indication to validate the hardware.

The possible backplane interfaces are shown below:

| GTP<br>Tile | AMC<br>Port | Reference Design                | XAUI Options      | SRIO Options             | Aurora Options             | GbE Options    |

|-------------|-------------|---------------------------------|-------------------|--------------------------|----------------------------|----------------|

| X0Y5        | 0           | GbE0 (hard core) [125MHz]       |                   |                          |                            |                |

| X0Y5        | 1           | GbE1 (hard core) [125MHz]       |                   |                          |                            |                |

| X0Y4        | 4           | PCIe x4/x8 (hard core) [250MHz] | XAUI0 [156.25MHz] | SRIO0A x1-x4 [156.25MHz] | AURORA0A x1-x8 [156.25MHz] | GbE2 [125MHz]  |

| X0Y4        | 5           | PCIe x4/x8 (hard core) [250MHz] | XAUI0 [156.25MHz] | SRIO0B x1-x4 [156.25MHz] | AURORA0A x1-x8 [156.25MHz] | GbE3 [125MHz]  |

| X0Y3        | 6           | PCIe x4/x8 (hard core) [250MHz] | XAUI0 [156.25MHz] | SRIO0C x1-x4 [156.25MHz] | AURORA0A x1-x8 [156.25MHz] | GbE4 [125MHz]  |

| X0Y3        | 7           | PCIe x4/x8 (hard core) [250MHz] | XAUI0 [156.25MHz] | SRIO0D x1-x4 [156.25MHz] | AURORA0A x1-x8 [156.25MHz] | GbE5 [125MHz]  |

| X0Y2        | 8           | PCIe x8 (hard core) [250MHz]    | XAUI1 [156.25MHz] | SRIO1A x1-x4 [156.25MHz] | AURORA0B x1-x8 [156.25MHz] | GbE6 [125MHz]  |

| X0Y2        | 9           | PCIe x8 (hard core) [250MHz]    | XAUI1 [156.25MHz] | SRIO1B x1-x4 [156.25MHz] | AURORA0B x1-x8 [156.25MHz] | GbE7 [125MHz]  |

| X0Y1        | 10          | PCIe x8 (hard core) [250MHz]    | XAUI1 [156.25MHz] | SRIO1C x1-x4 [156.25MHz] | AURORA0B x1-x8 [156.25MHz] | GbE8 [125MHz]  |

| X0Y1        | 11          | PCIe x8 (hard core) [250MHz]    | XAUI1 [156.25MHz] | SRIO1D x1-x4 [156.25MHz] | AURORA0B x1-x8 [156.25MHz] | GbE9 [125MHz]  |

| X0Y7        | 12          |                                 | XAUI2 [156.25MHz] | SRIO2A x1-x4 [156.25MHz] | AURORA1 x1-x4 [156.25MHz]  | GbE10 [125MHz] |

| X0Y7        | 13          |                                 | XAUI2 [156.25MHz] | SRIO2B x1-x4 [156.25MHz] | AURORA1 x1-x4 [156.25MHz]  | GbE11 [125MHz] |

| X0Y6        | 14          |                                 | XAUI2 [156.25MHz] | SRIO2C x1-x4 [156.25MHz] | AURORA1 x1-x4 [156.25MHz]  | GbE12 [125MHz] |

| X0Y6        | 15          |                                 | XAUI2 [156.25MHz] | SRIO2D x1-x4 [156.25MHz] | AURORA1 x1-x4 [156.25MHz]  | GbE13 [125MHz] |

| X0Y0        | 17          |                                 |                   | SRIO3 x1 [156.25MHz]     | AURORA2 x1-x2 [156.25MHz]  | GbE14 [125MHz] |

| X0Y0        | 18          |                                 |                   | SRIO4 x1 [156.25MHz]     | AURORA2 x1-x2 [156.25MHz]  | GbE15 [125MHz] |

| Key:     |                                                                              |

|----------|------------------------------------------------------------------------------|

| Green =  | = AMC.X standard port options (as supported for customer FPGA designs)       |

| Purple = | = AMC.X non-standard port options (as supported for customer FPGA designs)   |

| Yellow : | = AMC.X standard port mappings (as supported by VadaTech FPGA sample design) |

|          | Table 2: Possible packplane SERDES interfaces                                |

**NOTES:** Different protocol types can be mixed and matched within reason (pairs of lanes on the same GTX Tile must generally use the same protocol). If you change the backplane interfaces via a custom FPGA design please contact VadaTech for custom E-Keying records for the MMC so that your backplane E-Keying will match your FPGA implementation. Refer to the Virtex-5 documentation and IP documentation for limitations of the GTP tiles including clock forwarding, placement restrictions, resource granularity, etc.

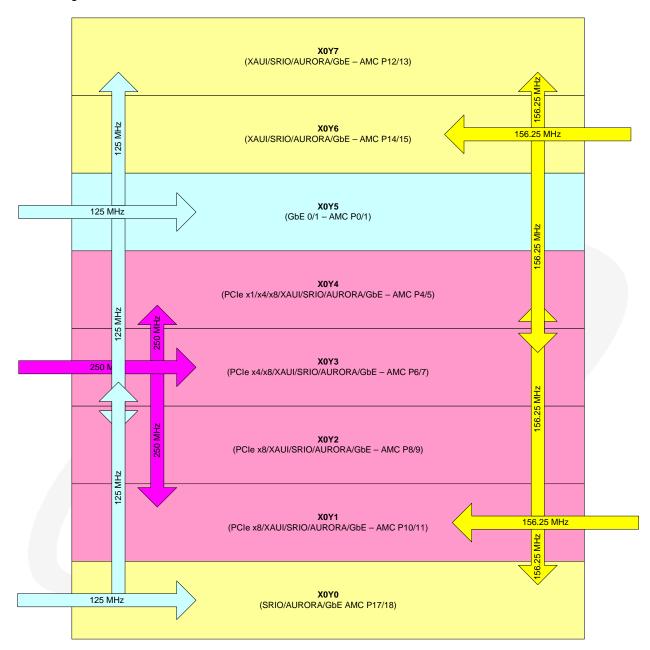

The AMC511 design attempts to provide the most flexible options for GTP tile clock forwarding. The following diagram illustrates the approach that was taken to minimize the limitations of the clock forwarding in the Virtex 5 FPGA:

Figure 3: Virtex 5 GTP clock forwarding for AMC511

# 2.2 AMC Card-edge Pin-out

| AMC<br>Finger | Net      | AMC<br>Finger | Net        | AMC<br>Finger | Net        | AMC<br>Finger | Net       | AMC<br>Finger | Net       |

|---------------|----------|---------------|------------|---------------|------------|---------------|-----------|---------------|-----------|

| 1             | GND      | 35            | n.c.       | 69            | AMC/RX7-   | 103           | AMC/TX10+ | 137           | GND       |

| 2             | AMC+12V  | 36            | n.c.       | 70            | GND        | 104           | GND       | 138           | CLKD-     |

| 3             | *AMCPS1  | 37            | GND        | 71            | AMCSDA     | 105           | AMC/RX11- | 139           | CLKD+     |

| 4             | AMCMP    | 38            | n.c.       | 72            | AMC+12V    | 106           | AMC/RX11+ | 140           | GND       |

| 5             | AMCGAO   | 39            | n.c.       | 73            | GND        | 107           | GND       | 141           | AMC/RX17- |

| 6             | n.c.     | 40            | GND        | 74            | CLKA+      | 108           | AMC/TX11- | 142           | AMC/RX17+ |

| 7             | GND      | 41            | *AMCENABLE | 75            | CLKA-      | 109           | AMC/TX11+ | 143           | GND       |

| 8             | n.c.     | 42            | AMC+12V    | 76            | GND        | 110           | GND       | 144           | AMC/TX17- |

| 9             | AMC+12V  | 43            | GND        | 77            | CLKB+      | 111           | AMC/RX12- | 145           | AMC/TX17+ |

| 10            | GND      | 44            | AMC/TX4+   | 78            | CLKB-      | 112           | AMC/RX12+ | 146           | GND       |

| 11            | AMC/TX0+ | 45            | AMC/TX4-   | 79            | GND        | 113           | GND       | 147           | AMC/RX18- |

| 12            | AMC/TX0- | 46            | GND        | 80            | PCI-E/CLK+ | 114           | AMC/TX12- | 148           | AMC/RX18+ |

| 13            | GND      | 47            | AMC/RX4+   | 81            | PCI-E/CLK- | 115           | AMC/TX12+ | 149           | GND       |

| 14            | AMC/RX0+ | 48            | AMC/RX4-   | 82            | GND        | 116           | GND       | 150           | AMC/TX18- |

| 15            | AMC/RX0- | 49            | GND        | 83            | *AMCPS0    | 117           | AMC/RX13- | 151           | AMC/TX18+ |

| 16            | GND      | 50            | AMC/TX5+   | 84            | AMC+12V    | 118           | AMC/RX13+ | 152           | GND       |

| 17            | AMCGA1   | 51            | AMC/TX5-   | 85            | GND        | 119           | GND       | 153           | n.c.      |

| 18            | AMC+12V  | 52            | GND        | 86            | GND        | 120           | AMC/TX13- | 154           | n.c.      |

| 19            | GND      | 53            | AMC/RX5+   | 87            | AMC/RX8-   | 121           | AMC/TX13+ | 155           | GND       |

| 20            | AMC/TX1+ | 54            | AMC/RX5-   | 88            | AMC/RX8+   | 122           | GND       | 156           | n.c.      |

| 21            | AMC/TX1- | 55            | GND        | 89            | GND        | 123           | AMC/RX14- | 157           | n.c.      |

| 22            | GND      | 56            | AMCSCL     | 90            | AMC/TX8-   | 124           | AMC/RX14+ | 158           | GND       |

| 23            | AMC/RX1+ | 57            | AMC+12V    | 91            | AMC/TX8+   | 125           | GND       | 159           | n.c.      |

| 24            | AMC/RX1- | 58            | GND        | 92            | GND        | 126           | AMC/TX14- | 160           | n.c.      |

| 25            | GND      | 59            | AMC/TX6+   | 93            | AMC/RX9-   | 127           | AMC/TX14+ | 161           | GND       |

| 26            | AMCGA2   | 60            | AMC/TX6-   | 94            | AMC/RX9+   | 128           | GND       | 162           | n.c.      |

| 27            | AMC+12V  | 61            | GND        | 95            | GND        | 129           | AMC/RX15- | 163           | n.c.      |

| 28            | GND      | 62            | AMC/RX6+   | 96            | AMC/TX9-   | 130           | AMC/RX15+ | 164           | GND       |

| 29            | n.c.     | 63            | AMC/RX6-   | 97            | AMC/TX9+   | 131           | GND       | 165           | AMCTCLK   |

| 30            | n.c.     | 64            | GND        | 98            | GND        | 132           | AMC/TX15- | 166           | AMCTMS    |

| 31            | GND      | 65            | AMC/TX7+   | 99            | AMC/RX10-  | 133           | AMC/TX15+ | 167           | *AMCTRST  |

| 32            | n.c.     | 66            | AMC/TX7-   | 100           | AMC/RX10+  | 134           | GND       | 168           | AMCTDO    |

| 33            | n.c.     | 67            | GND        | 101           | GND        | 135           | CLKC-     | 169           | AMCTDI    |

| 34            | GND      | 68            | AMC/RX7+   | 102           | AMC/TX10-  | 136           | CLKC+     | 170           | GND       |

Table 3: AMC card-edge pin-out

# 2.3 Front Panel Interfaces

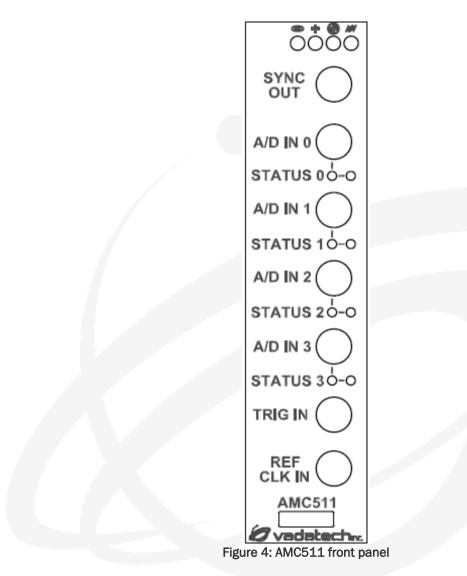

The front panel of the AMC511 is shown below:

#### 2.3.1 Front Panel Management Interfaces

The front panel includes the standard AMC LEDs showing hot-swap status and general card health. The LEDs behave as follows:

| LED   | Off                 | On                  | Blink                        |

|-------|---------------------|---------------------|------------------------------|

| Blue  | Card active         | OK to remove        | Hot-swap/power transitioning |

| Red   | No Fault            | Persistent fault    | Transient fault              |

| Green | No management power | Management power OK | Management power OK          |

|       |                     | Payload power OK    | Payload power not expected   |

| Amber | Normal              | Firmware upgrade    | N/A                          |

Table 4: AMC LED behavior

**NOTE:** The card should only be removed from a running carrier when the AMC Blue LED is solid ON.

To insert the card, pull out the hot-swap handle until it stops. Insert the card into the carrier's guide rails and push on the front panel firmly until it is fully seated into the connector. If the card does not go fully in, do not force it and instead remove it and check for proper orientation or obstructions. Once fully inserted the Blue LED should go to solid ON while the Green LED should start blinking. Then push in the handle to latch the card into the carrier, the Blue LED should blink for a time and then go solid OFF while the Green LED goes solid ON.

To remove the card, pull out the hot-swap handle until it stops to unlatch the card from the carrier (but do not pull hard enough to remove the card itself yet). The Blue LED should blink for a time and then go solid ON. Once it does, pull the hot-swap handle straight out firmly to remove the card from the carrier.

#### 2.3.2 Front Panel A/D Inputs

The four front panel A/D inputs are provided via SMB connectors which go into a low-pass filter structure, are transformer coupled, and then go into the A/D chips. Please refer to the A/D chip datasheet for signal characteristics.

#### 2.3.3 Front Panel Synchronization Interfaces

The front panel provides REF CLK IN and TRIG IN SMB connectors which are 3.3v LVCMOS compatible (after the optional 50 ohm termination). A SYNC OUT SMB output comes from the FPGA which drives as 3.3v LVCMOS. Refer to the following sections for details on how to enable/disable the 50 ohm input terminations.

### 2.3.4 Front Panel Channel Status LEDs

The front panel includes one set of green and amber LEDs per analog input. These LEDs default to showing various diagnostic status indicators when the FPGA is first configured. The default power-on behavior is shown below:

| LED            | Indication        |

|----------------|-------------------|

| STATUS 0 Green | 1000Base-X 0 SYNC |

| STATUS 0 Amber | Blinking          |

| STATUS 1 Green | 1000Base-X 1 SYNC |

| STATUS 1 Amber | OFF               |

| STATUS 2 Green | PCIe link up      |

| STATUS 2 Amber | PCIe x4 width     |

| STATUS 3 Green | SRAM Passing      |

| STATUS 3 Amber | SRAM Failing      |

Table 5: STATUS LEDs power-on behavior

**NOTE:** If both the SRAM Passing and SRAM Failing LEDs are lit this means that the SRAM controller is doing calibration. This calibration will never end if the AMC511 was ordered without the SRAM ordering option; and would therefore be considered a normal condition. Otherwise, with SRAM mounted the calibration should complete very quickly and then only show the SRAM Passing indication.

The reference device driver changes these LEDs to their normal run-time indications once it loads. The normal run-time behavior is shown below:

| LED                 | Indication                  |

|---------------------|-----------------------------|

| STATUS 0 Green      | A/D Channel O Running       |

| STATUS 0 Amber      | A/D Channel O Fault         |

| STATUS 1 Green      | A/D Channel 1 Running       |

| STATUS 1 Amber      | A/D Channel 1 Fault         |

| STATUS 2 Green      | A/D Channel 2 Running       |

| STATUS 2 Amber      | A/D Channel 2 Fault         |

| STATUS 3 Green      | A/D Channel 3 Running       |

| STATUS 3 Amber      | A/D Channel 3 Fault         |

| Table 6: STATUS   E | De normal run time habaviar |

Table 6: STATUS LEDs normal run-time behavior

The run-time behavior can be changed via software if desired. Please refer to the register specification later in this document.

**NOTE:** The 'Fault' indication is a combination of various statuses from the channel such as A/D conversion overflow, FIFO overflow/underflow, etc. Please refer to the register specification later in the document for details.

# 2.4 Switches / Jumpers / Headers

The card includes a JTAG header at P2. This header is for programming the FPGA and/or BPI flash and is compatible with the Xilinx Platform Cable USB II.

The card includes a set of DIP switches at SW2. The first two switches on SW2 (1 and 2) are for factory use only and should be set to the OFF position for normal operation. SW2-3 controls the routing of the JTAG lines to the FPGA as follows:

| SW2-3                                              | Description                                          |  |  |

|----------------------------------------------------|------------------------------------------------------|--|--|

| OFF                                                | Connect the JTAG header (P2) to the FPGA's JTAG port |  |  |

| ON Connect the AMC fingers to the FPGA's JTAG port |                                                      |  |  |

| Table 7: SW2-3 JTAG routing selection              |                                                      |  |  |

SW2-4 controls the write protection for the BPI Flash chip as follows:

| SW2-4                                     | Description                        |  |  |  |

|-------------------------------------------|------------------------------------|--|--|--|

| OFF                                       | Do not write protect the BPI Flash |  |  |  |

| ON                                        | Write protect the BPI Flash        |  |  |  |

| Table 8: SW2-4 BPI Flash write protection |                                    |  |  |  |

Table 8: SW2-4 BPI Flash write protection

JP1 and JP2 select the 50 ohm termination for the TRIG IN and REF CLK IN inputs respectively as follows:

|                                                    | JP1/JP2 | Description                                     |  |

|----------------------------------------------------|---------|-------------------------------------------------|--|

|                                                    | OPEN    | No input termination for TRIG IN/REF CLK IN     |  |

| SHUNT 50 ohm input termination for TRIG IN/REF CLK |         |                                                 |  |

|                                                    |         | Table 9: JP1 and JP2 optional input termination |  |

**NOTE:** The board expects a 3.3V compatible resulting signal AFTER the optional input termination. That means that if you use the input termination you may need to use a higher voltage so that the result after termination is 3.3V compatible.

The card includes an expansion/debug header at J4. This header provides expansion/debug ports for the FPGA. The header is a Tyco Mictor 38-pin receptacle (part number 2-767004-2). All of the pins use 2.5v LVCMOS signaling. The header is pinned out as follows (with the center blades also as Ground):

| Pin | Signal | Pin | Signal |

|-----|--------|-----|--------|

| 1   | (open) | 2   | (open) |

| 3   | Ground | 4   | (open) |

| 5   | CLKE   | 6   | CLKO   |

| 7   | D15E   | 8   | D150   |

| 9   | D14E   | 10  | D140   |

| 11  | D13E   | 12  | D130   |

| 13  | D12E   | 14  | D120   |

| 15  | D11E   | 16  | D110   |

| 17  | D10E   | 18  | D100   |

| 19  | D09E   | 20  | D090   |

| 21  | D08E   | 22  | D080   |

| 23  | D07E   | 24  | D070   |

| 25  | D06E   | 26  | D060   |

| 27  | D05E   | 28  | D050   |

| 29  | D04E   | 30  | D040   |

| 31  | D03E   | 32  | D030   |

| 33  | D02E   | 34  | D020   |

| 35  | D01E   | 36  | D010   |

| 37  | DOOE   | 38  | D000   |

Table 10: J4 pin-out

# 3 Reference FPGA Design Overview

The FPGA is fully customizable and it is expected that customers will want to provide their own custom DSP solution. However, a reference design is also provided to demonstrate the basic board functionality and to provide a complete solution which may be sufficient for some customer's needs. The remainder of this manual discusses the reference design and culminates in a discussion of how the customer may either customize or replace the reference design to add new DSP functionality.

The reference design provides four A/D channels running at 180 Msps under the control of an external host CPU via a PCIe x4 interface. It also provides two 1000Base-X base channel ports which are only present in the reference design to verify the hardware by attaining SYNC. There is no reference application logic attached to the 1000Base-X port. Finally, the reference design includes an SRAM controller with BIST. Again this controller is only in the reference design to validate the hardware and provide a pass/fail indication. The reference design does not make use of the SRAM directly.

| ltem                | Value                                         |

|---------------------|-----------------------------------------------|

| Vendor ID           | OxABCD (VadaTech Incorporated)                |

| Device ID           | 0x4511 (AMC511)                               |

| Subsystem Vendor ID | OxABCD (VadaTech Incorporated)                |

| Subsystem Device ID | 0x4511 (AMC511)                               |

| BAR 0               | 64KB (32-bit memory mapped, non-prefetchable) |

| Max Payload         | 512 bytes                                     |

The PCIe configuration space information is as follows:

Table 11: PCle configuration

The design supports a control/status register interface via 32-bit PCIe PIO as well as a four channel DMA controller which uses PCIe posted writes with burst length based on the negotiated largest burst size. The DMA channels are arbitrated by a round-robin arbiter to ensure fairness. The design includes an interrupt controller which signals interrupts using either Legacy INTA or an MSI vector whichever is supported by the system.

The clock synchronizer chip is controlled via a SPI master in the FPGA and its status is monitored with interrupt notification of changes. A flexible clock/signal router allows many different signals to be passed out the front panel output or the backplane M-LVDS outputs. An LED controller is provided which allows for various statuses to be monitored visually on the front panel.

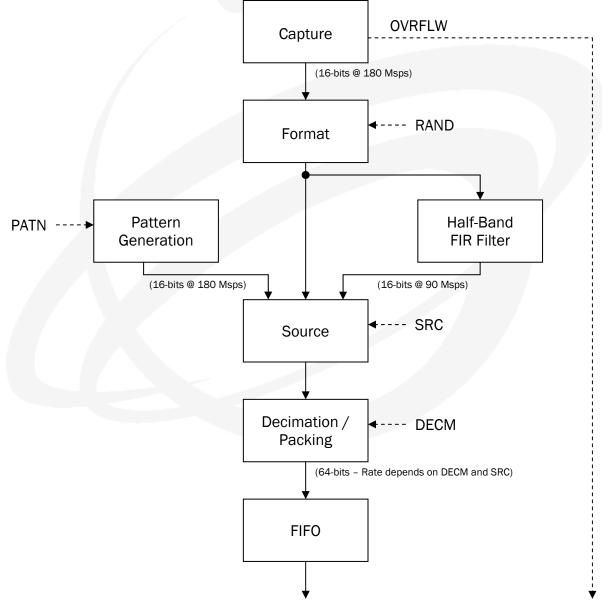

Each A/D chip's output data is pushed through a pipeline in the FPGA which includes the following stages (many of them optional):

- Capture (clocks in the data as close to the pins as possible)

- Optional Formatting (removes effects of the A/D chip's RAND function)

- Optional Pattern Generation (for debugging)

- Optional Half-Band FIR low-pass filter (reduces the data rate by a factor of 2)

- Optional Decimation (reduces the data rate by a factor of 2 to 256 without filtering)

- Packing (Positions four 16-bit samples into one 64-bit FIFO entry)

- 64KB FIFO (Gets data from A/D clock domain to PCIe clock domain/buffers the data)

The pipeline is structured as shown in the following diagram:

Figure 5: ADC pipeline

Each pipeline stage signals the next when it has data available, so that the data reaching the user application only contains valid samples.

Note that when the Half-band filter is used the data rate is already decimated by a factor of 2 prior to hitting the Decimation stage. The Decimation stage should only be used to evaluate system throughput/loading or if the input signal is already appropriately band-limited prior to entry to the board, otherwise aliasing may occur. In the latter case, a high-quality external low-pass filter with a cut-off at half the decimated sample rate is strongly recommended.

## 3.1 PCIe Bridge w/ DMA Burst Engine

The PCIe Bridge implements a state machine which converts PCIe Transaction layer packets into internal local bus transactions. It supports up to 32-bit PIO reads and up to 32-bit PIO writes. It also generates out-bound DMA bursts as requested by the DMA Burst Arbiter. The PIO Reads/Writes take priority over the DMA bursts so that the host CPU does not stall needlessly.

### 3.2 DMA Burst Arbiter

The DMA Burst Arbiter supports four ADC clients and arbitrates between them on a roundrobin basis to ensure fair access to the DMA Burst Engine.

### 3.3 ADC Controller w/ DMA Burst Scheduler

Each ADC controller implements control/status registers, a data pipeline, and a DMA Burst Scheduler. The control/status registers enable control over the A/D chip as well as the processing pipeline and DMA. Data can be gathered from the end of the pipeline either by PIO or DMA accesses; however, DMA access is strongly advised due to the extremely high data rates involved. The A/D chip is automatically put into power-saving mode when the channel is not enabled to reduce power usage and heat generation.

#### 3.3.1 Capture Stage

The capture stage simply clocks the data into the FPGA. This stage exists solely to ensure that the flip-flops involved can be placed directly at the input pad to minimize timing skew. The data from the chips is 16-bit signed (two's compliment) sample data plus one bit of overflow indication. The overflow indication is stripped off after this stage and is captured by a status register instead of following the remaining data flow. This maximizes the bandwidth utilization of the PCIe bus since 17-bit data doesn't pack very efficiently.

#### 3.3.2 Formatting Stage

The formatting stage will automatically remove the XOR randomization that is applied by the A/D chip when the RAND feature is used. It is recommended that the RAND feature always be used to spread the spectrum of the noise caused by the A/D chip outputs.

#### 3.3.3 Pattern Generation Stage

A pattern generator can be switched in as the data source for the decimation stage rather than the formatted A/D data or FIR data. The pattern generator is useful in verifying the dataflow through the hardware and software to the end-user application. It is capable of generating the following patterns:

- All zero bits

- All one bits

- Most negative signed 16-bit value

- Most positive signed 16-bit value

- Repeating ramp from most negative to most positive 16-bit values

#### 3.3.4 Half-Band FIR Low-Pass Filter Stage

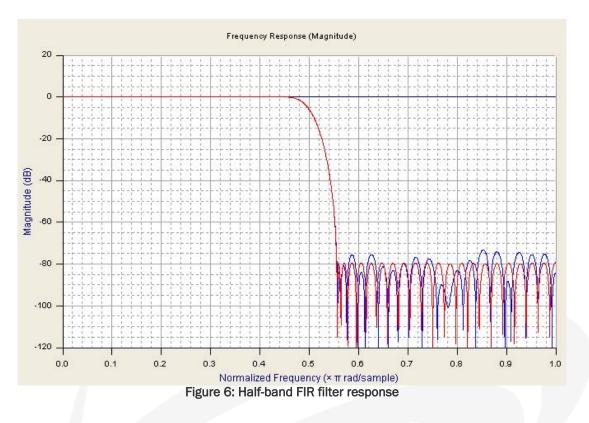

The FIR filter stage implements an 83-tap half-band low-pass filter with decimation by 2. It utilizes Distributed Arithmetic architecture to allow it to operate at the full incoming sample rate. Samples go into the filter at 180 Msps and come out at 90 Msps. The FIR filter takes care of band-limiting the data prior to decimation to avoid aliasing. Note that this decimation is fixed and independent of the Decimation Stage as described in the next section. The FIR filter has approximately 80dB stop-band attenuation as shown on the next page:

#### 3.3.5 Decimation Stage

The Decimation Stage optionally drops samples (without low-pass filtering). It can reduce the sample rate by a factor of 2 to 256. A setting of 0 performs no decimation (equivalent to decimation by a factor of 1), while a setting of 1 performs decimation by a factor of 2, etc.

#### 3.3.6 Packing Stage

The A/D chips and the data pipeline are 16-bit and the PCIe core is 64-bit, so this stage simply packs four samples into one FIFO entry.

#### 3.3.7 FIFO Stage

After the samples are packed they are pushed into a 64KB FIFO structure. This structure serves two purposes. First it enables seamless crossing from the A/D clock domain into the PCIe clock domain. Second it absorbs the latencies which occur while buffering up a DMA burst, waiting for other bus activity to complete, software latencies, etc. The pipeline design ensures that by the time the samples are taken out of the FIFO the host software will know if there was any A/D converter overflow, FIR overflow, or FIFO overflow/underflow so that a high degree of confidence can be established in the captured data.

#### 3.3.8 DMA Burst Scheduler

Each ADC channel has its own DMA Burst Scheduler. The scheduler uses two scatter-gather DMA descriptor chains to facilitate very low-overhead streaming transfers to the main system memory. It reads the DMA descriptors and schedules burst transfers to complete the chunks described there. It waits for the FIFO to fill enough to satisfy a burst then it requests service from the DMA Burst Arbiter. The DMA Burst Arbiter forwards the request to the DMA Burst Engine which will then complete the burst by reading the FIFO using special 64-bit internal reads and writing the data out across the PCIe bus into system memory as instructed. The DMA Burst Scheduler notifies the software whenever a chain completes via a status register/interrupt. Each descriptor can point to up to 512KB of physically contiguous memory with a size/alignment granularity of 4KB. There are 128 descriptors per chain.

The DMA Burst Scheduler has a special mode which can be used for sourcing point-to-point (card-to-card) PCle DMA transfers rather than doing card-to-memory transfers. This mode may be used for example if the AMC511 card is designated for capturing data while a second card is designated for doing additional DSP of the data. The software reference design doesn't support this mode of operation. However, it is provided in the FPGA as a starting point of what could be done in more sophisticated configurations designed to fully exploit the point-to-point architecture of PCle (where data does not always need to flow through the memory/CPU).

### 3.4 Interrupt Controller

The central interrupt controller consolidates the interrupt lines coming from the four ADC cores and the Clock Synchronizer core to provide one single master interrupt line to the PCIe Bridge. The interrupt controller also supports a Bit Change Interrupt mechanism which is used for alerting the software any time the Clock Synchronizer status lines change.

### 3.5 Clock Synchronizer Controller

The Clock Synchronizer Controller implements a control/status register for basic control of the TI Clock Synchronizer chip. It also implements a SPI Master which can be used to set all of the registers within the TI chip using a serial protocol. The SPI Master handshakes with the host software to ensure that it remains synchronized with the serial data transfer so the software can know when the transfer is complete.

#### 3.5.1 SPI Master

The TI chip includes four 32-bit control registers which are set via a SPI bus interface. The SPI Master function in the Clock Synchronizer Controller provides four shadow registers

which are available via PCIe PIO read/write which it shifts out to the TI chip on command from the host software.

Each time the host software instructs the SPI Master to start; it shifts all four data words to the chip using a 500 kHz clock and then indicates completion to the software via a status register/interrupt.

The SPI Master's default register values are customized to match the AMC511 hardware and differ from the TI chip defaults. These new defaults are shifted out immediately upon FPGA configuration without software intervention. The SPI Master enforces read-only semantics on some of the control fields that are otherwise read/write for the TI chip so that parameters specific to the AMC511 circuits are not violated inadvertently.

### 3.6 Clock/Signal Router

The Clock/Signal Router enables flexible routing of off-board and on-board signals such as clocks and status indicators, etc. It also enables/disables various input/output buffers. See the register specification that follows for details of routing sources and targets.

### 3.7 LED Controller

The LED Controller allows various statuses to be reflected onto the front panel User LEDs. See the register specification for details on the available LED sources.

### 3.8 BPI Flash Controller

The FPGA reference design includes a BPI Flash Controller which enables the FPGA's BPI Flash to be reprogrammed via PCIe in the field and then trigger the FPGA reconfiguration. This mechanism can be used in place of a JTAG probe for FPGA upgrades.

### 3.9 Utility Functions

The FPGA includes various utility functions such as reporting its version number and signature, as well as providing a scratch register for bus testing.

# 4 Reference Software Overview

The software provided with the FPGA reference design targets the Linux operating system with Linux Kernel 2.6. It includes the following:

- amc511.ko: Device driver module for Linux 2.6 kernel

- amc511tool: Tool for controlling the driver/card

- **fcf2coe**: Filter coefficient conversion utility

The device driver's makefile should be customized to point at the kernel sources on the build machine prior to building it. The other tools should build without customization; however the amc511tool does require that development support for 'pcilib' be present. This dependency can be stripped out if support for the debugging commands is not needed.

The coefficient conversion utility aids in designing new filters for inclusion in a customized FPGA image. It converts Matlab FCF file format (single/double precision floating point) to Xilinx FIR Filter Compiler COE file format (floating point decimal). It can be helpful if Matlab was purchased with the Signal Processing/Filter Design toolkits but not the Fixed Point toolkit (which includes a COE export functionality). The Xilinx FIR Filter Compiler can automatically quantize floating point decimal COE files.

### 4.1 AMC511 Device Driver

The device driver is capable of supporting AMC511 cards attached to the PCIe bus of the host CPU. Each card will be assigned four minor device numbers in the order of probing. These minor device numbers represent A/D channels on the card. The global functionality of the card is accessible via any of the four channels and it is the responsibility of the application to ensure that the global settings are suitable for all four channels. The global settings include the Clock Synchronizer, Clock Routing, and LEDs.

The device driver supports PIO and DMA transfer of data. DMA is the default and recommended method since it is dramatically more efficent, but PIO can be used for low data rate applications or for debugging. A module parameter is available to force PIO mode. For example:

#### insmod amc511.ko force\_pio=1

In order to reduce the system load as much as possible during data transfer, the device driver pre-allocates the DMA/PIO buffer chains when each card is probed and re-uses the descriptors/buffers over and over again. The allocation is done using single pages (scatter/gather) to reduce pressure on the kernel memory allocator.

The number of pages to use for each transfer can be specified using a module parameter. Examples:

insmod amc511.ko xfer\_pages=128

insmod amc511.ko force\_pio=1 xfer\_pages=15

The maximum number of pages per transfer for DMA is 128 (512KB) while the maximum for PIO is 15 (60KB). Since the driver and card perform streaming using two descriptor chains (i.e. the card can be writing to memory in one chain while the application is reading from memory in the other chain), twice the specified amount of memory is allocated by the driver. So for the DMA case up to 1MB of memory can be dedicated to each A/D channel.

Generally the larger the value of xfer\_pages, the higher the latency of the samples from A/D to application but the lower the system load. Conversely specifying a smaller value for xfer\_pages reduces the latency but increases the system load. It is up to the end-user application requirements to determine the best trade-off.

The device driver optimizes data transfer to the user application by allowing the application to memory map the driver's buffer chains directly into the application's virtual memory map. Once this is done the two buffer chains appear as one contiguous region of application virtual memory. When used with DMA, this makes the transfer of A/D data from the card all the way into the user application a zero-copy operation from the CPU's point of view and results in extremely low CPU overhead. This leaves almost all of the CPU's time available for user application processing of the A/D data or other application behavior.

The device driver supports open, close, mmap, poll/select, and ioctl operations from the application. Generally the application should open() one or more channels as desired, then make an ioctl call to get information about the channel. This information includes the size of the mmap region to be used. Once the information is obtained, the application should mmap() the buffer region and then proceed to enable the A/D channel.

After the channel is enabled the application can call the poll() or select() system call to wait for data or status to become available. The application can use POLLPRI for status changes and/or POLLIN for new A/D data. If the driver indicates that the status changed then the application should read the status using the appropriate ioctl. If the driver indicates that data is available then the application should get information about the data using the appropriate ioctl. As mentioned before, the data is actually already in the application's virtual memory space, so this ioctl simply provides an offset and length within the mmaped region so that the application knows where to find it.

After this call is made, the indicated buffer memory is marked as reserved for application use by the driver and neither the driver nor the card will touch it. Once the application has read or processed the data, the buffer space must be returned to the driver using the appropriate ioctl. This once again makes the buffer space accessible by the card for the next transfer. Keep in mind that there are two descriptor chains, so the driver/card will be transferring data into the next chain while the application is reading the current chain, so the application should not access the buffer memory after the memory has been returned to

the driver. Depending on the host CPU type, if the application accesses the data buffers at the wrong time (even if it is only reading them) cache coherency may be lost resulting in data corruption.

The application should return buffer memory to the driver as soon as possible to avoid stalling the streaming transfer and risking overflow of the channel's FIFO. This is another tradeoff however, in that it is probably more efficient overall to process the data directly in the memory buffer and then return it to the driver rather than making a copy of it prior to processing. But each application is different and some experimentation may be necessary to tune the overall system performance. In either case, the card/driver provides all of the necessary status information to let the application know when/if the FIFO overflows so that performance tuning can be accomplished.

Once the capture is complete the application should disable the channel and/or close() the file handle. The driver will automatically disable the channel when the file handle is closed if it was not already disabled.

The ioctl() interfaces available for the device driver are documented in an appendix at the end of this document.

## 4.2 AMC511 Tool Application

The amc511tool provides basic support for controlling the card and gathering status as well as capturing A/D data. It can capture data to memory and discard it (to test the PCIe and memory bandwidth of the system) or it can capture it to a file.

The tool supports two distinct modes of operation. One mode uses the device driver interfaces (as would be recommended during typical activities). The other mode bypasses the device driver by mapping the PCIe BAR into user-space using 'pcilib' and reading/writing registers directly. This mode is for debugging only as it can potentially interfere with the device driver.

The usage information for the tool is shown below:

```

usage: amc511tool <cmd> [<opts>]

NORMAL CMDs: (use device driver)

- Detect driver/card and report version info

detect <dev>

leds <dev> [<green0> <green1> <green2> <green3>

<amber0> <amber1> <amber2> <amber3>1 - Show/set LED selectors

routing <dev> [<sync_out> <tclka_out> <tclkb_out> <tclkc_out> <tclkd_out>

<adc0_trigin> <adc1_trigin> <adc2_trigin> <adc3_trigin>

<pri_ref> <sec_ref> <sync_out_en> <trig_in_en> <ref_clk_in_en>

<tclkx_in_en> <tclka_out_en> <tclkb_out_en>

<tclkc_out_en> <tclkd_out_en>] - Show/set clock routing

clksync <dev> [primary|secondary] - Show/set clock synchronizer settings

status <dev> [monitor] - Show/monitor channel status flags

capture <dev> <decm> <pat> <src> <pga> <rand> <dith>

imit> [<file>] - Capture ADC data from channel

DEBUG CMDs: (direct memory mapping of device/bypass device driver)

adc <0-3> <decm> <pat> <src> [file] - Start/Dump ADC channel 0-3 FIFO data

ovrflw <0-3> <pga>- Monitor ADC channeldump [all|desc]- Dump the register contewrite <addr> <val>- Write value at addressprofile [read|write]- Test PIO read/write spetest [scratch|sig]- Repeated Read/Write or

- Monitor ADC channel 0-3 OVRFLW status

- Dump the register contents

- Test PIO read/write speed

- Repeated Read/Write or Read tests

```

The options for the tool generally follow the field definitions in the register specification. So for instance the values which can be provided for **pat** match what is described in the CHCTRLx register's PAT field.

Note that the ADC channels always have their trigger logic enabled and will not start capturing data after the channel is enabled until they see a logical '1' on their internal trigger input. Therefore, if an external trigger signal is not being used, the adcx\_trigin options for the routing command should be set to '1' to create an auto-trigger functionality.

The amc511tool source code can be used as a reference for the development of end-user applications.

# 5 System Performance Considerations

Capturing A/D data is a continuous real-time streaming operation that involves many aspects of the system and not just the AMC511 card. The AMC511 FPGA can actually process data rates faster than the rest of the system can handle. Four channel signal acquisition at 180 Msps produces about 1.44 GB/s worth of data in addition to necessary status/control register reads/writes.

Factors such as FPGA overhead, memory bandwidth, CPU speed/loading, data path, and application behavior will impact the sustainable streaming throughput. As an example it may be possible to write full rate data to a file if the capture is limited to a few megabytes, but if unconstrained the streaming will quickly stall and overflow the FIFO when the filesystem buffers and hard drive cache fill up due to the inability of the hard drive platters to sustain that rate. Therefore it is important to understand the performance characteristics of every piece of hardware/software in the complete data path to see where a bottleneck might be occurring. It is also important to keep in mind that sometimes the effects of the bottleneck might not be immediately apparent and will only show up after some amount of time such as the hard drive cache effect mentioned here.

For high sample rate applications the best approach is to customize the FPGA to do the DSP operations in an environment where cycle-accurate, real-time performance can be guaranteed and then transfer the resulting data at a greatly reduced data rate to the host memory/CPU via PCIe or other link. The reference design may not be fully optimized for your particular application; it is simply provided as a working example from which to branch off from with your own development.

## 5.1 Software Optimization Tips

The application should strive to put the data buffer back to the driver before it is actually needed by the card for the next DMA transfer. The driver/card will deal with either case seamlessly as long as the FIFO does not overflow as a result of the stall. The driver will post both buffer chains to the card whenever possible so that the DMA Burst Scheduler on the card does not stall. Whenever the DMA Burst Scheduler sees that the next chain is available upon completion of the current one it proceeds to process the next chain without direct software intervention. This greatly helps to avoid the cumulative and variable effects of software/interrupt latency on the on-going streaming transfer.

It is possible to route the FPGA's internal interrupt request line out to the front panel Sync output and view it on an oscilloscope or send it to a frequency counter. This technique works best for single channel acquisition but it can also be used under full load to get a feeling for the overall interrupt frequency. When the line is low the card is not requesting interrupt service and when it is high it is requesting interrupt service. By watching this line it is possible to interpret how well the system is responding to the card's needs.

By observing the width of the low-period while the tool application is acquiring and discarding data is it is possible to see how much time the user's own application can be afforded between transfers to process the data. This single-channel information can then be scaled according to how many channels the user's own application will actually be processing.

If the user's own application starts overflowing the FIFO then the extended low-period of the interrupt request line should be detectable as a result of the delay caused when the application didn't put the data buffer back in time to prevent a stall of the DMA engine. The difference between this and the previously established baseline should reveal how much the application is exceeding its allocated time to process the data.

By observing the width of the high-period it is possible to see if other device drivers or kernel activities are contributing to interrupt latency (by locking out interrupts). If the high-period shows a lot of variability or occasional very long high pulses this can have an adverse effect on the streaming since it will delay the notification of new data availability from the driver to the application and therefore reduce the amount of time the application has to process the data before the card needs that buffer back again. If undesirable interrupt latency is occurring, the solution is not to look at the amc511.ko driver (which has a fairly consistent interrupt processing and lockout time), but instead to look to other sources of interrupt latency which would actually be in the kernel-layer but could possibly be stimulated by user-space activity. Typical sources might be hard drive access, networking drivers, USB, serial ports, etc. Try to eliminate these sources of latency by either disabling the devices or not using them during signal acquisition to see if the interrupt latency shown by the AMC511 card is improved.

By customizing the FPGA it is also possible to add performance counters to measure such things as bus utilization, stall time, idle time, etc in a more direct manner.

# 6 FPGA Customization

The reference FPGA design combines IP cores from Xilinx with VadaTech custom VHDL code. This design can be customized or replaced by the customer to allow for high-end custom DSP solutions that are tailor-made to take full advantage of the considerable signal processing capabilities of the Xilinx Virtex-5 FPGA. In order to ease this effort, this section of the document describes some of the building blocks used in the FPGA reference design as well as some development techniques particular to the AMC511 board.

Having the VHDL sources available while reading this section is recommended to see the correspondence of various files or instances of cores mentioned here.

The following cores from Xilinx are used:

- PCIe x4 Endpoint Plus (ep)

- Wraps the Virtex 5 embedded PCIe core

- o Provides the basic control/status/data interface for the reference design

- Tri-mode Ethernet Core in 1000Base-X mode (dual\_enet\_block)

- Wraps the Virtex 5 embedded MAC core

- o Simply tests link establishment in the reference design

- Rocket I/O GTP Core (GTP\_DUAL\_1000X\_inst)

- Wraps the Virtex 5 GTP tile

- Used as the 1000Base-X SERDES PHY in the reference design

- Block Memory Generator (chain0/1\_ram)

- Used for holding the ADC DMA descriptors

- FIFO Generator (adc\_dcfifo\_inst, main\_to\_adc\_mailbox)

- Used for holding the ADC sample data (clock-domain crossing/buffering)

- Used for the ADC control mailbox (clock-domain crossing)

- FIR Compiler (fir\_halfband\_inst)

- o Used for the ADC half-band low-pass decimating filter

- Memory Interface Generator (sram\_ctrl)

- Used to generate the SRAM controller

It is expected that if the customer wishes to synthesize a new FPGA image, that they will have access to both the Xilinx ISE tool v11.3 or later (full version required to support the Virtex-5 chip on the board) as well as the necessary IP cores. Most of the IP cores are generic or else they are wrappers for Virtex-5 embedded blocks and therefore are included

with the ISE license at no extra charge from Xilinx. The Xilinx ISE tool license is not included as part of the purchase of the AMC511 card.

Refer to the applicable datasheets, user guides, and app notes from Xilinx for more details.

The VadaTech custom cores used in the reference design include:

- Top level wrapper (amc511\_fpga.vhd)

- Glues everything together at the top level

- ADC Controller/Pipeline w/ DMA Burst Scheduler (adc\_core.vhd)

- Controls each ADC and processes the dataflow from it

- PCIe to Local Bridge w/ DMA Burst Engine (pcie\_local\_bridge.vhd)

Provides PIO Read/Write and DMA Write capabilities

- DMA Burst Arbiter (dma\_burst\_arbiter.vhd)

o Round-robin arbitration of the DMA Burst Engine between the four ADCs

- Clock Synchronizer Controller (clksync\_core.vhd)

Controls the synchronizer chip via SPI and reports status

- Clock/Signal Router (clkrouter\_core.vhd)

- Flexibly routes clock/status/debug signals between places in the design

- LED Controller (led\_core.vhd)

Controls the user LEDs

- BPI Flash Controller (bpi\_flash.vhd)

- o Provides a simple interface to the BPI Flash bus for reprogramming

- General Purpose Utility Core (vt\_utility\_x32.vhd)

- Provides version information and general utility functionality

- General Purpose Arbitrary Clock Enable Divider (vt\_clocken\_div\_arbitrary.vhd)

- Provides a re-usable way to slow down portions of the design while still using the same clock

- General Purpose Interrupt Controller (vt\_interrupt\_controller\_x32.vhd)

- o Provides a re-usable way to implement an interrupt controller for the design

- General Purpose Reset Synchronizer (vt\_reset\_sync.vhd)

- Provides a re-usable asynchronous assertion/synchronous de-assertion reset

- General Purpose Clock Synchronizer (vt\_multi\_sync.vhd)

- Provides a re-usable way to get individual signals from one clock domain to another to mitigate meta-stability

**LEGAL NOTICE:** The VadaTech custom VHDL code included in this reference design is the intellectual property of VadaTech Incorporated. Permission is granted to use the VadaTech custom VHDL code royalty-free in customer designs targeting the VadaTech AMC511 card only. Redistribution to third parties or use of this code for any other purpose is strictly prohibited.

It is possible to make slight changes to the design such as replacing the provided half-band FIR filter with your own custom FIR filter, etc or to completely replace the design. At a minimum the UCF file will be a useful starting point since it captures the pin-out of the FPGA chip on the AMC511 card. The provided source files were used to create the flash image that is shipped on the board from VadaTech. The MCS file used is also included so that the original BPI flash contents can be replaced after experimentation to restore the original board functionality.

A Xilinx Platform Cable USB II (or other compatible JTAG probe) is required to program the FPGA and/or BPI flash. During development it is possible to save time by only programming the FPGA. However, with a PCIe-based design it is required to soft-reset the system in order for the PCIe core to get re-initialized by the CPU. Doing a hard-reset will load the contents of the BPI flash and will wipe out any previous FPGA configuration that may have been done via JTAG. There is no special switch to select BPI vs. JTAG mode, the board is always in BPI mode but the JTAG can reconfigure the FPGA at any time. So the usual development sequences would be:

Developing using BPI Flash to load the FPGA:

- 1) Power the system (FPGA will load whatever is already in BPI flash)

- 2) Program the BPI flash with the MCS file

- 3) Power-cycle the system

Developing using FPGA only:

- 1) Power the system (FPGA will load whatever is already in BPI flash)

- 2) Program the FPGA with the BIT file (previous configuration will be overwritten for current power-cycle only)

- 3) Soft-reset the system (i.e. CTRL-ALT-DELETE or 'reboot' Linux command) to cause the PCIe BARs to be re-detected/re-initialized.

VadaTech is not responsible for damage or loss caused by reprogramming of the FPGA or BPI Flash by the customer. Use caution when changing the reference design or creating your own design as it is possible to damage the board or components.

# Customizing the VCXO / Ref Clock Configuration

The AMC511 reference design code ships out with a default VCXO (A/D sample clock) rate of 180 MHz and a default Ref Clock rate of 10 MHz. However, these parts (Y4 and Y3 respectively on the schematic) may be changed out by Vadatech at the customer's request to better suit their target application.

To help facilitate this board-level change there are conditional compile options in both the reference FPGA code and the device driver code. These conditional compile options change the N/M divider configuration in the clock synchronizer PLL (refer to the **SYNCSPIO** register in the following section). Using incorrect settings will prevent the PLL from locking and may result in an unstable A/D sample clock.

The following configurations are currently supported by the reference design. If your application requires a different combination of oscillators please contact VadaTech Sales.

| VCXO (Y4)  | Ref Clock (Y3) | N Divider | M Divider |

|------------|----------------|-----------|-----------|

| 180 MHz    | 10 MHz         | 990       | 55        |

| 107.52 MHz | 10 MHz         | 1344      | 125       |

Table 12: Supported VCXO / Ref Clock frequencies

To change the hardware default N/M configuration which the FPGA applies immediately upon configuration, look for the following compile options in the FPGA VHDL reference design's **clksync\_core.vhd** file and set exactly one of them to 1 and the other to 0 and then re-generate the programming file:

| constant VCXO180_REF10    | : | <pre>integer range 0 to 1 := 1;</pre> |  |

|---------------------------|---|---------------------------------------|--|

| constant VCXO107_52_REF10 |   | <pre>integer range 0 to 1 := 0;</pre> |  |

To change the device driver's card initialization values, edit the device driver's **amc511.c** file and look for the following compile options and set exactly one of them to 1 and the other to 0 then rebuild the driver:

| #define | VCXO180_REF10    | 1 |

|---------|------------------|---|

| #define | VCX0107_52_REF10 | 0 |

It is recommended that both the FPGA and device driver defaults be changed to match the oscillator configuration of your particular board. However, if changing the FPGA is not practical then just changing the device driver should be sufficient since it overrides the FPGA defaults prior to any actual data acquisition.

# 8 Appendix A: FPGA Register Specification

The AMC511 Reference Design FPGA's registers are available via a PCIe 64KB nonprefetchable memory-mapped region (BAR 0). This region responds to byte-enabled 32-bit memory reads and writes; meaning that BYTE, WORD, and DWORD accesses are permitted. The layout of this region is shown below:

| Core                 | BAR Offset      | Mnemonic    | Description                           |

|----------------------|-----------------|-------------|---------------------------------------|

| Interrupt Controller | 0x0000          | GIMSR       | Global Interrupt Mask Set Register    |

|                      | 0x0004          | GIMCR       | Global Interrupt Mask Clear Register  |

|                      | 0x0008          | GISR        | Global Interrupt Status Register      |

|                      | 0x000C          | BCSR        | Bit-Change Status Register            |

|                      | 0x0010 - 0x0FFF | N/A         | Reserved                              |

| A/D Channel 0        | 0x1000          | CHCTRLO     | Channel O Control Register            |

|                      | 0x1004          | CHSTATO     | Channel O Status Register             |

|                      | 0x1008          | CHMASKO     | Channel O Mask Register               |

|                      | 0x100C          | CHHWMO      | Channel O High Water Mark Register    |

|                      | 0x1010          | CHLVLO      | Channel O Level Register              |

|                      | 0x1014          | CHDMACTRLO  | Channel O DMA Control/Status Register |

|                      | 0x1018          | CHDMACOUNTO | Channel O DMA Count Register          |

|                      | 0x101C          | CHDEBUGAO   | Channel O Debug Register A            |

|                      | 0x1020          | CHDEBUGBO   | Channel O Debug Register B            |

|                      | 0x1024          | CHDEBUGCO   | Channel O Debug Register C            |