User Manual, V 1.0, Nov. 2005

# CIC751 Companion IC

Microcontrollers

Never stop thinking

Edition 2005-11 Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2005. All Rights Reserved.

#### **Attention please!**

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# CIC751 Companion IC

# Microcontrollers

Never stop thinking

| CIC751<br>CONFID<br>Revisior | ENTIAL<br>h History: | 2005-11                             | V 1.0 |

|------------------------------|----------------------|-------------------------------------|-------|

| Previous Version:            |                      | None.                               |       |

| Page                         | Subjects             | (major changes since last revision) |       |

|                              |                      |                                     |       |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

| <b>1</b><br>1.1<br>1.2 | Introduction       1-         Overview       1-         Features       1- | 1 |

|------------------------|---------------------------------------------------------------------------|---|

| 1.2.1                  | Detailed Features 1-:                                                     | 2 |

| 1.2.1.1                | ADC 1-:                                                                   | 3 |

| 1.2.1.2                | MLI                                                                       | 4 |

| 1.2.1.3                | SSC 1                                                                     | 4 |

| 1.3                    | Signal Description 1-                                                     | 5 |

| 2                      | System and Control Unit (SCU)                                             | 1 |

| 2.1                    | Reset Control Block 2-                                                    | 1 |

| 2.1.1                  | Power-On Reset                                                            | 1 |

| 2.1.2                  | Embedded Voltage Regulator (EVR) Reset                                    | 1 |

| 2.2                    | Mode Selection                                                            | 1 |

| 2.2.1                  | MODE Pin                                                                  | 2 |

| 2.2.2                  | TESTMODE Pin                                                              | 2 |

| 2.3                    | Clock System                                                              | 2 |

| 2.3.1                  | Overview                                                                  | 2 |

| 2.3.2                  | Clock Generation Unit 2-2                                                 | 2 |

| 2.3.2.1                | RC Oscillator Circuit (RCOSC) 2-                                          | 3 |

| 2.3.2.2                | Phase-Locked Loop (PLL) Module 2-4                                        | 4 |

| 2.3.2.3                | Clock Control Unit                                                        |   |

| 2.4                    | Power Supply System 2-1                                                   | 0 |

| 2.4.1                  | Embedded Voltage Regulator 2-1                                            | 1 |

| 2.5                    | Event Control                                                             | 1 |

| 2.5.1                  | Event Sources 2-1                                                         | 1 |

| 2.5.2                  | External Trigger Inputs 2-1                                               | 1 |

| 2.5.3                  | Event Output Structure 2-12                                               | 2 |

| 2.5.3.1                | Service Request Routing 2-1                                               | 3 |

| 2.6                    | SCU Registers 2-14                                                        | 4 |

| 2.6.1                  | Clock Control Registers 2-14                                              | 4 |

| 2.6.2                  | Miscellaneous SCU Registers 2-1                                           | 6 |

| 2.7                    | SCU Register Overview 2-2-                                                | 4 |

| 3                      | Direct Memory Access Controller                                           | 1 |

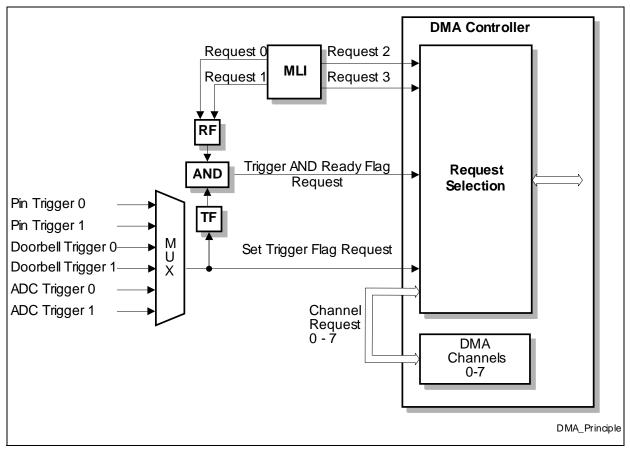

| 3.1                    | DMA Request Generation and Control                                        | 1 |

| 3.1.1                  | Request Generation 3-                                                     | 1 |

| 3.1.1.1                | Preselection of the Indirect Requests                                     | 2 |

| 3.1.2                  | DMA Request Assignment Matrix 3-                                          | 4 |

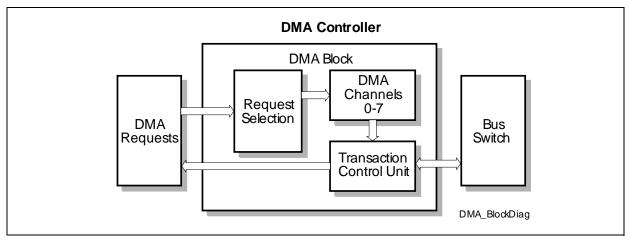

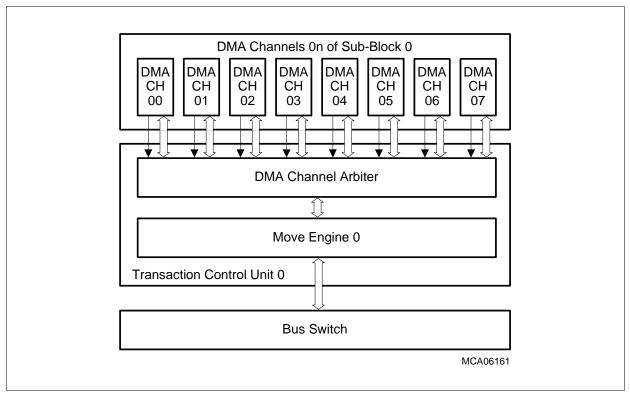

| 3.2                    | DMA Controller Kernel Description 3-                                      | 8 |

| 3.2.1                  | Features                                                                  | 9 |

| 3.2.2                  | Definition of Terms 3-1                                                   | 0 |

| 3.2.3<br>3.2.4<br>3.2.4.1<br>3.2.4.2 | DMA Principles       DMA Channel Functionality         DMA Channel Functionality       Shadowed Source or Destination Address         DMA Channel Request Control       DMA Channel Request Control | 3-12<br>3-12 |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 3.2.4.3                              | DMA Channel Operation Modes                                                                                                                                                                         | 3-16         |

| 3.2.4.4                              | Channel Reset Operation                                                                                                                                                                             | 3-20         |

| 3.2.4.5                              | Transfer Count and Move Count                                                                                                                                                                       | 3-22         |

| 3.2.4.6                              | Circular Buffer                                                                                                                                                                                     | 3-24         |

| 3.2.5                                |                                                                                                                                                                                                     | 3-25         |

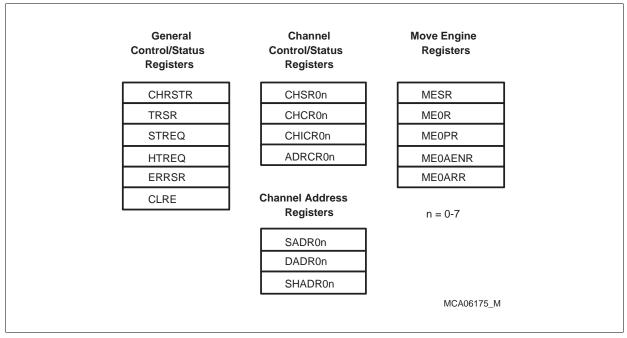

| 3.3                                  | DMA Module Kernel Registers                                                                                                                                                                         |              |

| 3.3.1                                | General Control/Status Registers                                                                                                                                                                    | 3-28         |

| 3.3.2                                | Move Engine Registers                                                                                                                                                                               | 3-37         |

| 3.3.3                                | Channel Control/Status Registers                                                                                                                                                                    |              |

| 3.3.4                                | Channel Address Registers                                                                                                                                                                           |              |

|                                      | -                                                                                                                                                                                                   |              |

| 4                                    | Micro Link Interface (MLI)                                                                                                                                                                          |              |

| 4.1                                  | MLI Protocol                                                                                                                                                                                        |              |

| 4.1.1                                |                                                                                                                                                                                                     |              |

| 4.1.2                                | MLI Specific Terms                                                                                                                                                                                  |              |

| 4.1.3                                | MLI Communication Principles                                                                                                                                                                        |              |

| 4.1.4                                | MLI Frame Types                                                                                                                                                                                     |              |

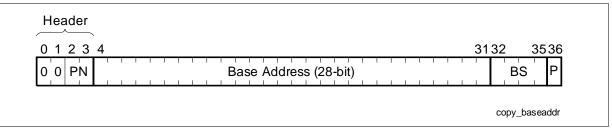

| 4.1.4.1                              | Copy Base Address Frame                                                                                                                                                                             |              |

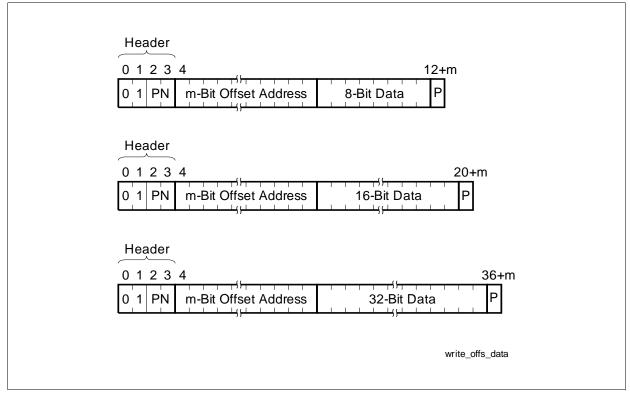

| 4.1.4.2                              | Write Offset and Data Frame                                                                                                                                                                         |              |

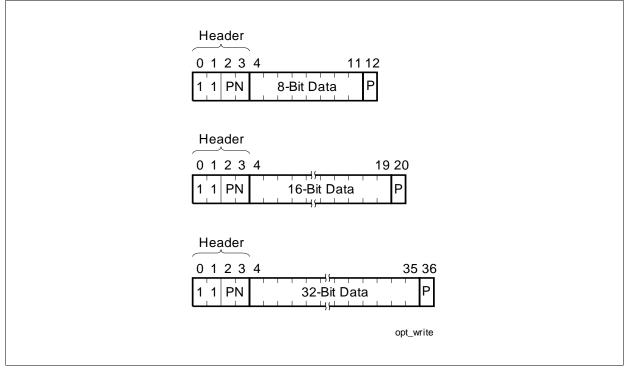

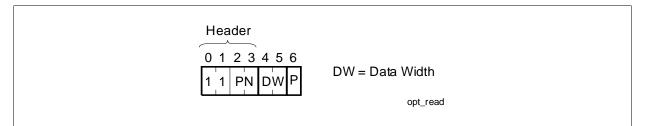

| 4.1.4.3                              | Optimized Write Frame                                                                                                                                                                               | 4-10         |

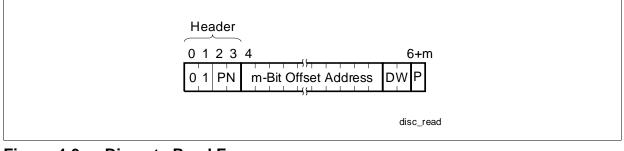

| 4.1.4.4                              | Discrete Read Frame                                                                                                                                                                                 | 4-11         |

| 4.1.4.5                              | Optimized Read Frame                                                                                                                                                                                | 4-12         |

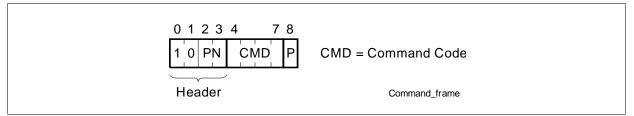

| 4.1.4.6                              |                                                                                                                                                                                                     | 4-13         |

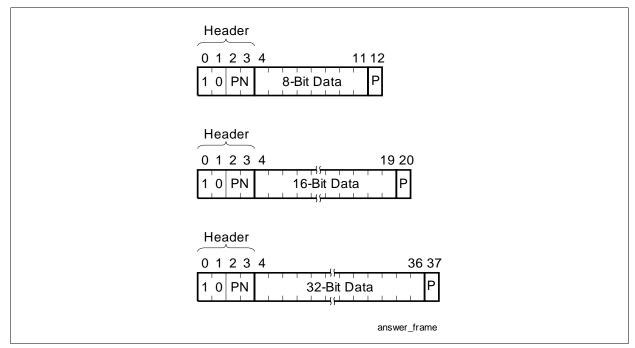

| 4.1.4.7                              | Answer Frame                                                                                                                                                                                        | 4-14         |

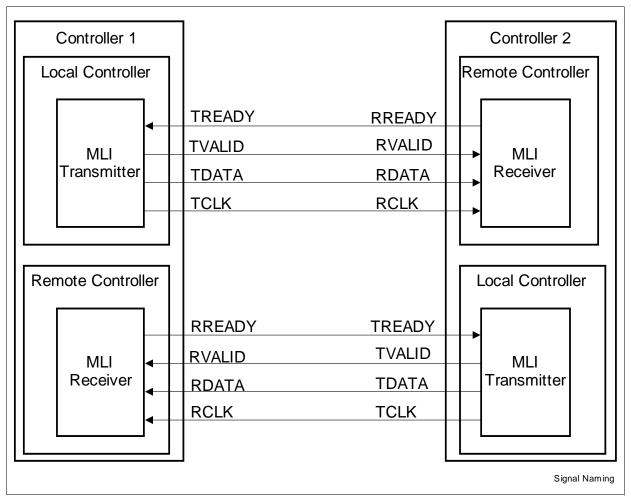

| 4.1.5                                | Naming Conventions                                                                                                                                                                                  | 4-15         |

| 4.1.6                                | MLI Communication Examples                                                                                                                                                                          | 4-15         |

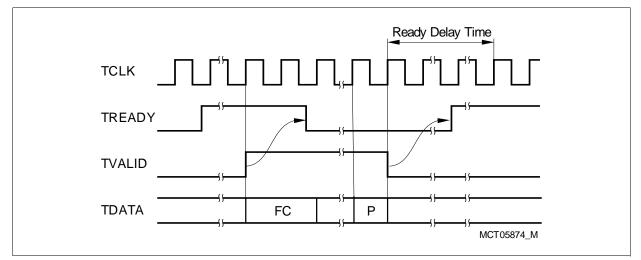

| 4.1.6.1                              | Ready Delay Time                                                                                                                                                                                    | 4-16         |

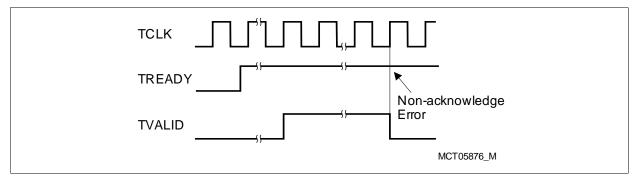

| 4.1.6.2                              | Non-Acknowledge Error                                                                                                                                                                               |              |

| 4.1.7                                | Parity Generation                                                                                                                                                                                   | 4-17         |

| 4.1.8                                | Address Prediction                                                                                                                                                                                  | 4-17         |

| 4.2                                  |                                                                                                                                                                                                     | 4-19         |

| 4.2.1                                | Frame Handling                                                                                                                                                                                      | 4-19         |

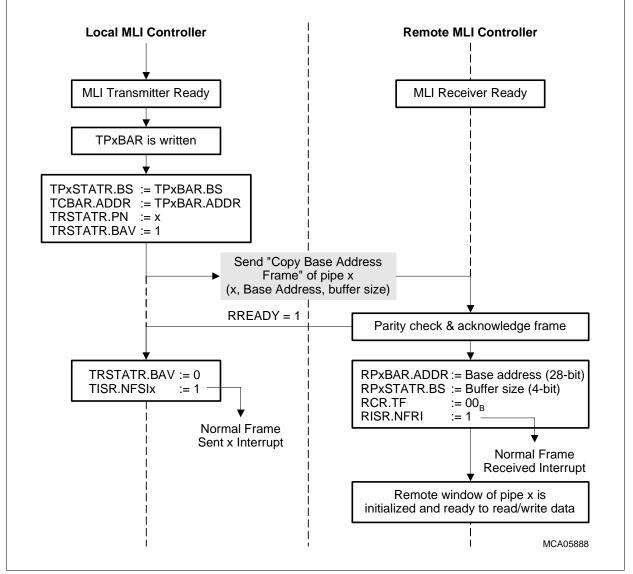

| 4.2.1.1                              | Copy Base Address Frame                                                                                                                                                                             | 4-19         |

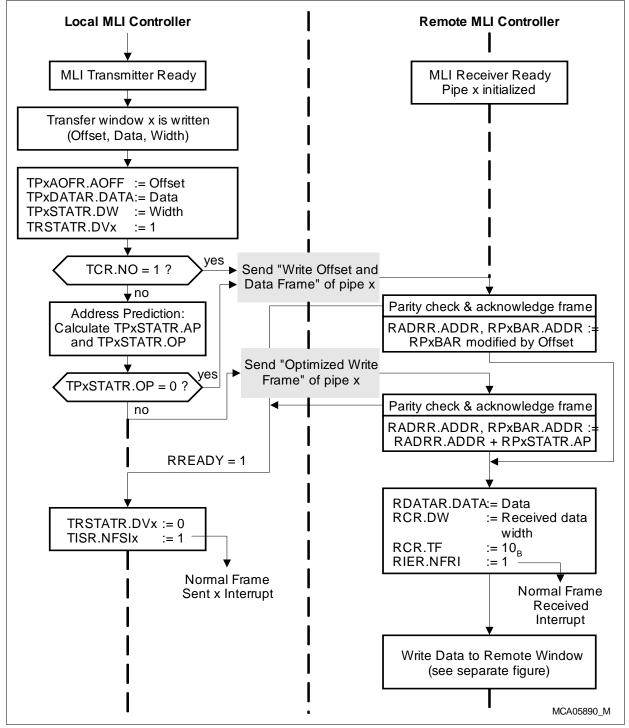

| 4.2.1.2                              | Data Frames                                                                                                                                                                                         | 4-22         |

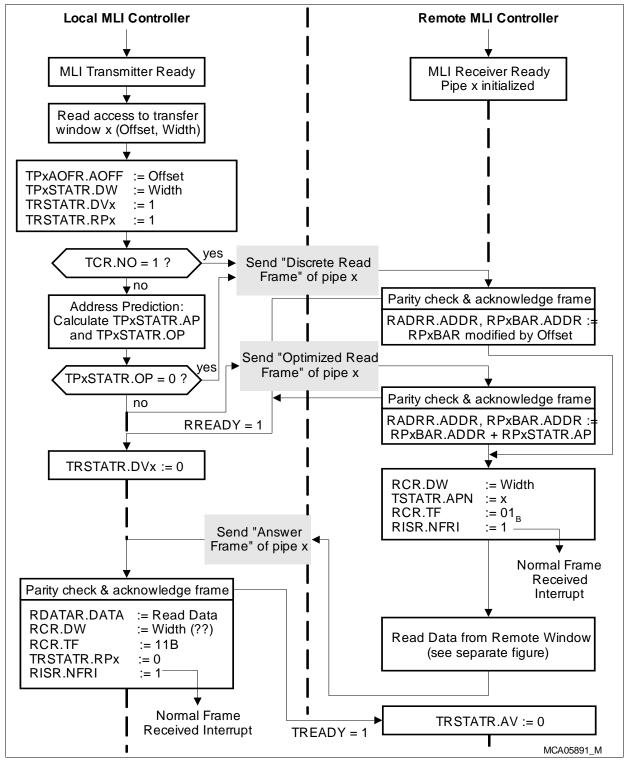

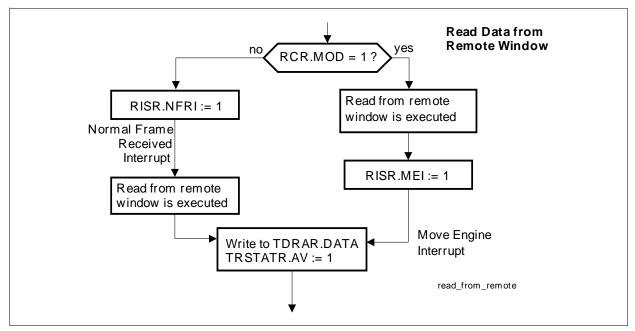

| 4.2.1.3                              | Read Frames                                                                                                                                                                                         | 4-26         |

| 4.2.1.4                              | Answer Frame                                                                                                                                                                                        | 4-29         |

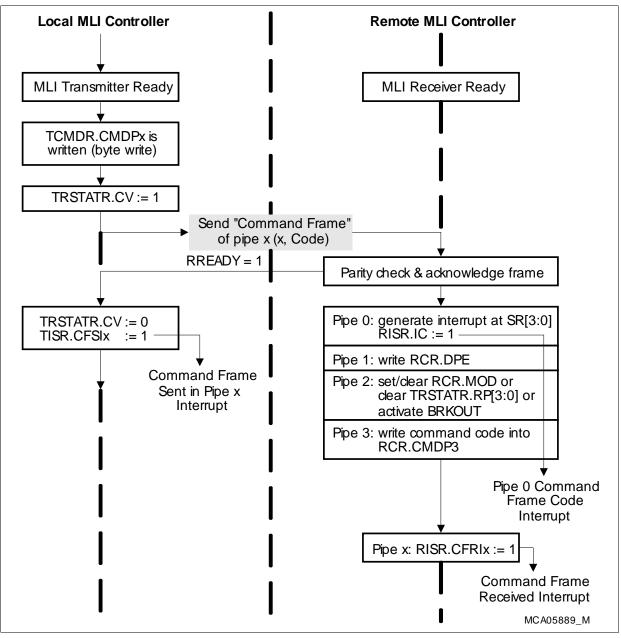

| 4.2.1.5                              |                                                                                                                                                                                                     | 4-30         |

| 4.2.2                                | General MLI Features                                                                                                                                                                                | 4-34         |

| 4.2.2.1                              | Parity Generation and Checking                                                                                                                                                                      | 4-34         |

| 4.2.2.2  | Non-Acknowledge Error                                  | 4-37 |

|----------|--------------------------------------------------------|------|

| 4.2.2.3  | Address Prediction                                     | 4-38 |

| 4.2.2.4  | Automatic Data Mode                                    | 4-39 |

| 4.2.2.5  | Transmit Priority                                      | 4-39 |

| 4.2.3    | MLI Interface Control                                  | 4-40 |

| 4.2.4    | MLI Request Generation                                 | 4-41 |

| 4.2.5    | Transmitter Interrupts                                 | 4-41 |

| 4.2.5.1  | Parity/Time-out Error Interrupt                        | 4-43 |

| 4.2.5.2  | Normal Frame Sent x Interrupt                          | 4-43 |

| 4.2.5.3  | Command Frame Sent Interrupt                           | 4-43 |

| 4.2.6    | Receiver Interrupts                                    | 4-43 |

| 4.2.6.1  | Discarded Read Answer Interrupt                        | 4-43 |

| 4.2.6.2  | Parity Error Interrupt                                 | 4-44 |

| 4.2.6.3  | Normal Frame Received/Move Engine Terminated Interrupt | 4-44 |

| 4.2.6.4  | Interrupt Command Frame Interrupt                      | 4-44 |

| 4.2.6.5  | Command Frame Received Interrupt                       | 4-44 |

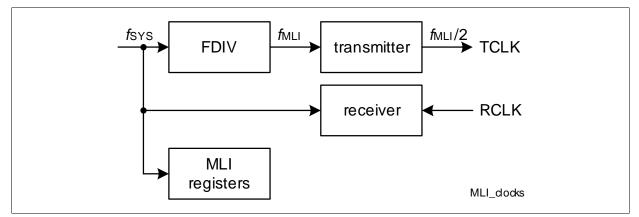

| 4.2.7    | Baud Rate Generation                                   | 4-45 |

| 4.3      | MLI Kernel Registers                                   | 4-47 |

| 4.3.1    | General Registers                                      | 4-49 |

| 4.3.1.1  | Fractional Divider Register                            | 4-49 |

| 4.3.1.2  | Set Clear Register                                     | 4-51 |

| 4.3.1.3  | Global Interrupt Set Register                          | 4-53 |

| 4.3.1.4  | Output Input Control Register                          | 4-54 |

| 4.3.2    | MLI Transmitter Registers                              | 4-59 |

| 4.3.2.1  | Transmitter Control Register                           | 4-59 |

| 4.3.2.2  | Transmitter Status Register                            | 4-62 |

| 4.3.2.3  | Transmitter Pipe x Status Registers                    | 4-64 |

| 4.3.2.4  | Transmitter Command Register                           | 4-66 |

| 4.3.2.5  | Transmitter-Receiver Status Register                   | 4-68 |

| 4.3.2.6  | Transmitter Pipe x Address Offset Register             | 4-70 |

| 4.3.2.7  | Transmitter Pipe x Data Register                       | 4-71 |

| 4.3.2.8  | Transmitter Data Read Answer Register                  | 4-72 |

| 4.3.2.9  | Transmitter Pipe x Base Address Register               | 4-73 |

| 4.3.2.10 | Transmitter Copy Base Address Register                 | 4-74 |

| 4.3.3    | MLI Receiver Registers                                 | 4-75 |

| 4.3.3.1  | Receiver Control Register                              | 4-75 |

| 4.3.3.2  | Receiver Pipe x Base Address Register                  | 4-78 |

| 4.3.3.3  | Receiver Pipe x Status Register                        | 4-79 |

| 4.3.3.4  | Receiver Address Register                              | 4-81 |

| 4.3.3.5  | Receiver Data Register                                 | 4-82 |

| 4.3.4    | Transmitter Interrupt Registers                        | 4-83 |

| 4.3.4.1  | Transmitter Interrupt Enable Register                  | 4-83 |

| 4.3.4.2  | Transmitter Interrupt Register                         | 4-85 |

| 4.3.4.3<br>4.3.5<br>4.3.5.1<br>4.3.5.2<br>4.3.5.3 | Transmitter Interrupt Node Pointer Register          Receiver Interrupt Registers          Receiver Interrupt Enable Register          Receiver Interrupt Status Register          Receiver Interrupt Node Pointer Register | 4-86<br>4-88<br>4-88<br>4-90<br>4-92 |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 4.4                                               | MLI Address Map                                                                                                                                                                                                             | 4-94                                 |

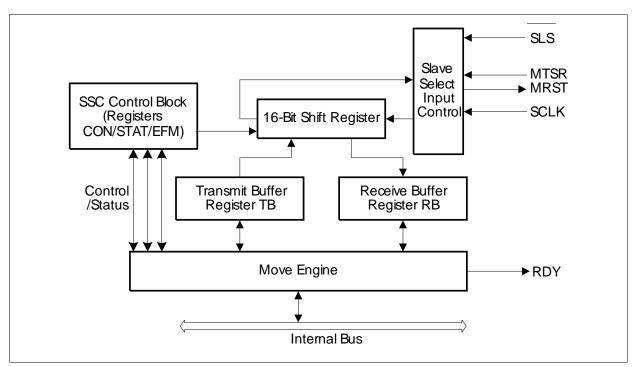

| 5                                                 | Synchronous Serial Interface (SSC)                                                                                                                                                                                          |                                      |

| 5.1                                               | Overview                                                                                                                                                                                                                    |                                      |

| 5.2                                               | General Operation                                                                                                                                                                                                           |                                      |

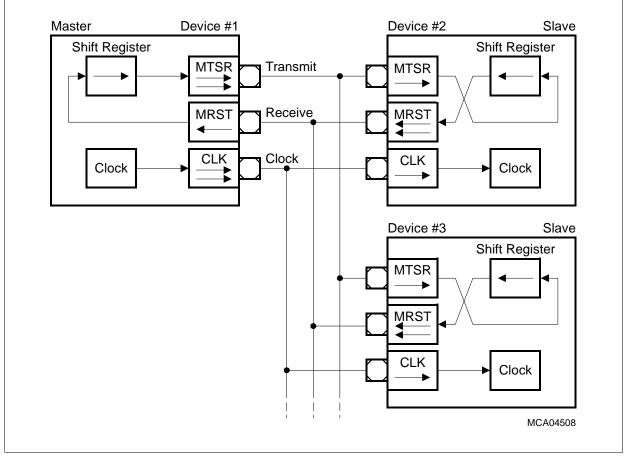

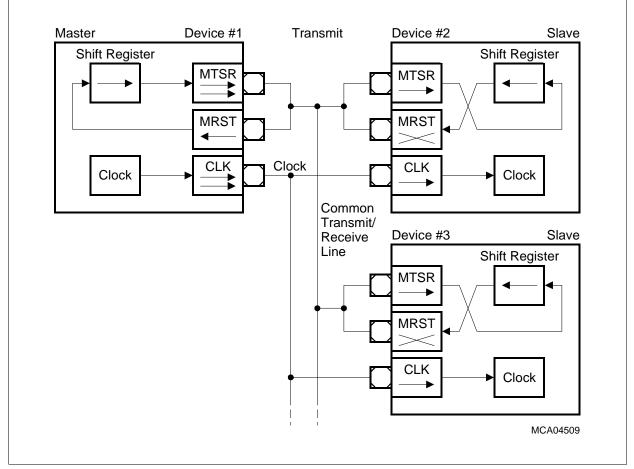

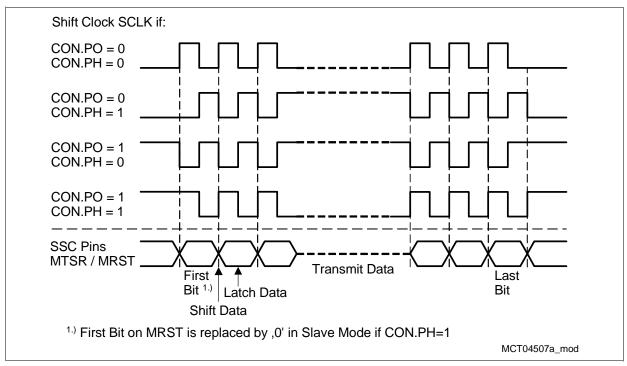

| 5.2.1                                             | SPI Communication Basics                                                                                                                                                                                                    |                                      |

| 5.2.1.1                                           | Full-Duplex Operation                                                                                                                                                                                                       |                                      |

| 5.2.1.2                                           | Half-Duplex Operation                                                                                                                                                                                                       |                                      |

| 5.2.2                                             | Operating the SSC                                                                                                                                                                                                           | . 5-8                                |

| 5.2.2.1                                           | SSC Transaction Header                                                                                                                                                                                                      |                                      |

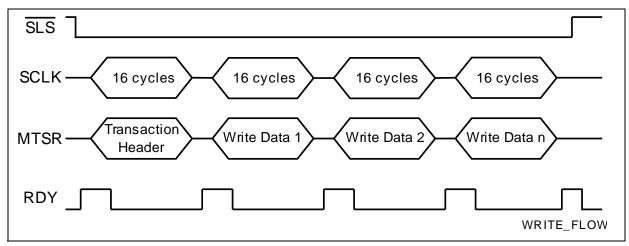

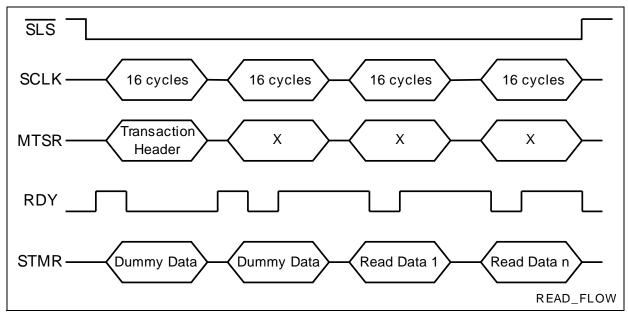

| 5.2.2.2                                           | SSC Data Flow Model                                                                                                                                                                                                         | . 5-9                                |

| 5.2.3                                             | Operating Mode Selection                                                                                                                                                                                                    | 5-13                                 |

| 5.2.4                                             | Error Detection Mechanisms                                                                                                                                                                                                  | 5-14                                 |

| 5.3                                               | Register Descriptions                                                                                                                                                                                                       | 5-15                                 |

| 5.4                                               | Port Control                                                                                                                                                                                                                | 5-23                                 |

| 5.4.1                                             | Connecting 2 or more CIC751 SSC Slaves to 1 Host                                                                                                                                                                            | 5-23                                 |

| 6                                                 | The Analog/Digital Converter                                                                                                                                                                                                | . 6-1                                |

| 6.1                                               | Mode Selection                                                                                                                                                                                                              | 6-3                                  |

| 6.1.1                                             | Compatibility Mode                                                                                                                                                                                                          | 6-3                                  |

| 6.1.2                                             | Enhanced Mode                                                                                                                                                                                                               | 6-3                                  |

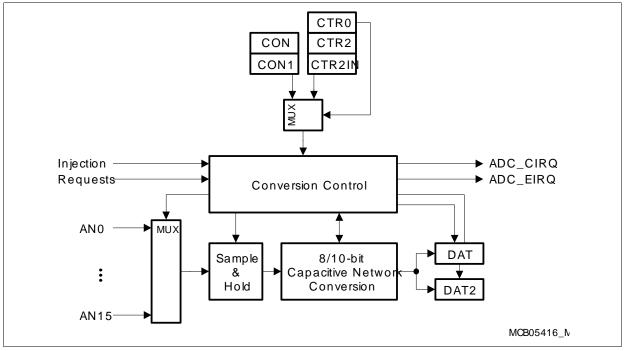

| 6.2                                               | ADC Operation                                                                                                                                                                                                               | . 6-4                                |

| 6.2.1                                             | Channel Selection                                                                                                                                                                                                           | 6-4                                  |

| 6.2.2                                             | ADC Status Flags                                                                                                                                                                                                            | 6-4                                  |

| 6.2.3                                             | ADC Start/Stop Control                                                                                                                                                                                                      | 6-4                                  |

| 6.2.4                                             | Conversion Mode Selection                                                                                                                                                                                                   |                                      |

| 6.2.5                                             | Conversion Resolution Control                                                                                                                                                                                               | . 6-6                                |

| 6.2.5.1                                           | Conversion Result                                                                                                                                                                                                           | . 6-6                                |

| 6.2.6                                             | Fixed Channel Conversion Modes                                                                                                                                                                                              | 6-6                                  |

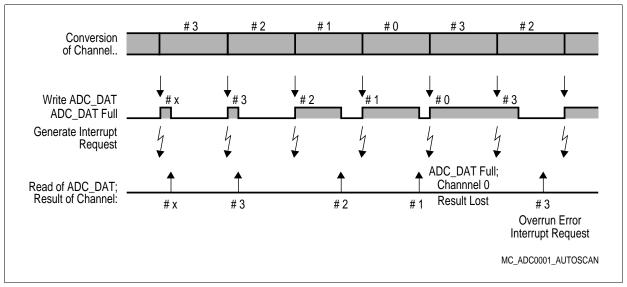

| 6.2.7                                             | Auto Scan Conversion Modes                                                                                                                                                                                                  | 6-6                                  |

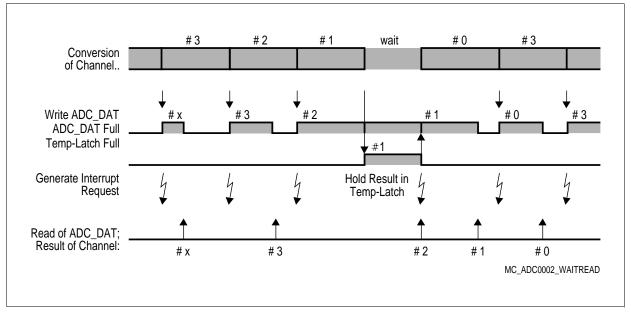

| 6.2.8                                             | Wait for Read Mode                                                                                                                                                                                                          |                                      |

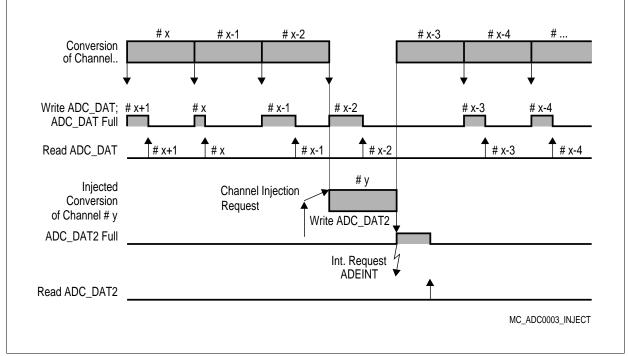

| 6.2.9                                             | Channel Injection Mode                                                                                                                                                                                                      |                                      |

| 6.2.10                                            | Arbitration of Conversions                                                                                                                                                                                                  |                                      |

| 6.3                                               | Automatic Calibration                                                                                                                                                                                                       | 6-11                                 |

| 6.4                                               | Multiplexer Test Mode                                                                                                                                                                                                       | 6-11                                 |

| 6.5                                               | Conversion Timing Control                                                                                                                                                                                                   | 6-12                                 |

| 6.6                                               | A/D Converter Interrupt Operation                                                                                                                                                                                           | 6-15                                 |

| 6.6.1                                             | Interrupt Event Handling                                                                                                                                                                                                    | 6-15                                 |

| 6.6.1.1                                           | Trigger an DMA Action                                                                                                                                                                                                       | 6-15                                 |

| 0.0.1.1                                           |                                                                                                                                                                                                                             | 0 10                                 |

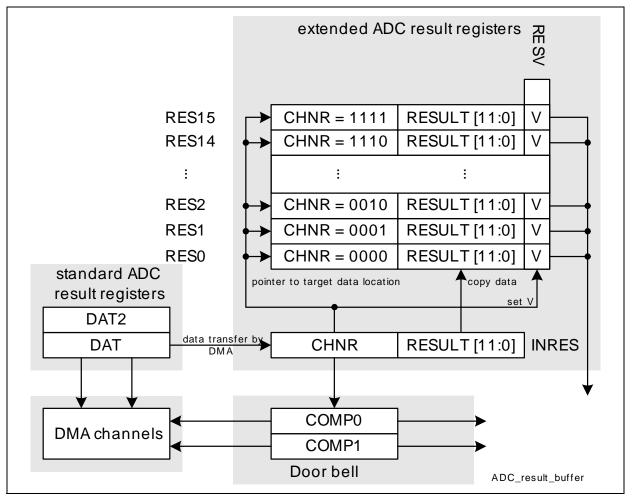

| 6.6.1.2<br>6.7<br>6.7.1<br>6.7.2<br>6.7.3<br>6.7.3.1<br>6.7.3.2<br>6.8<br>6.8.1<br>6.8.2<br>6.8.3<br>6.8.4<br>6.8.5 | Forward to an SRn Pin<br>ADC Buffer Registers<br>Overview<br>Extended Result Registers<br>Doorbell Mechanism<br>Trigger an DMA Transfer<br>Stimulate SRn Pins<br>ADC Registers<br>ADC Control Registers for Compatibility Mode<br>ADC Control Registers for Enhanced Mode<br>ADC Result Registers<br>ADC Result Registers<br>ADC Extended Result Registers<br>ADC Doorbell Register | 6-16 |

|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 7                                                                                                                   | Parallel Ports                                                                                                                                                                                                                                                                                                                                                                      | 7_1  |

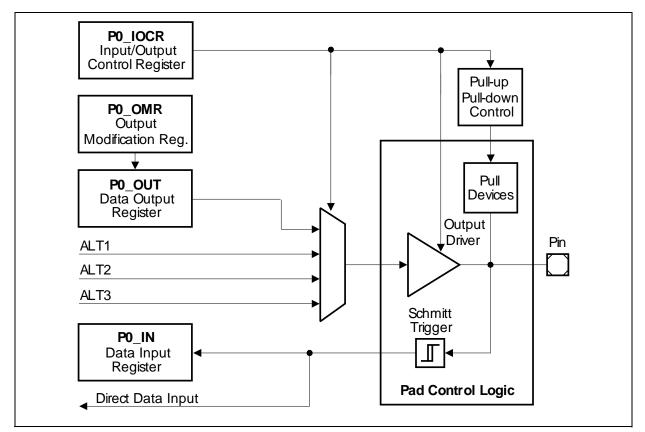

| 7.1                                                                                                                 | Port 0                                                                                                                                                                                                                                                                                                                                                                              |      |

| 7.1.1                                                                                                               | Block Diagram                                                                                                                                                                                                                                                                                                                                                                       |      |

| 7.1.2                                                                                                               | Input Stage                                                                                                                                                                                                                                                                                                                                                                         |      |

| 7.1.3                                                                                                               | Port 0 Routing                                                                                                                                                                                                                                                                                                                                                                      |      |

| 7.1.4                                                                                                               | Port 0 Register Description                                                                                                                                                                                                                                                                                                                                                         |      |

| 7.1.4.1                                                                                                             | Port 0 Control Register                                                                                                                                                                                                                                                                                                                                                             |      |

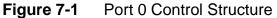

| 7.2                                                                                                                 | Port 1                                                                                                                                                                                                                                                                                                                                                                              |      |

| 7.2.1                                                                                                               | Block Diagram                                                                                                                                                                                                                                                                                                                                                                       | 7-13 |

| 7.2.2                                                                                                               | Input Stage                                                                                                                                                                                                                                                                                                                                                                         | 7-13 |

| 7.2.3                                                                                                               | Port 1 Routing                                                                                                                                                                                                                                                                                                                                                                      | 7-14 |

| 7.2.4                                                                                                               | Port 1 Register Description                                                                                                                                                                                                                                                                                                                                                         | 7-15 |

| 7.2.4.1                                                                                                             | Port Input Register                                                                                                                                                                                                                                                                                                                                                                 | 7-15 |

| 7.3                                                                                                                 | Ports Register Overview                                                                                                                                                                                                                                                                                                                                                             | 7-15 |

| 8                                                                                                                   | Register Overview                                                                                                                                                                                                                                                                                                                                                                   | 8-1  |

| 8.1                                                                                                                 | Address Map of CIC751                                                                                                                                                                                                                                                                                                                                                               |      |

| 8.1.1                                                                                                               | Access Rules                                                                                                                                                                                                                                                                                                                                                                        |      |

| 8.2                                                                                                                 | Registers Tables                                                                                                                                                                                                                                                                                                                                                                    |      |

| 8.3                                                                                                                 | Memory Registers                                                                                                                                                                                                                                                                                                                                                                    | 8-15 |

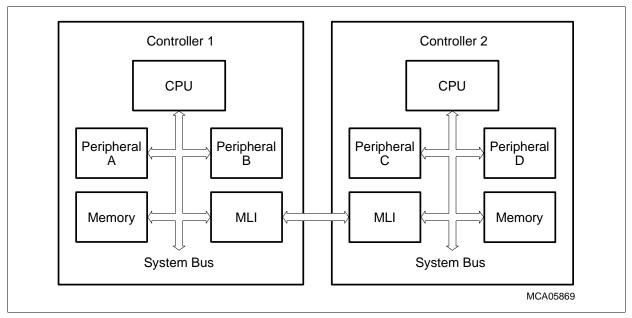

## 1 Introduction

The CIC751 is a companion IC for the Infineon AUDO-NG family of 32-bit microcontrollers. The major function of the CIC751 is to provide the AUDO-NG 32-bit microcontrollers with the capability of a 5 V Analog to Digital Converter (ADC). The interconnection of the CIC751 and the microcontroller is accomplished via either the Micro Link Interface (MLI) or the Synchronous Serial Interface (SSC). Internal operations of the CIC751 are supported by the very flexible on-chip DMA controller.

#### 1.1 Overview

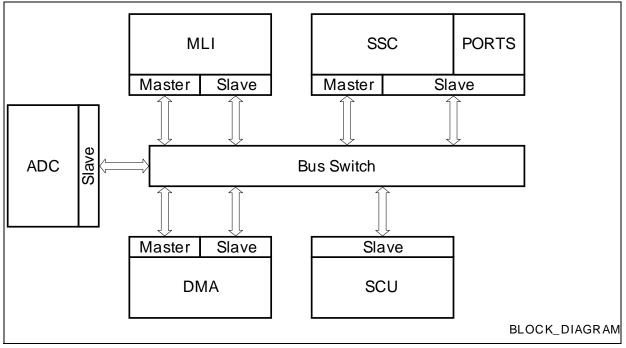

**Figure 1-1** provides the block diagram of the CIC751 companion chip. This design allows access to the ADC by the host CPU without sacrificing any of the features of the ADC. This can be achieved because all registers of the ADC are mapped to the on-chip bus. This bus can be accessed via one of the two serial interfaces. Selection of the interface is made via pin MODE, which can be directly connected to the supply voltage or via pull-up/down resistors.

The bus domain is completely separated from the address domain on the CPU chip. The addresses of all modules on the companion chip are 32-bit addresses. Transactions between the CPU and the SSC are executed with the SSC transmission protocol; transactions between the MLI and the CPU use the MLI transmission protocol.

Each transaction via any of the two serial interfaces is defined by address, data, data width, and type of frame. The address from which data is read or written to, is related to the address domain. The data width may be 8, 16 or 32 bits for the MLI and 16 bits for the SSC. The ADC and the MLI may send request triggers to the DMA Controller.

Figure 1-1 CIC751 Block Diagram

#### 1.2 Features

This section provides a high-level description of the features on the CIC751.

- 5 V Analog to Digital Converter

- 16 analog input channels

- Internal low power oscillator

- Slave (SPI) SSC interface operating on 5 V or 3.3 V

- MLI Interface operating on 5 V or 3.3 V

- Maximum system frequency of 40 MHz

- Low-power design

- Single power supply concept design (for pad and core supply)

- Seperated ADC supply

- Input and output pins with 3.3 V and 5.0 V

- Flexible clocking concept

- Crossbar bus architecture

## 1.2.1 Detailed Features

The following sections provide detailed information about each of the on-chip modules.

## 1.2.1.1 ADC

The CIC751 provides an Analog/Digital Converter with 8-bit or 10-bit resolution and a sample & hold circuit on-chip. An input multiplexer selects between up to 16 analog input channels either via software (Fixed Channel Modes) or automatically (Auto Scan Modes).

To fulfill most requirements of embedded control applications, the ADC supports the following conversion modes:

- Standard Conversions

- Fixed Channel Single Conversion

produces just one result from the selected channel

- Fixed Channel Continuous Conversion repeatedly converts the selected channel

- Auto Scan Single Conversion

produces one result from each of a selected group of channels

- Auto Scan Continuous Conversion repeatedly converts the selected group of channels

- Wait for Read Mode start a conversion automatically when the previous result was read

- **Channel Injection Mode** can insert the conversion of a specific channel into a group conversion (auto scan)

The key features of the ADC are:

- Use of Successive Approximation Method

- Integrated sample and hold functionality

- Analog Input Voltage Range from 0V to 5V

- 16 Analog Input Channels

- 16 ADC result registers

- Resolution:

8 Bit or 10 Bit in Compating

- 8-Bit or 10-Bit in Compatibility Mode

- Minimum Conversion Time: 2.55 µs @ 10-Bit

- Total Unadjusted Error (TUE):±1 LSB @ 8-Bit, ± 2 LSB @ 10-Bit

- Support of several Conversion Modes

Fixed Channel Single Conversion

Fixed Channel Continuous Conversion

Auto Scan Single Conversion

Auto Scan Continuous Conversion

Wait for Result Read and Start Next Conversion

Channel Injection during Group Conversion

- Programmable Conversion and Sample Timing Scheme

- Automatic Self-Calibration to changing temperatures or process variations

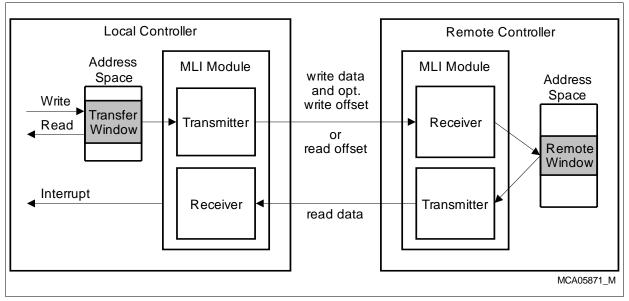

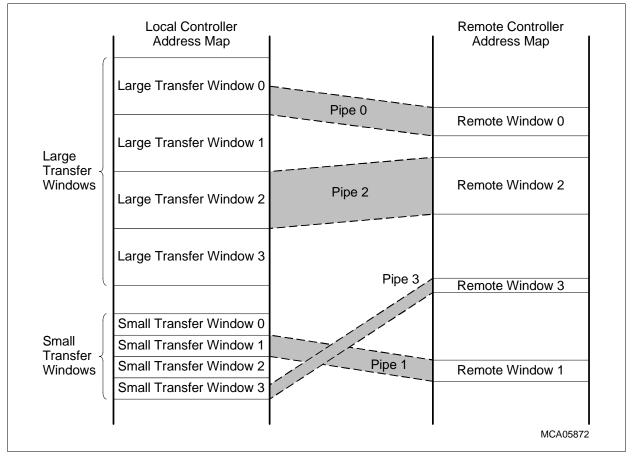

## 1.2.1.2 MLI

The Micro Link Interface (MLI) is a fast synchronous serial interface that makes it possible to exchange data between microcontrollers or other devices.

The key features of the MLI are:

- Synchronous serial communication between an MLI transmitter and an MLI receiver

- Different system clock speeds are supported in the MLI transmitter and MLI receiver due to full handshake protocol (4 lines between a transmitter and a receiver)

- Fully transparent read/write access is supported (= remote programming)

- Complete address range of target device (Remote Controller) is available

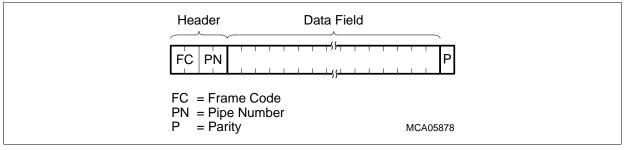

- Specific frame protocol to transfer commands, addresses, and data

- Error detection by parity bit

- 32-bit, 16-bit, or 8-bit data transfers are supported

- Programmable baud rate:  $f_{MLI}/2$  (max.:  $f_{MLI} = f_{SYS}$ )

- Multiple receiving devices are supported

## 1.2.1.3 SSC

The SSC supports full-duplex and half-duplex serial synchronous communication up to 10 Mbit/s (@ 40 MHz module clock). The serial clock signal is received from an external master (Slave Mode). Data width, shift direction, clock polarity, and phase are programmable. This allows communication with SPI-compatible devices. Transmission and reception of data is double-buffered. A shift clock generator provides the SSC with a separate serial clock signal.

This section describes only the use of the SSC module as a slave because the CIC751 always operates as a slave to a host.

#### Features

- Slave Mode operation

- Full-duplex or half-duplex operation

- Automatic pad control possible

- Flexible data format

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: Idle low or idle high state for the shift clock

- Programmable clock/data phase: Data shift with leading or trailing edge of the shift clock

- Internal Master Function

- Access to the all addresses

- Automatic address handling

- Automatic data handling

## 1.3 Signal Description

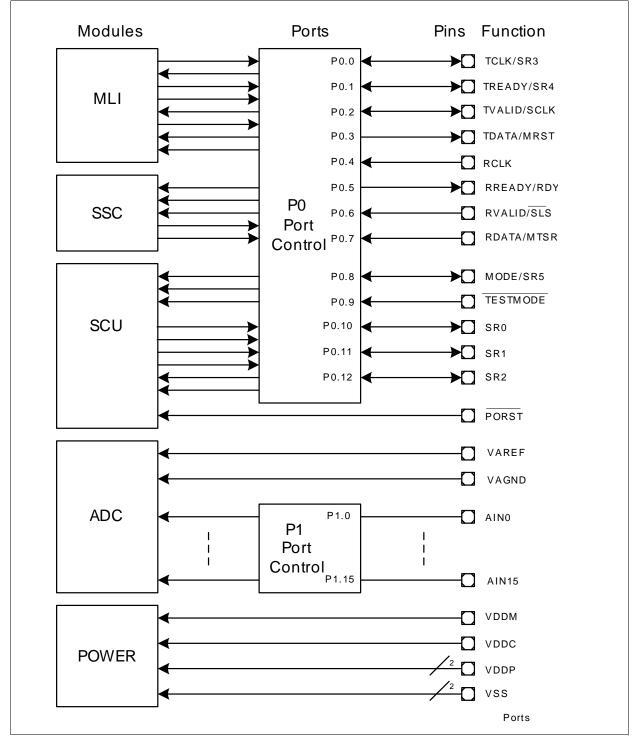

This section describes signals that connect off chip. **Table 1-1** gives a summery of the CIC751 external signals (pins).

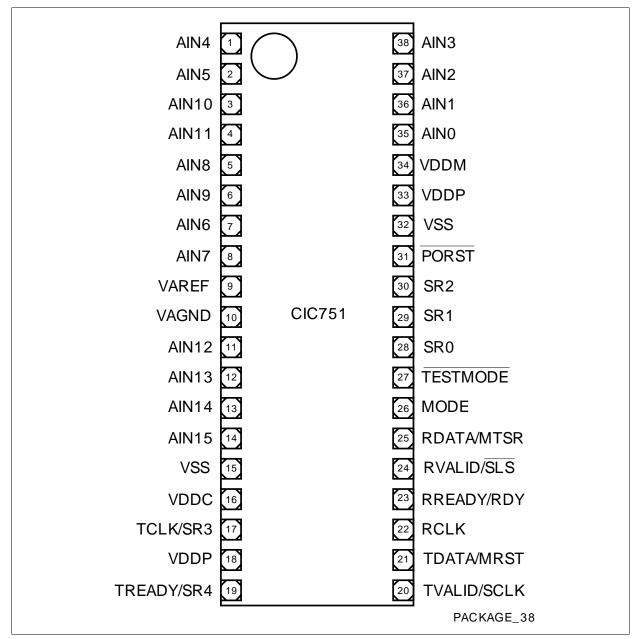

| Table 1-1 | Pin Definitio | a Functions |                                                                                    |

|-----------|---------------|-------------|------------------------------------------------------------------------------------|

| Symbol    | Pin/Port      | I/O         | Function                                                                           |

| AIN0      | 35<br>P1.0    | I           | Analog Input 0 <sup>1)</sup><br>For this pin a Multiplexer Test Mode is available. |

| AIN1      | 36<br>P1.1    | I           | Analog Input 1 <sup>1)</sup>                                                       |

| AIN2      | 37<br>P1.2    | I           | Analog Input 2 <sup>1)</sup>                                                       |

| AIN3      | 38<br>P1.3    | I           | Analog Input 3 <sup>1)</sup>                                                       |

| AIN4      | 1<br>P1.4     | I           | Analog Input 4 <sup>1)</sup>                                                       |

| AIN5      | 2<br>P1.5     | I           | Analog Input 5 <sup>1)</sup>                                                       |

| AIN6      | 7<br>P1.6     | I           | Analog Input 6 <sup>1)</sup>                                                       |

| AIN7      | 8<br>P1.7     | I           | Analog Input 7 <sup>1)</sup>                                                       |

| AIN8      | 5<br>P1.8     | I           | Analog Input 8 <sup>1)</sup>                                                       |

| AIN9      | 6<br>P1.9     | I           | Analog Input 9 <sup>1)</sup>                                                       |

| AIN10     | 3<br>P1.10    | I           | Analog Input 10 <sup>1)</sup>                                                      |

| AIN11     | 4<br>P1.11    | I           | Analog Input 11 <sup>1)</sup>                                                      |

| AIN12     | 11<br>P1.12   | I           | Analog Input 12 <sup>1)</sup>                                                      |

| AIN13     | 12<br>P1.13   | I           | Analog Input 13 <sup>1)</sup>                                                      |

| AIN14     | 13<br>P1.14   | I           | Analog Input 14 <sup>1)</sup>                                                      |

Table 1-1

Pin Definitions and Functions

## **CIC751**

## Introduction

| Symbol      | Pin/Port    | I/O | Function                                                                                        |

|-------------|-------------|-----|-------------------------------------------------------------------------------------------------|

| AIN15       | 14<br>P1.15 | I   | Analog Input 15 <sup>1)</sup>                                                                   |

| VAREF       | 9           | I   | Analog Reference Voltage                                                                        |

| VAGND       | 10          | I   | Analog Ground                                                                                   |

| TCLK/SR3    | 17<br>P0.0  | I/O | MODE = 0:<br>MLI Transmit Channel Clock Output<br>MODE = 1:<br>Event output line 3              |

| TREADY/SR4  | 19<br>P0.1  | I/O | MODE = 0:<br>MLI Transmit Channel Ready Input<br>MODE = 1:<br>Event request output line 4       |

| TVALID/SCLK | 20<br>P0.2  | I/O | MODE = 0:<br>MLI Transmit Channel Valid Output<br>MODE = 1:<br>SPI Serial Channel Clock         |

| TDATA/MRST  | 21<br>P0.3  | I/O | MODE = 0:<br>MLI Transmit Channel Data Output<br>MODE = 1:<br>SPI Master Receive Slave Transmit |

| RCLK        | 22<br>P0.4  | I/O | MODE = 0:<br>MLI Receive Channel Clock Input<br>MODE = 1:<br>GPIO                               |

| RREADY/RDY  | 23<br>P0.5  | I/O | MODE = 0:<br>MLI Receive Channel Ready Output<br>MODE = 1:<br>SSC Ready Signal                  |

| RVALID/SLS  | 24<br>P0.6  | I/O | MODE = 0:<br>MLI Receive Channel Valid Input<br>MODE = 1:<br>SSC Select Slave                   |

| RDATA/MTSR  | 25<br>P0.7  | I/O | MODE = 0:<br>MLI Receive Channel Data Input<br>MODE = 1:<br>SPI Master Transmit Slave Receive   |

## **CIC751**

#### Introduction

| Symbol                 | Pin/Port       | I/O                    | Function                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|------------------------|----------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MODE <sup>2)</sup>     | 26 I/O<br>P0.8 |                        | Interface Selection<br>Pin MODE selects whether the on-chip MLI or<br>SSC are used to access the CIC751 device.<br>0: On-chip MLI<br>1: On-chip SSC<br>Event request output line 5 (SR5)<br>After latching the initial state with the rising edge of<br>the PORST signal (see Chapter 2.5), this pin car<br>be used as an additional general purpose or SR5<br>output line. |  |  |  |

| TESTMODE <sup>3)</sup> | 27<br>P0.9     | I/O                    | Test Mode Selection<br>0: Reserved; do no use<br>1: Normal Mode<br>After latching the initial state with the rising edge of<br>the PORST signal, this pin can be used as an<br>additional general purpose or special function I/O<br>line (see Chapter 2.5).                                                                                                                |  |  |  |

| SR0                    | 28<br>P0.10    | I/O                    | Event request output line 0                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| SR1                    | 29<br>P0.11    | I/O                    | External Trigger                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| SR2                    | 30<br>P0.12    | I/O                    | External Trigger                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| PORST                  | 31             | I                      | Power-on Reset                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| V <sub>DDM</sub>       | 34             | +5 V                   | Power Supply, supply for ADC module                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| V <sub>DDP</sub>       | 18, 33         | +3.3 V<br>or<br>+5.0 V |                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| V <sub>DDC</sub>       | 16             | +2.5 V                 | Power Supply, supply for digital module cores                                                                                                                                                                                                                                                                                                                               |  |  |  |

| V <sub>ss</sub>        | 15, 32         | 0 V                    | Ground                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

#### Table 1-1 Pin Definitions and Functions (cont'd)

1) In addition to the analog input function of pin P1.x, a digital input stage is available. This input stage is activated while STCU\_SYSCON.P1DIDIS = 0.

2) The initial logic state on pin MODE is latched while the PORST input is active. A weak pull-up can be disabled if used as the SR5 pin.

3) The initial logic state on pin TESTMODE is latched while the PORST input is active.

Figure 1-2 shows the pin-out for a 38-pin package.

Figure 1-2 Pins for P/PG-TSSOP-38 Package

Figure 1-3 Pin Numbering for P/PG-TSSOP-38 Package

## 2 System and Control Unit (SCU)

The System and Control Unit (SCU) controls all system relevant tasks.

The system tasks of the SCU are:

- Reset operation (see Chapter 2.1)

- System clock control (see Chapter 2.3)

- Power supply system (see Chapter 2.4)

- System Interrupt control (see Chapter 2.5)

## 2.1 Reset Control Block

The single system reset function initializes the CIC751 into a defined default state and is invoked by any of the following trigger conditions:

- External PORST reset

- Power-on reset; indicated by hardware reset input after power-on

- Internal EVR fail reset

- The EVR encounters a problem and the required power supply levels are not longer guaranteed

- Setting bit SCU\_SYSCON.SWRST

- This generates a software trigger reset

The entire CIC751 is reset, regardless of the means by which the reset was generated. A reset always triggers a new mode selection phase with the exception that a software reset does not trigger a new Mode Selection. A software reset retains the mode currently selected.

## 2.1.1 **Power-On Reset**

The PORST input pin requests a power-on reset. Driving the PORST pin low causes a non-synchronized reset of the entire device.

PORST is equipped with a noise suppression filter which suppresses glitches below 10 ns pulse width. PORST pulses with a width above 100 ns are safely recognized.

## 2.1.2 Embedded Voltage Regulator (EVR) Reset

If the power supply does not reach the value required for proper functionality, a reset is applied. This ensures a reproducible behavior after power-on or in the case of power-fail.

## 2.2 Mode Selection

The pins TESTMODE and MODE should supplied with specific voltage levels to ensure correct configuration of the CIC751.

## 2.2.1 MODE Pin

The MODE pin defines whether the MLI interface or the SSC interface is activated for Normal Mode. For MODE = 0, the MLI interface is activated and configured as the only communication interface. For MODE = 1, the SSC interface is activated and configured as the only communication interface.

The value that is sampled and used for this decision must be held for 400  $\mu s$  after  $V_{\text{DDP}}$  reached 1.5 V.

## 2.2.2 TESTMODE Pin

The pin must be tied to '1'.

#### 2.3 Clock System

This section describes the clock system of the CIC751. Topics include clock generation, clock domains, operation of clock circuitry, and clock control registers.

#### 2.3.1 Overview

The CIC751 clock system performs the following functions:

- Uses the internal free running frequency of the VCO block to create a fast clock frequency  $f_{SYS}$ .

- Uses the internal oscillator of the VCO block to create a fast clock frequency  $f_{SYS}$ .

- Acquires and buffers the external clock signal (RCLK) to create a fast clock frequency  $f_{SYS}$ .

- Distributes the in-phase synchronized clock signal throughout the CIC751's entire clock tree.

The clock system must be operational before the CIC751 can operate, so it contains special logic to handle power-up and reset operations. Its services are fundamental to the operation of the entire system, so it contains a special fail-safe logic.

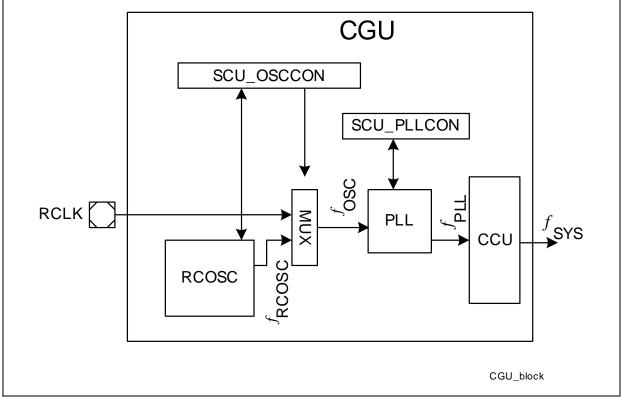

#### 2.3.2 Clock Generation Unit

The Clock Generation Unit (CGU) allows very flexible clock generation for CIC751.

The CGU in the CIC751 consists of an oscillator circuit (RCOSC), one Phase-Locked Loop (PLL) module, and a Clock Control Unit (CCU). The CGU can convert a low-frequency clock signal to a high-speed internal clock.

#### Figure 2-1 Clock Generation Unit Block Diagram

The following sections describe the various parts of the CGU:

## 2.3.2.1 RC Oscillator Circuit (RCOSC)

The RC Oscillator Circuit (RCOSC) is designed to work without an external crystal oscillator or an external stable clock source. The RCOSC consists of an Schmitt Trigger RC oscillator core and a standard current reference to provide a VDD-independent bias current.

#### Internal Clock Mode

When operating without an external crystal or clock source, the RC oscillator provides a stabile clock frequency of 9 MHz. The stability of this clock frequency is influenced by the temperature.

The system clock  $f_{SYS}$  (for Normal Mode equal to  $f_{PLL}$ ) is generated from an oscillator clock  $f_{OSC}$  in one of four selectable ways:

- Bypass Mode (Direct Drive)

- Prescaler Mode

- Normal Mode

- Free running Mode

## 2.3.2.2 Phase-Locked Loop (PLL) Module

This section describes the PLL module of the CIC751. The PLL supplies the system with a single clock frequency.

## Features

- Programmable clock generation PLL

- Loop filter

- Input frequency<sup>1)</sup>: $f_{OSC} = 3.1$  to 37.5 MHz

- VCO frequency:  $f_{VCO} = 100$  to 250 MHz (select by range)

- VCO lock detection

- Oscillator run detection

- Output frequency: $f_{PLL} = 6.25$  to 250 MHz

- 2bit input divider P:(divide by PDIV+1)

- 5bit feedback divider N:(multiply by NDIV+1, stability restrictions possible)

- 4bit output divider K:(divide by KDIV+1)

- Bypass Mode

- Prescaler Mode

- Freerunning Mode

- Normal Mode

- Glitchless switching between Normal Mode and Prescaler Mode

#### PLL Functional Description

The PLL provides the system with a clock generated from one of the various potential clock sources.

<sup>1)</sup> For P = 1, otherwise multiplied by P.

## Figure 2-2 PLL Block Diagram

The PLL uses up to three dividers to manipulate the input frequency in a configurable way. Each of the three dividers can be bypassed in some way to define an operating mode

Bypassing P, N, and K divider; this defines the Bypass Mode

Bypassing N divider; this defines the Prescaler Mode

Bypassing no divider; this defines the Normal Mode

Ignoring the P divider; this defines the Freerunning Mode

#### Normal Mode

In Normal Mode, the input clock  $f_{OSC}$  is divided by a factor P, multiplied by a factor N, and then divided by a factor K.

So, the output frequency is given by

$$f_{PLL} = \frac{N}{P \cdot K} \cdot f_{OSC}$$

(2.1)

The Normal Mode is selected by setting SCU\_PLLCON.PLLCTRL =  $11_B$ .

#### **Bypass Mode**

In Bypass Mode, the input clock  $f_{\rm OSC}$  is directly connected to the PLL output  $f_{\rm PLL}$ . So, the output frequency is given by

$$f_{PLL} = f_{OSC}$$

(2.2)

The Bypass Mode is selected by setting SCU\_PLLCON.BY =  $1_B$ .

#### **Prescaler Mode**

In Prescaler Mode, the input clock  $f_{OSC}$  is divided down by a factor P \* K. So, the output frequency is given by

$$f_{PLL} = \frac{f_{OSC}}{P \cdot K}$$

(2.3)

The Prescaler Mode is selected by setting SCU\_PLLCON.PLLCTRL =  $00_{B}$ .

#### Freerunning Mode

In Freerunning Mode, the base frequency output of the Voltage Controlled Oscillator (VCO)  $f_{\text{VCObase}}$  is only divided by a factor K.

So, the output frequency is given by

$$f_{PLL} = \frac{f_{VCObase}}{K}$$

(2.4)

The Freerunning Mode is selected by setting SCU\_PLLCON.PLLCTRL =  $10_B$ .

#### **General Configuration Overview**

All three divider values and all necessary other values can be configured via the PLL configuration register **SCU\_PLLCON**.

**Table 2-1** lists a few possible values for the P factor and gives the valid output frequency range for the P divider dependent on P and the  $f_{OSC}$  frequency range:

| P = PDIV+1 | PDIV |            | =      |        |                  |        |

|------------|------|------------|--------|--------|------------------|--------|

|            |      | 4 MHz      | 10 MHz | 16 MHz | 20 MHz           | 25 MHz |

| 1          | 0    | 4          | 10     | 16     | 20               | 25     |

| 2          | 1    | not        | 5      | 8      | 10               | 12.5   |

| 3          | 2    | allowed    | 3.33   | 5.33   | 6.6 <del>6</del> | 8.33   |

| 4          | 3    | not allowe | ed     | 4      | 5                | 6.25   |

Divider Festere

Note: Of course, the entire range between two  $f_{OSC}$  columns in the above table is allowed. E.g. for a range  $f_{OSC} = 20$  to 25, and P = 3,  $f_{RFF} = 6.6\overline{6}$  to  $8.3\overline{3}$  MHz.

The P-divider output frequency  $f_{\text{REF}}$  is fed to a Voltage Controlled Oscillator (VCO). The VCO is part of the PLL with a feedback path. A divider in the feedback path (N divider) divides the VCO frequency. As well as N, the correct range of  $f_{VCO}$  must be chosen by configuring SCU\_PLLCON.PLLVB:

| PLLVB [1:0] | $f_{\sf VCOmin}$     | $f_{\sf VCOmax}$ | $f_{\rm VCObase}$ <sup>1)</sup> | Unit |  |

|-------------|----------------------|------------------|---------------------------------|------|--|

| 01          | 150                  | 200              | 40130                           | MHz  |  |

| 00          | 100                  | 150              | 2080                            | MHz  |  |

| 10          | 200                  | 250              | 60180                           | MHz  |  |

| 11          | Reserved; do not use |                  |                                 |      |  |

1) f<sub>VCObase</sub> is the free running operation frequency of the PLL, when no input clock is available. These values are only preliminary and are later updated with more exact simulation and measurement results from the PLL.

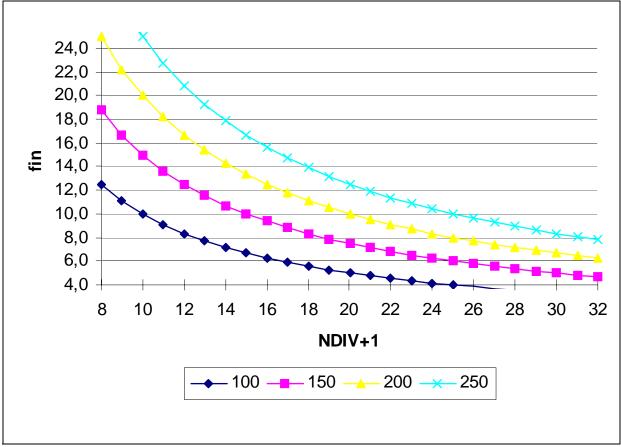

The VCO band (100...150 MHz, 150...200 MHz, 200...250 MHz) must be selected according to the desired VCO output frequency (100...250 MHz). Figure 2-3 illustrates how this output frequency depends on the input frequency and the multiplication factor.

#### Figure 2-3 VCO Band Selection

**Table 2-3** lists the possible N loop division rates and gives the valid output frequency range for  $f_{\text{REF}}$  depending on N and the VCO frequency range:

| N = NDIV+1 | NDIV | $f_{\sf REF}$ for $f_{\sf VCO}$ = |                   |       |       |  |  |  |  |

|------------|------|-----------------------------------|-------------------|-------|-------|--|--|--|--|

|            |      | 100                               | 150               | 200   | 250   |  |  |  |  |

| <b>≤</b> 7 | ≤ 6  | not allowe                        | əd <sup>1)</sup>  |       | L     |  |  |  |  |

| 8          | 7    |                                   | 18.75             | 25.00 | 31.25 |  |  |  |  |

| 9          | 8    | 11.11                             | 16.6 <del>6</del> | 22.22 | 27.77 |  |  |  |  |

| 10         | 9    | 10.00                             | 15.00             | 20.00 | 25.00 |  |  |  |  |

| 1130       | 1029 |                                   |                   |       |       |  |  |  |  |

| 31         | 30   | 3.22                              | 4.84              | 6.45  | 8.06  |  |  |  |  |

| 32         | 31   | 3.13                              | 4.69              | 6.25  | 7.81  |  |  |  |  |

#### Table 2-3N Loop Division Rates

1)Values in this range are allowed in Freerunning Mode, but have no impact there.

Note: Of course, the entire range between two  $f_{\rm VCO}$  columns in the above table is allowed.

The N-divider output frequency  $f_{\text{DIV}}$  is then compared with  $f_{\text{REF}}$  in the phase detector logic, which is within the VCO logic. The phase detector determines the difference between the two clock signals and accordingly controls the output frequency of the VCO,  $f_{\text{VCO}}$ .

Note: Due to this operation, the VCO clock of the PLL has a frequency that is a multiple of  $f_{REF}$ . The factor for this is controlled through the value applied to the N-divider in the feedback path. For this reason, this factor is often called a multiplier, although it actually controls division.

The output frequency of the VCO,  $f_{VCO}$ , is divided by K to provide the final desired output frequency  $f_{PLL}$ . Table 2-4 lists the output frequency range depending on the K divisor and the VCO frequency range:

| K =<br>K2DIV+1 | K2<br>DIV |       | Duty Cycle<br>[%] |                  |                  |         |

|----------------|-----------|-------|-------------------|------------------|------------------|---------|

|                |           | 100   | 150               | 200              | 250              |         |

| 1              | 0         | 100.0 | 150.0             | 200.0            | 250.0            | 45 - 55 |

| 2              | 1         | 50.0  | 75.0              | 100.0            | 125.0            | 50      |

| 3              | 2         | 33.3  | 50.0              | 66. <del>6</del> | 83.3             | 33      |

| 4              | 3         | 25.0  | 37.5              | 50.0             | 62.5             | 50      |

| 5              | 4         | 20.0  | 30.0              | 40.0             | 50.0             | 40      |

| 614            | 513       |       |                   |                  |                  |         |

| 15             | 14        | 6.6   | 10.0              | 13. <del>3</del> | 16. <del>6</del> | 46.6    |

| 16             | 15        | 6.25  | 9.38              | 12.5             | 18.75            | 50      |

Table 2-4K Divisor Table

Note: Note that the entire range between two  $f_{vco}$  columns in the above table is allowed.

Note: For divider factors that cause duty cycles far from 50% not only the cycle time has to be checked, but also the minimum clock pulse width.

#### **Oscillator Run Detection**

Oscillator Run Detection monitors the incoming clock from the oscillator and determines whether it is suitable for an operation in Normal Mode with the selected setting for the N-Divider. Only incoming frequencies that are too low to enable a stable operation of the VCO circuit are detected.

#### PLL Configuration and Status Registers

The PLL Configuration and Status Registers hold the hardware configuration bits of the PLL, and provide the control for the N, P and K-Dividers as well as the PLL status information.

The clock generation path is selected via the PLL control register SCU\_PLLCON.

## 2.3.2.3 Clock Control Unit

The Clock Control Unit (CCU) receives the clock that is created by the PLL  $f_{\rm PLL}$ . In Normal Mode the PLL output frequency  $f_{\rm PLL}$  is always used directly as the system clock  $f_{\rm SYS}$ .

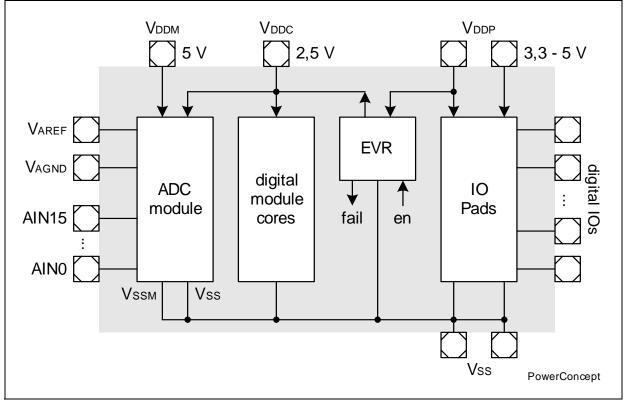

## 2.4 Power Supply System

The power supply system is selected such that it offers maximum flexibility and requires a minimum of pins and system integration cost.

Features:

- 5 V supply for the ADC

- 5 V or 3.3 V supply for the I/O pads

Figure 2-4 CIC751 Power Supply System

## 2.4.1 Embedded Voltage Regulator

The Embedded Validated Voltage Regulator (EVR) is used for the reduction of supply interfaces between PCB and CIC751. In addition to the I/O voltage VDDP, the voltage supply for the core VDD is necessary. The handling of two different supply voltages can have a large impact on application board design. Thus, it is highly appreciated to provide the on-chip voltage by an on-chip voltage regulator. This embedded voltage regulator further helps reduce the power consumption of the entire chip.

## 2.5 Event Control

Events or interrupts are generated towards the system by the ADC, SSC, MLI, DMA, and pins. In this chip, the term event is used because the term interrupt is normally linked with the interruption of a code execution but a code executing unit is not present within the CIC751.

## 2.5.1 Event Sources

There are 13 event sources available for the CIC751.

- ADC event 0; injection conversion interrupt of the ADC module

- ADC event 1; standard conversion interrupt of the ADC module

- ADC event 2; the OR-combination of all valid bits of the ADC\_RESBn registers

- Doorbell event 0 that becomes active if the channel number written to INRES equals DBCTR.COMP0

- Doorbell event 1 that becomes active if the channel number written to INRES equals DBCTR.COMP1

- Doorbell event 2 that monitors the valid bit ADC\_RESBn.V of the result register selected by DBCTR.COMP0

- Doorbell event 3 that monitors the valid bit ADC\_RESBn.V of the result register selected by DBCTR.COMP1

- MLI Request 0 of the MLI module

- MLI Request 1 of the MLI module

- MLI Request 2 of the MLI module

- MLI Request 3 of the MLI module

- External trigger Input 0

- External trigger Input 1

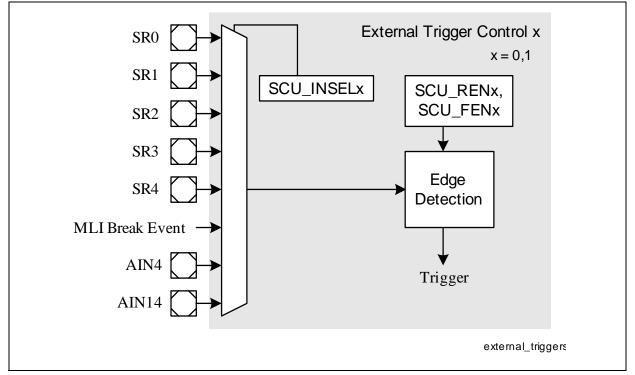

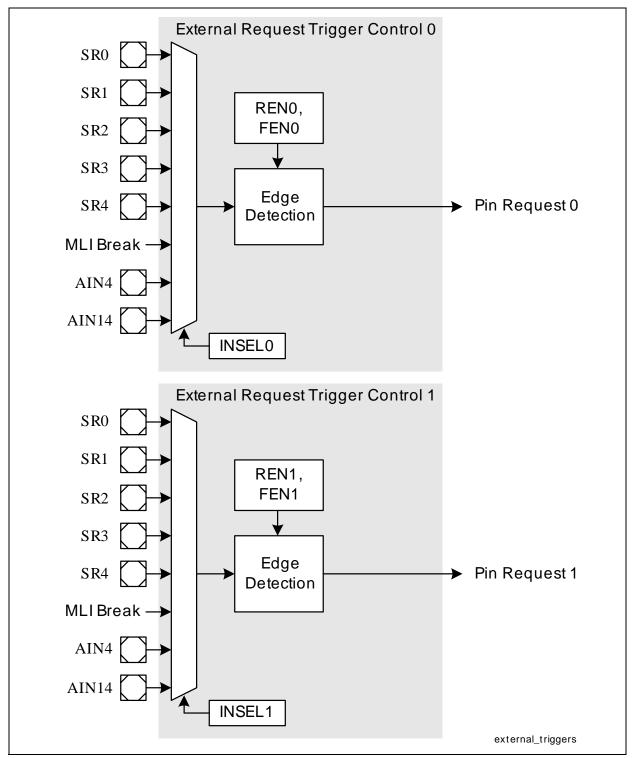

## 2.5.2 External Trigger Inputs

The device supports external trigger sources to start ADC conversions or DMA transfers. The device has several input pins (SR0 - 2 for MLI Mode and SR0 - 4 for SSC Mode) capable of delivering a trigger input signal.

#### Figure 2-5 External Triggers

The rising edge and falling edge sensitivity of the selected input can be enabled individually. If both edge detections are enabled, an external trigger event is generated upon each change of the signal level (rising edge or falling edge).

The external trigger control register SCU\_ETCTR contains the bits defining the behavior of the external trigger inputs.

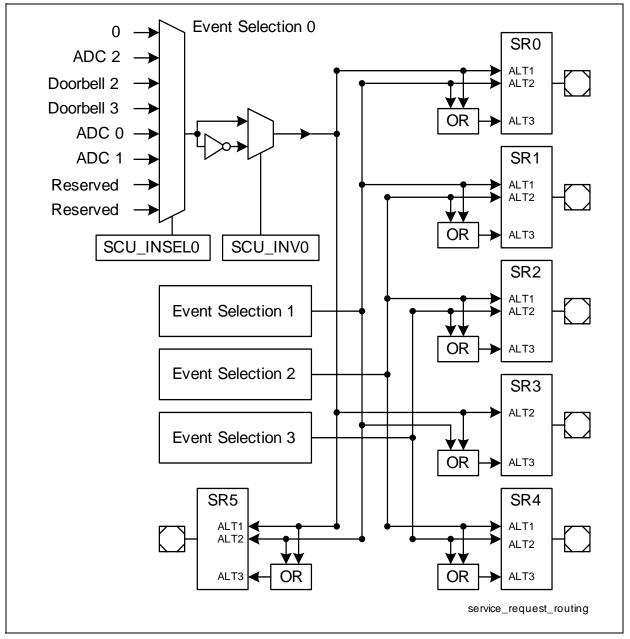

## 2.5.3 Event Output Structure

The CIC751 allows output of internal status or notification events on output pins. In order to support different applications and pin usage, internal events are generated. These events are then distributed to the service request pins SRn (n = 0...5).

The following status events can be selected as the source for an output of an SRn pin:

- Doorbell event 2

- Doorbell event 3

- ADC event 2; the OR-combination of all valid bits of the ADC\_RESBn registers

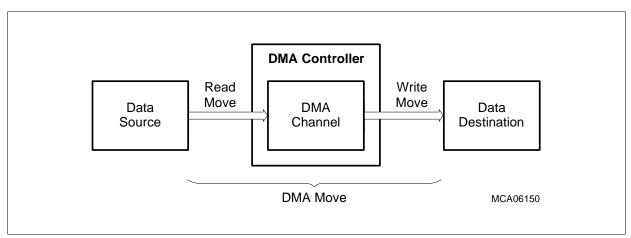

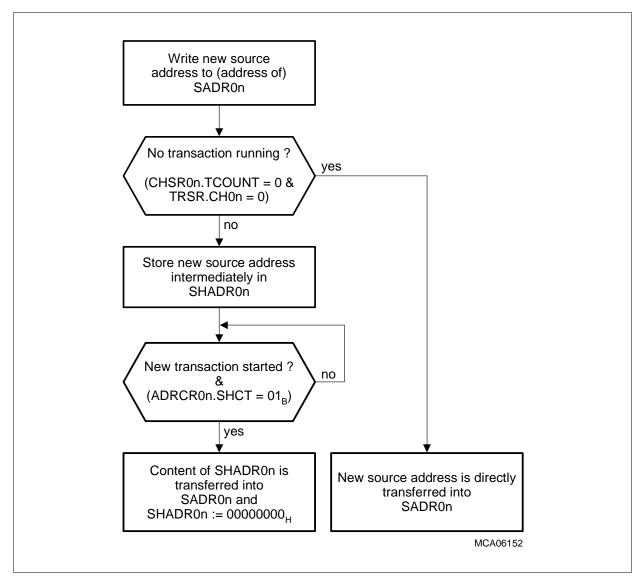

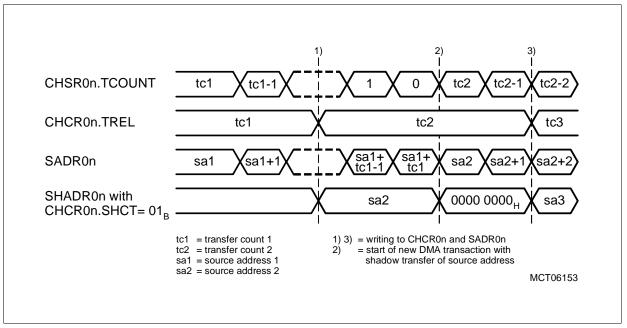

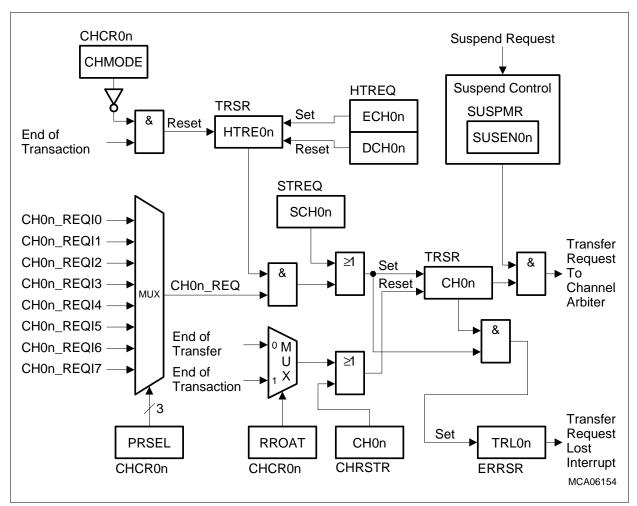

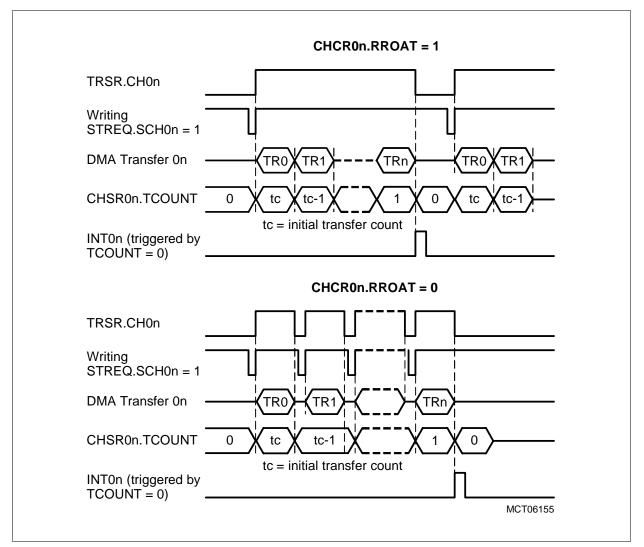

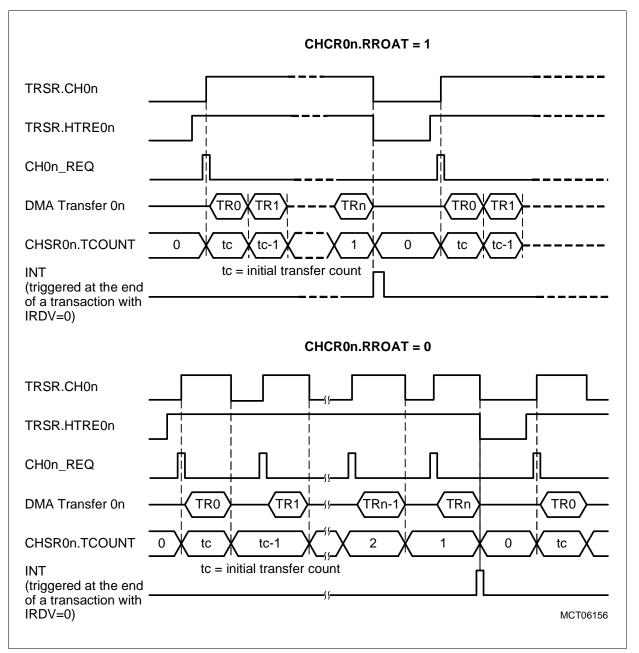

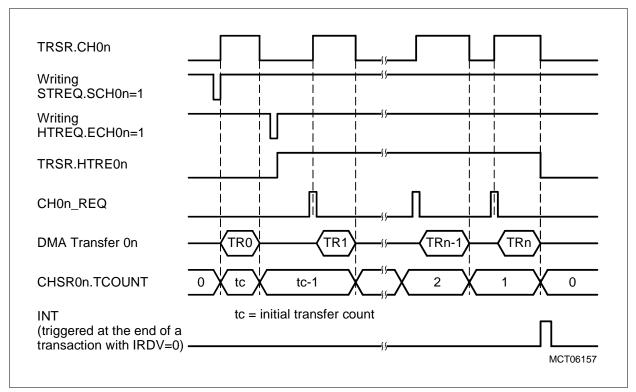

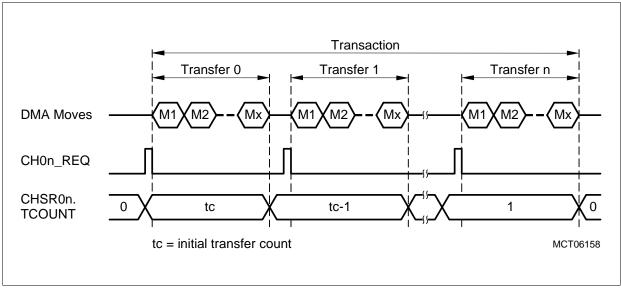

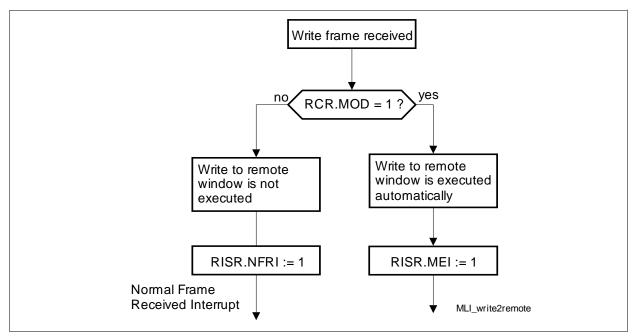

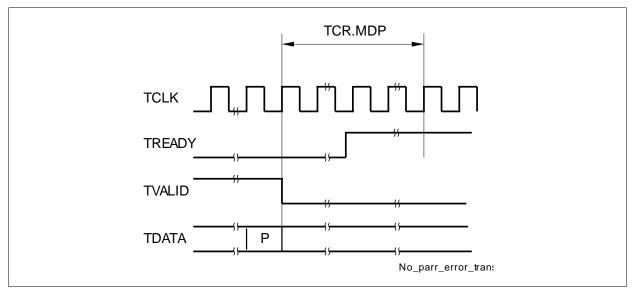

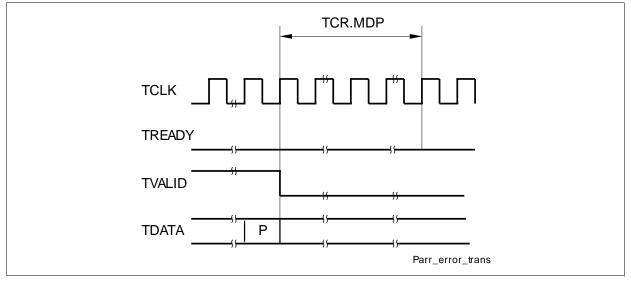

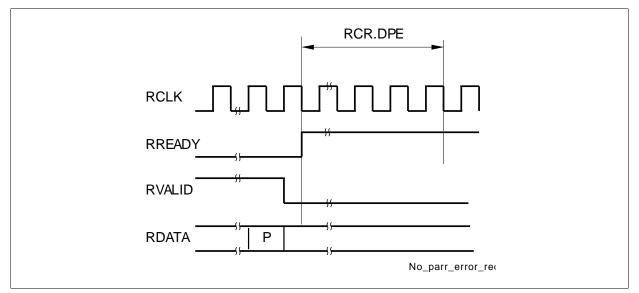

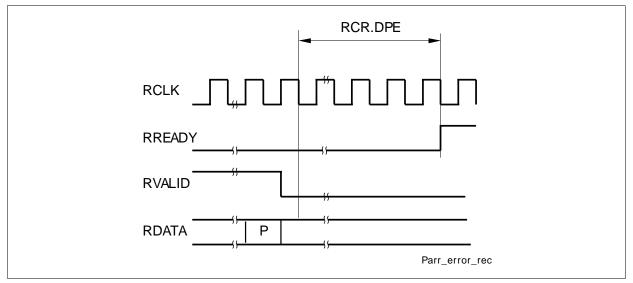

- ADC event 0