Rev: PR-071006

# **PCI66-16A016FLV**

# 16-BIT, 16-CHANNEL, HIGH-SPEED PCI ANALOG OUTPUT BOARD

With Balanced Differential Outputs and Reconstruction Filters

**REFERENCE MANUAL**

# PRELIMINARY

General Standards Corporation Ph:(256)880-8787 FAX:(256)880-8788 Email: solutions@GeneralStandards.com

MAN-PCI66-16AO16FLV

#### PCI66-16AO16FLV

Copyright (C) 2006 General Standards Corp.

Additional copies of this manual or other General Standards Co. literature may be obtained from:

General Standards Corp. 8302A Whitesburg Dr. Huntsville, Alabama 35802 Telephone: (256) 880-8787 FAX: (256) 880-8788

The information in this document is subject to change without notice.

General Standards Corp. makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Although extensive editing and reviews are performed before release to ECO control, General Standards Corp. assumes no responsibility for any errors that may exist in this document. No commitment is made to update or keep current the information contained in this document.

General Standards Corp. does not assume any liability arising out of the application or use of any product or circuit described herein, nor is any license conveyed under any patent rights or any rights of others.

General Standards Corp. assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

General Standards Corp. reserves the right to make any changes, without notice, to this product to improve reliability, performance, function, or design.

All rights reserved.

No part of this document may be copied or reproduced in any form or by any means without prior written consent of General Standards Corp.

# **TABLE OF CONTENTS**

| SECTION | TITLE                            | PAGE |  |

|---------|----------------------------------|------|--|

| 1.0     | INTRODUCTION                     | 1-1  |  |

| 1.1     | General Description              | 1-1  |  |

| 1.2     | Functional Overview              | 1-2  |  |

| 2.0     | INSTALLATION AND MAINTENANCE     | 2-1  |  |

| 2.1     | Board Configuration              | 2-1  |  |

| 2.2     | Installation                     | 2-1  |  |

| 2.2.1   | Physical Installation            | 2-1  |  |

| 2.2.2   | Input/Output Cable Connections   | 2-2  |  |

| 2.3     | System Configuration             | 2-3  |  |

| 2.3.1   | Output Considerations            | 2-3  |  |

| 2.3.1.1 | Output Configurations            | 2-3  |  |

| 2.3.1.2 | Line Losses                      | 2-4  |  |

| 2.3.1.3 | Remote Ground Sensing            | 2-4  |  |

| 2.3.2   | External Clock and Trigger I/O   | 2-5  |  |

| 2.3.2.1 | Sample Clock Output              | 2-5  |  |

| 2.3.2.2 | Burst Trigger I/O                | 2-5  |  |

| 2.3.3   | Multiboard Synchronization       | 2-5  |  |

| 2.3.3.1 | Synchronized Bursts              | 2-5  |  |

| 2.3.3.2 | Synchronized Clocks              | 2-5  |  |

| 2.4     | Maintenance                      | 2-6  |  |

| 2.5     | Reference Verification           | 2-6  |  |

| 2.5.1   | Equipment Required               | 2-7  |  |

| 2.5.2   | Verification Procedure           | 2-7  |  |

| 3.0     | CONTROL SOFTWARE                 | 3-1  |  |

| 3.1     | Introduction                     | 3-1  |  |

| 3.2     | Board Control Register           | 3-1  |  |

| 3.3     | Configuration and Initialization | 3-1  |  |

| 3.3.1   | Board Configuration              | 3-1  |  |

| 3.3.2   | Initialization                   | 3-3  |  |

ì

# TABLE OF CONTENTS (Continued)

| SECTION   | TITLE                           | PAGE |

|-----------|---------------------------------|------|

| 3.4       | Analog Output Control           | 3-4  |

| 3.4.1     | Data Organization               | 3-5  |

| 3.4.1.1   | Active Channels                 | 3-5  |

| 3.4.1.1.1 | Selection                       | 3-5  |

| 3.4.1.1.2 | Loading                         | 3-5  |

| 3.4.1.2   | Data Frame                      | 3-6  |

| 3.4.1.3   | Output Data Format              | 3-6  |

| 3.4.1.3.1 | Output Data Buffer              | 3-6  |

| 3.4.1.3.2 | Output Data Coding              | 3-7  |

| 3.4.1.4   | Voltage Range Selection         | 3-7  |

| 3.4.2     | Output Buffer                   | 3-7  |

| 3.4.2.1   | Buffer Operations Register      | 3-7  |

| 3.4.2.2   | Active Buffer                   | 3-9  |

| 3.4.2.3   | Status Flags                    | 3-9  |

| 3.4.2.4   | Open Buffer                     | 3-9  |

| 3.4.2.5   | Circular Buffer                 | 3-10 |

| 3.4.3     | Output Clocking                 | 3-11 |

| 3.4.3.1   | Clock Source                    | 3-11 |

| 3.4.3.1.1 | External Clock                  | 3-11 |

| 3.4.3.1.2 | Internal Rate Generator         | 3-11 |

| 3.4.3.2   | Simultaneous Clocking           | 3-12 |

| 3.4.3.3   | Sequential Operation            | 3-12 |

| 3.4.4     | Sampling Mode                   | 3-12 |

| 3.4.4.1   | Continuous Sampling             | 3-12 |

| 3.4.4.2   | Data Bursts                     | 3-13 |

| 3.4.5     | Multiboard Synchronization      | 3-13 |

| 3.4.5.1   | Synchronous Bursts              | 3-13 |

| 3.4.5.2   | Synchronous Clocking            | 3-14 |

| 3.4.6     | Function Generation             | 3-14 |

| 3.4.6.1   | Periodic and One-Shot Functions | 3-14 |

iì

# **TABLE OF CONTENTS (Continued)**

| <b>SECTION</b> | TITLE                                           | PAGE |

|----------------|-------------------------------------------------|------|

| 3.4.6.2        | Multiple Functions                              | 3-14 |

| 3.4.6.3        | Functioning Sequencing                          | 3-14 |

| 3.5            | Autocalibration                                 | 3-16 |

| 3.6            | Interrupt Control                               | 3-16 |

| 3.6.1          | Local Interrupt Request                         | 3-16 |

| 3.6.2          | Enabling the PCI Interrupt                      | 3-17 |

| 3.7            | Remote Ground Sensing                           | 3-17 |

| 3.8            | Application Examples                            | 3-18 |

| 3.8.1          | Sequential Direct Outputs                       | 3-19 |

| 3.8.2          | Simultaneous Direct (Single Group) Outputs      | 3-19 |

| 3.8.3          | Continuous Function                             | 3-20 |

| 3.8.4          | Periodic Function                               | 3-21 |

| 3.8.5          | Function Burst                                  | 3-22 |

| 3.8.6          | Function Sequencing                             | 3-23 |

| 3.9            | DMA Operation                                   | 3-24 |

| 3.10           | Synchronization with Sigma-Delta Input Products | 3-25 |

| 3.10.1         | Adjustable Reference Frequency Control          | 3-25 |

| 3.10.2         | Initiator/Target Configurations                 | 3-26 |

| 3.11           | Assembly Configuration Register                 | 3-27 |

| 3.12           | Output Filters                                  | 3-27 |

|                |                                                 |      |

|                |                                                 |      |

| 4.0        | PRINCIPLES OF OPERATION          | 4-1 |

|------------|----------------------------------|-----|

| 4.1        | General Description              | 4-1 |

| 4.2        | Analog Outputs                   | 4-2 |

| 4.3        | Autocalibration                  | 4-2 |

| 4.4        | Power Control                    | 4-2 |

|            |                                  |     |

| Appendix A | Local Register Quick Reference   | A-1 |

| Appendix B | Migration from the PC104P-16AO20 | B-1 |

# LIST OF ILLUSTRATIONS

| <b>FIGURE</b> | TITLE                            | PAGE |

|---------------|----------------------------------|------|

| 1.1-1         | Physical Configuration           | 1-1  |

| 1.2-1         | Functional Organization          | 1-2  |

| 2.2-1         | Physical Installation            | 2-1  |

| 2.2-2         | System I/O Connector             | 2-2  |

| 2.3-1         | Output Configurations            | 2-3  |

| 2.3-2         | Line Loss Versus Load Current    | 2-4  |

| 2.3-3         | Multiboard Burst Synchronization | 2-6  |

| 2.5-1         | Reference Adjustment Access      | 2-7  |

| 3.4-1         | Typical Buffer Loading Sequence  | 3-6  |

| 3.4-2         | Open Buffer Data Flow            | 3-10 |

| 3.4-3         | Circular Buffer Data Flow        | 3-10 |

| 3.4-4         | Function Sequencing              | 3-15 |

| 4.1-1         | Functional Block Diagram         | 4-1  |

General Standards Corporation Ph:(256)880-8787 FAX:(256)880-8788 Email: solutions@GeneralStandards.com

# LIST OF TABLES

| TABLE  | TITLE                                           | PAGE |

|--------|-------------------------------------------------|------|

| 2.2-1  | System I/O Connector Pin Functions              | 2-2  |

| 2.5.1  | Reference Verification Equipment                | 2-7  |

| 3.1-1  | Control and Data Registers                      | 3-1  |

| 3.2-1  | Board Control Register                          | 3-2  |

| 3.3-1  | Configuration Operations                        | 3-3  |

| 3.4-1  | Summary of Output Control Parameters            | 3-4  |

| 3.4-2  | Channel Selection Register                      | 3-5  |

| 3.4-3  | Output Data Buffer                              | 3-6  |

| 3.4-4  | Output Data Coding; D15D00                      | 3-7  |

| 3.4-5  | Buffer Operations Register                      | 3-8  |

| 3.4-6  | Active Buffer Size                              | 3-9  |

| 3.4-7  | Sample Rate Control Register                    | 3-11 |

| 3.4-8  | Sample Rate Selection                           | 3-12 |

| 3.6-1  | Interrupt Event Selection                       | 3-17 |

| 3.8-1  | Summary of Operation Examples                   | 3-18 |

| 3.8-2  | Initial Operations                              | 3-18 |

| 3.8-3  | Sequential Direct Outputs Example               | 3-19 |

| 3.8-4  | Simultaneous Direct Outputs Example             | 3-19 |

| 3.8-5  | Continuous Function Example                     | 3-20 |

| 3.8-6  | Periodic Function Example                       | 3-21 |

| 3.8-7  | Function Burst Example                          | 3-22 |

| 3.8-8  | Function Sequencing Example                     | 3-23 |

| 3.9-1  | Typical DMA Register Configuration              | 3-24 |

| 3.10-1 | Adjustable Reference Frequency Control Register | 3-25 |

| 3.10-2 | Multiboard Clocking Configurations              | 3-26 |

| 3.11-1 | Assembly Configuration Register                 | 3-27 |

v

#### PCI66-16AO16FLV

(This page blank intentionally)

# SECTION 1.0 INTRODUCTION

### 1.1 General Description

The PCI66-16AO16FLV board provides precision high-speed analog output capability for PCI applications. Sixteen 16-bit analog output channels provide either single-ended or balanced differential output configurations, with two selectable high-order reconstruction filters in each channel. Output ranges are selectable as either  $\pm 1.5V$  and  $\pm 2.5V$  with a high-current output option, or as  $\pm 5V$  and  $\pm 10V$  with a high-level option. The outputs can be clocked either simultaneously or sequentially at rates up to 450 KSPS (Kilosamples per second) per channel. The board is functionally and mechanically compatible with the IEEE PCI local bus specification Revision 2.3 for 32-Bit transfers with 33MHz or 66MHz PCI clocking.

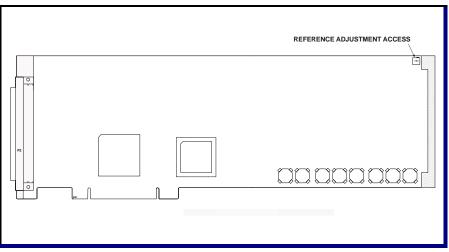

Power requirements consist of +5 VDC from the PCI bus in accordance with the specification, and operation over the specified temperature range is achieved with conventional cooling. Specific details of physical characteristics and power requirements are contained in the PCI66-16AO16FLV product specification. Figure 1.1-1 shows the general physical configuration of the board, and the arrangement of major components.

Figure 1.1-1. Physical Configuration

The board is designed for minimum off-line maintenance, and includes internal monitoring and autocalibration features that eliminate the need for disconnecting or removing the module from the system for calibration. All system input and output connections are made through a single 68-pin I/O connector. Analog outputs are initialized to zero-level (midrange).

# **1.2 Functional Overview**

Principal capabilities of the PCI66-16AO16FLV board are summarized in the following list of features.

Sixteen Precision High-Speed 3-Wire Balanced Differential Analog Output Channels 16-Bit Resolution; D/A Converter per Channel Data Rates up to 450K Samples per Second per Channel; 7.2MSPS Aggregate Rate Outputs Update Simultaneously or Sequentially; Software-Selectable Output Ranges of ±10V and ±5V, or ±2.5V and ±1.25V 8th-Order Continuous-Time Output Reconstruction Filters D32 Transfer Compatibility in both 33MHz and 66MHz clocking Environments 256K-Sample Analog Output FIFO Buffer Configurable as Either Circular or Open Continuous and Triggered-Burst (One-Shot) Output Modes Data Rate Controlled by Adjustable Internal Clock or by Externally Supplied Clock Supports Multiboard Synchronization. On-demand Internal Autocalibration of all Channels Differential Sync I/O Available for Synchronizing GSC's Sigma-Delta ADC Boards Active Buffer Size Adjustable from 8 Samples to 256K Samples.

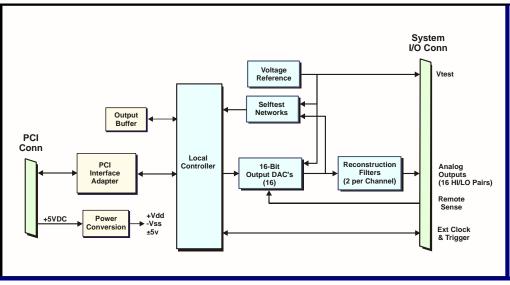

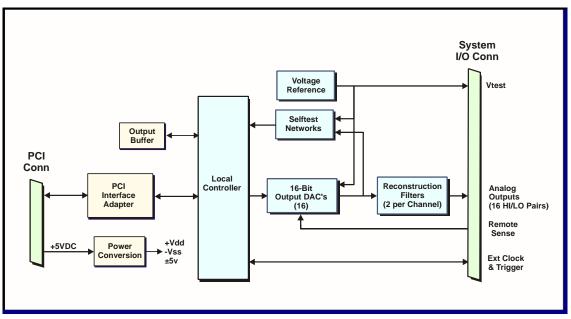

Figure 1.2-1 outlines the internal functional organization of the board. Sixteen analog output channels are controlled through an analog output buffer, and can be updated either simultaneously or sequentially. The outputs can be factory-configured either as 3-wire balanced differential channels or as 2-wire single-ended channels. Two reconstruction filters are provided in each channel.

Figure 1.2-1. Functional Organization

The output clocking rate can be controlled by an internal rate generator, or by an external clock source. Internal selftest networks permit all channels to be calibrated to a single internal voltage reference. On-demand autocalibration adjusts offset and gain calibration DAC's in each output channel to calibrate all channels to an internal precision reference voltage.

# **SECTION 2.0**

# INSTALLATION AND MAINTENANCE

### 2.1 Board Configuration

This product has no field-alterable configuration features, and is completely configured at the factory.

#### 2.2 Installation

#### 2.2.1 Physical Installation

To minimize the opportunity for accidental damage before installation, the board should be stored in the original protective shipping envelope. System power must be turned OFF before proceeding with the installation.

CAUTION: This product is susceptible to damage from electrostatic discharge (ESD). Before removing the board from the conductive shipping envelope, ensure that the work surface, the installer and the host system are adequately discharged to ground.

Before removing the board from the protective shipping envelope, select an empty PCI slot in the host computer and, if a blank panel bracket is located in the slot position, remove the bracket. Then remove the board from the shipping envelope and position the board with the panel bracket oriented toward the expansion panel opening. Align the board's PCI edge-connector with the mating connector on the motherboard, and carefully press the board into position. Verify that the PCI connector has mated completely, and that the panel bracket is seated against the fastener bracket above the panel opening. To complete the installation, secure the panel bracket and rear support bracket with appropriate fasteners. Do not overtighten.

#### 2.2.2 Input/Output Cable Connections

System cable signal pin assignments are listed in Table 2.2-1. The system input/output connector is designed to mate with a 68-Pin dual-cable high-density 0.05-inch connector, Amp type 749621-7 or equivalent. This insulation displacement (IDC) cable connector accepts standard 0.050-inch ribbon cable, with the pin numbering convention shown in Table 2.2-1 and in Figure 2.2-2. "Twist and flat" cable is recommended for long cables (greater than five feet). Contact the factory if preassembled cables are required.

|     | ROW-A              | Ī | ROW-B |                   |                                                  |

|-----|--------------------|---|-------|-------------------|--------------------------------------------------|

| PIN | FUNCTION           | Í | PIN   | FUNCTION          |                                                  |

| 1   | OUTPUT 00 LO *     |   | 1     | OUTPUT 09 LO *    | Row B Row-A                                      |

| 2   | OUTPUT 00 HI       | Ì | 2     | OUTPUT 09 HI      | Pin 34                                           |

| 3   | OUTPUT RTN 00 **** | İ | 3     | OUTPUT 10 LO *    |                                                  |

| 4   | OUTPUT RTN 01      | Í | 4     | OUTPUT 10 HI      |                                                  |

| 5   | OUTPUT 01 LO *     | Í | 5     | OUTPUT RTN 09     | I/O<br>Conn                                      |

| 6   | OUTPUT 01 HI       | ľ | 6     | OUTPUT RTN 10     |                                                  |

| 7   | OUTPUT RTN 01      | ľ | 7     | OUTPUT 11 LO *    | PWB                                              |

| 8   | OUTPUT RTN 02      | Í | 8     | OUTPUT 11 HI      |                                                  |

| 9   | OUTPUT 02 LO *     | ľ | 9     | OUTPUT 12 LO *    |                                                  |

| 10  | OUTPUT 02 HI       | Í | 10    | OUTPUT 12 HI      |                                                  |

| 11  | OUTPUT RTN 02      | ľ | 11    | OUTPUT RTN 11     | Pin 1                                            |

| 12  | OUTPUT RTN 03      | Í | 12    | OUTPUT RTN 12     | a. I/O Connector (panel pin-view)                |

| 13  | OUTPUT 03 LO *     | ľ | 13    | OUTPUT 13 LO *    | a. NO connector (panel pin-view)                 |

| 14  | OUTPUT 03 HI       | ľ | 14    | OUTPUT 13 HI      |                                                  |

| 15  | OUTPUT RTN 03      |   | 15    | OUTPUT 14 LO *    |                                                  |

| 16  | OUTPUT RTN 04      |   | 16    | OUTPUT 14 HI      |                                                  |

| 17  | OUTPUT 04 LO *     |   | 17    | OUTPUT RTN 13     |                                                  |

| 18  | OUTPUT 04 HI       |   | 18    | OUTPUT RTN 14     | 5                                                |

| 19  | OUTPUT RTN 04      |   | 19    | OUTPUT 15 LO *    | Cable-B *                                        |

| 20  | OUTPUT RTN 05      |   | 20    | OUTPUT 15 HI      | / Cable-B *   ਨੂੰ Cable-A * /                    |

| 21  | OUTPUT 05 LO *     |   | 21    | OUTPUT RTN 15     |                                                  |

| 22  | OUTPUT 05 HI       |   | 22    | REM GND SENSE     | C C                                              |

| 23  | OUTPUT RTN 05      |   | 23    | OUTPUT RTN 15     |                                                  |

| 24  | OUTPUT RTN 06      |   | 24    | VTEST OUT         |                                                  |

| 25  | OUTPUT 06 LO *     |   | 25    | VTEST RETURN      | Pin-1 Wire Pin-1 Wire Front                      |

| 26  | OUTPUT 06 HI       |   | 26    | DIGITAL RETURN    | * 34-Conductor Ribbon<br>Cable; 0.050-in Spacing |

| 27  | OUTPUT RTN 06      |   | 27    | TRIG IN HI **     |                                                  |

| 28  | OUTPUT RTN 07      |   | 28    | TRIG IN LO **     | b. System Cable Connector                        |

| 29  | OUTPUT 07 LO *     |   | 29    | TRIG OUT HI **    |                                                  |

| 30  | OUTPUT 07 HI       |   | 30    | TRIG OUT LO **    | Figure 2. System I/O Connecto                    |

| 31  | OUTPUT RTN 07      |   | 31    | DAC CLK OUT HI ** |                                                  |

| 32  | OUTPUT RTN 08      |   | 32    | DAC CLK OUT LO ** |                                                  |

| 33  | OUTPUT 08 LO *     |   | 33    | CLOCK I/O HI ***  |                                                  |

| 34  | OUTPUT 08 HI       |   | 34    | CLOCK I/O LO ***  |                                                  |

Table 2.2-1. System I/O Connector Pin Functions

The differential analog output configuration is shown. For optional single-ended outputs, OUTPUT XX HI is an output, and OUTPUT XX LO is not used.

\* "No-connect" for the 2-Wire single-ended configuration.

\*\* Software-selectable as LVDS differential pairs. In TTL mode, 'HI' pins are signal pins, and 'LO' inputs should be connected to digital return.

\*\*\* Bidirectional synchronization signal.

\*\*\*\* All OUTPUT RTN XX pins are connected together internally

Channels available in 8-Channel and 12-Channel configurations: 8-Channel Board: Channels 00-07, 12-Channel board: Channels 00-11.

# 2.3 System Configuration

- 2.3.1 Output Considerations

- 2.3.1.1 Output Configurations

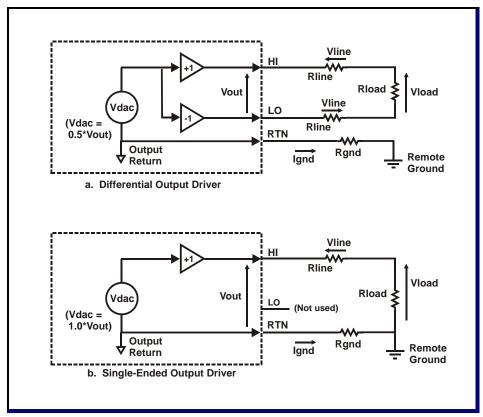

The sixteen analog output channels can be factory-configured either as 3-wire balanced differential outputs or as 2-wire single-ended outputs.

Balanced differential outputs (Figure 2.3-1a) provide the highest immunity to system noise and interference, and are recommended in all systems in which the loads will accept differential inputs. Each of the HI and LO outputs carries one-half of the output signal, with the two halves operating as complementary signals of equal amplitude and opposite polarity.. Since radiated interference usually affects both output lines simultaneously, the coupled interference appears as a common mode signal which will be attenuated in a differential load.

Figure 2.3-1. Output Configurations

For applications requiring single-ended outputs (Figure 2.3-1b), the output signal from each channel appears on the associated HI output pin, and is generated with reference to the output return pin. In general, single-ended outputs should drive only loads that are isolated from system ground. The best results are obtained when the loads also are isolated from each other

### 2.3.1.2 Line Losses

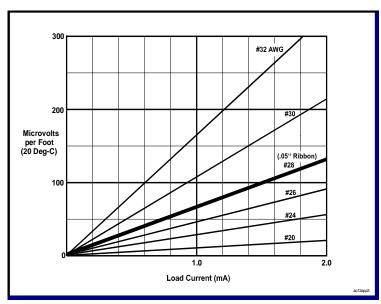

The voltage drop in ribbon cable can be a significant source of error in 16-bit systems, even with relatively short cables driving low-current loads. Figure 2.3-2 shows the effect of load current on the voltage drop in copper wire of various sizes. A 2.0 milliamp load for example, will insert a voltage drop of approximately 130 microvolts *per foot* in conventional #28 AWG ribbon cable; twice that if the return line also is considered. Several feet of ribbon cable therefore can produce significant errors in a 16-bit system, in which 1 LSB may represent only 76 microvolts (±2.5 Volt range). High impedance loads however, generally will not produce significant DC line loss errors.

Figure 2.3-2. Line Loss Versus Load Current

# 2.3.1.3 Remote Ground Sensing

In single-ended applications, if a significant potential difference is expected between the ground connection at the load and the output return from the board, the use of remote ground sensing should be considered. When remote ground sensing is enabled through application software, the input signal at the REM GND SENSE pin in the I/O connector adjusts the output voltages of single-ended channels to compensate for a ground potential at the load.

To provide correction for the potential difference between the analog output return and the remote system ground, the REM GND SENSE input must be connected to the remote system ground, and remote sensing must be enabled by the control software. If remote ground sensing is not implemented, the REM GND SENSE input should be connected to OUTPUT RETURN.

The remote sensing input affects all analog output channels, and consequently can be a significant source of noise if not adequately protected from external sources of interference.

# NOTE: Remote ground sensing is disabled for differential output channels.

### 2.3.2 External Clock and Trigger I/O

External clock and trigger input and output signals are software-selectable as either singleended TTL-compatible, or as low-voltage differential signaling (LVDS)-compatible.

In LVDS mode, the HI and LO pins in each pair correspond to the standard "+" and "-" LVDS signals, respectively. LVDS inputs are terminated internally with 100 Ohms.

In TTL mode, the clock and trigger signals use the corresponding "HI" I/O pins, and the "LO" pins should be grounded to digital return. TTL inputs are pulled HIGH internally through approximately 5K-Ohms

#### 2.3.2.1 Sample Clock Output

The DAC CLOCK OUT signal generates a 100-150ns low-going pulse each time the analog outputs are updated, and can be used to synchronize the analog output clocking of multiple *clock target* boards to a single *clock initiator*.

#### 2.3.2.2 Burst Trigger I/O

If burst triggering is enabled by the control software, an external TTL or LVDS signal can initiate a data burst by applying a HIGH-to-LOW transition on the TRIGGER INP pin in the I/O connector. In order for the trigger input to be acknowledged, the TRIGGER OUT signal must be HIGH, and the TRIGGER INP signal must go low for a minimum interval of 70 nanoseconds.. TRIGGER OUT goes LOW at the beginning of a burst, and returns HIGH when the burst is completed.

To use the TRIGGER OUT as the *sync* input to an SDI-series sigma-delta board, connect the TRIGGER OUT HI and LO outputs to the SYNC LO and HI inputs, respectively, of the SDI board.

# 2.3.3 Multiboard Synchronization

#### 2.3.3.1 Synchronized Bursts

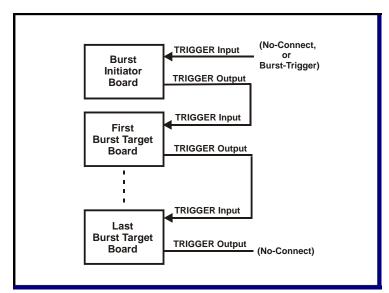

If multiple boards are to be burst-synchronized together, the TRIGGER OUT signal from a single *burst-initiator*, is connected to the TRIGGER IN pin of the first board in a series of *burst targets* (Figure 2.3-3). The TRIGGER OUT from each target is connected to the TRIGGER IN of the next target board in the series, and the TRIGGER OUT of the last target is left unconnected. When operating in this *triggered-burst* mode, each burst-target will initiate a single burst from its buffer each time the burst-initiator initiates a burst. The initiator can be configured for either continuous or burst operation.

#### 2.3.3.2 Synchronized Clocks

To clock-synchronize multiple boards together, the DAC CLOCK OUT from a *clock initiator* is connected directly to the CLOCK IO pin of the first target board in a series of *clock targets*. The DAC-CLOCK OUT from each target is connected to the CLOCK IO pin of the next target in the series, and the CLOCK-IO pin of the last target is left unconnected. This mode is configured by the application software as shown in Table 3.10-2.

Figure 2.3-3. Multiboard Burst Synchronization

A clock target can be clocked by a HI-to-LO transition from any external TTL or LVDS signal source connected to the CLOCK IO input. The input signal is edge-detected, and must be low for a minimum interval of 70 nanoseconds in order to be recognized as a valid clock.

## 2.4 Maintenance

This product requires no scheduled hardware maintenance other than periodic reference verification. The optimum verification interval will vary, depending upon the specific application, but in most instances an interval of one year should be sufficient. In the event of a suspected malfunction, all associated system parameters, such as power voltages, control bus integrity, and input signal levels, should be evaluated before troubleshooting of the board itself is attempted. A board that is suspected to be defective should be returned to the factory for problem analysis and repair.

# 2.5 Reference Verification

All output channels are software-calibrated to an internal voltage reference (Vtest) by an embedded autocalibration firmware utility. The verification procedure presented here describes the adjustment of the reference. For applications in which the system must not be powered down, the board can be calibrated under normal operating conditions while installed on the existing host board.

To eliminate the requirement for a special test connector, the two test points required for calibration, VTEST OUT and VTEST RETURN, can be made available at a system breakout connector or test panel. This arrangement also eliminates the necessity of disconnecting the system input/output cable for reference verification or adjustment.

## 2.5.1 Equipment Required

Table 2.5-1 lists the minimum equipment requirements for verifying and adjusting the internal voltage reference. Alternative equivalent equipment may be used.

| Table 2.5-1. Reference Verification Equipment |

|-----------------------------------------------|

|-----------------------------------------------|

| EQUIPMENT DESCRIPTION                                                                                                                                                                   | MANUFACTURER    | MODEL       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|

| Digital Multimeter, 5-1/2 digit, 0.005% accuracy for DC voltage measurements at ±10 Volts.                                                                                              | Hewlett Packard | 34401A      |

| PCI expansion slot 33MHz or 66MHz; 32-Bit.                                                                                                                                              | (Existing host) |             |

| Standard 68-Pin, 0.05", dual-ribbon cable<br>connector, with test leads. (Not required if<br>calibration test points are made<br>permanently available at a system<br>connection point) | Amp             | #1-746288-0 |

## 2.5.2 Verification Procedure

The following procedure describes the single adjustment that is necessary to ensure conformance to the product specification.

Adjustment of the internal reference (Vtest) is performed with a single adjustment trimmer that is accessed as shown in Figure 2.5-1. The adjustment seal on the trimmer should be removed before beginning the procedure, and the trimmer should be resealed with a suitable sealing agent after the adjustment has been completed. Thread-locking agents should not be used.

Figure 2.5-1. Reference Adjustment Access

This procedure assumes that the board to be verified is installed on a host board, and that the host is installed in an operating system. The board can be operating in any mode when the adjustment is performed.

- 1. Connect the digital multimeter between the VTEST OUT (+) and VTEST RETURN (-) pins in the system I/O connector. Refer to Table 2.2-1 for pin assignments.

- 2. If power has been removed from the board, apply power now and wait at least 15 minutes before proceeding.

- 3. The digital multimeter indication should indicate +9.9900 ±0.0010 VDC for the High-Level range option, or +2.4975 ±0.0010 VDC for the High-Current option. If the indication is not within this range, adjust the reference trimmer until an in-range indication is obtained..

- 4. Reference verification or adjustment is completed. Remove all test connections.

# **SECTION 3.0**

# CONTROL SOFTWARE

## 3.1 Introduction

The PCI66-16AO16FLV is compatible with the PCI Local Bus specification revision 2.3 for D32 transfers at 33MHz or 66MHz. The PCI interface is controlled by a PLX<sup>™</sup> PCI-9056 PCI adapter. Configuration-space registers are initialized internally to support the location of the board on any 8-longword boundary in memory space. DMA access is supported for data transfers to the analog output data buffer.

After initialization, communication between the PCI bus and the board takes place through the control and data registers shown in Table 3.1-1. All data transfers are long-word D32. Reserved bits in each register are ignored during write operations, and are forced LOW during read operations. To ensure compatibility of applications with subsequent product upgrades, reserved bits should be written as LOW.

| OFFSET | REGISTER                | MODE* | DEFAULT    | PRIMARY FUNCTION                           |

|--------|-------------------------|-------|------------|--------------------------------------------|

| 00     | BOARD CONTROL (BCR)     | R/W   | 0000_0810h | Board Control Register (BCR)               |

| 04     | CHANNEL SELECTION       | R/W   | 0000_FFFFh | Channel-enabling mask                      |

| 08     | SAMPLE RATE             | R/W   | 0000_0096h | Analog output clocking rate selection      |

| 0C     | BUFFER OPERATIONS       | R/W   | 0000_340Fh | Buffer size selection and status flags     |

| 10     | Firmware and Options ** | RO    | 00XX_XXXh  | Firmware revision and hardware options     |

| 14     | Autocal Values **       | R/W   | 0000_0XXXh |                                            |

| 18     | OUTPUT DATA BUFFER      | WO    | 0000_0000h | Analog output FIFO buffer                  |

| 1C     | ADJUSTABLE CLOCK        | R/W   | 0000_0000h | Control of the adjustable clock generator. |

## Table 3.1-1. Control and Data Registers

\* R/W = Read/Write; RO = Read-only; WO = Write-only.

\*\* Maintenance register; shown for reference.

# 3.2 Board Control Register

The Board Control Register (BCR) controls primary board functions, including burst control, autocalibration, and interrupt event selection. Table 3.2-1 provides a brief description of each bit field in the BCR, as well as indicating an associated section in the text.

# 3.3 Configuration and Initialization

#### 3.3.1 Board Configuration

During *board configuration*, initial values for both the PCI configuration registers and the internal control logic are extracted from internal nonvolatile read-only memory. This process is initiated by a PCI bus reset, and should be required only once after the initial application of power. While the PCI configuration registers are being loaded, the response to PCI target accesses is RETRY's. Configuration operations are executed in the sequence shown in Table 3.3-1.

| Offset: | 0000h |                                                                                                                                                                                                      |     | Default: 0000_(                                                                                                                                                                                     | 0810h           |

|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| BIT     | MODE  | DESIGNATION                                                                                                                                                                                          | DEF | DESCRIPTION                                                                                                                                                                                         | REF             |

| D00     | R/W   | BURST ENABLED                                                                                                                                                                                        | 0   | Selects burst-mode if HIGH, continuous-mode if LOW.                                                                                                                                                 | 3.4.4,<br>3.4.5 |

| D01     | RO    | BURST READY 0 If HIGH, indicates that a burst trigger will be accepted. If LOW, indicates that a burst is in progress, and that a trigger will not be accepted. Available as an interrupt condition. |     |                                                                                                                                                                                                     |                 |

| D02     | R/W   | *BURST TRIGGER                                                                                                                                                                                       | 0   | Software burst trigger, asserted HIGH. Active only when BURST ENABLED is asserted.                                                                                                                  |                 |

| D03     | R/W   | REMOTE GROUND SENSE                                                                                                                                                                                  | 0   | Correction is made for remote ground potentials when this bit is HIGH.                                                                                                                              | 3.7             |

| D04     | R/W   | OFFSET BINARY                                                                                                                                                                                        | 1   | Selects offset-binary data format when asserted HIGH, or two's complement when LOW.                                                                                                                 | 3.4.1.3         |

| D05     | R/W   | DIFFERENTIAL SYNC I/O                                                                                                                                                                                | 0   | Selects differential (LVDS) external clock/trigger I/O when high, or TTL clock/trigger I/O when low.                                                                                                | 3.4.5           |

| D06     | R/W   | DISABLE EXT BURST TRIG                                                                                                                                                                               | 0   | Disables external burst trigger input.                                                                                                                                                              | 3.4.4.2         |

| D07     | R/W   | SIMULTANEOUS OUTPUTS                                                                                                                                                                                 | 0   | When HIGH, selects simultaneous output                                                                                                                                                              | 3.4.3.2,        |

|         |       |                                                                                                                                                                                                      |     | clocking. When LOW, selects sequential clocking.<br>Default is LOW; i.e.: sequential.                                                                                                               | 3.4.3.3         |

| D08-D10 | R/W   | INTERRUPT A0-A2                                                                                                                                                                                      | 0   | Interrupt event selection.                                                                                                                                                                          | 3.6             |

| D11     | R/W   | INTERRUPT REQUEST FLAG                                                                                                                                                                               | 1   | Set HIGH when the board asserts an interrupt request. Clears the request when cleared LOW by the bus.                                                                                               |                 |

| D12     | R/W   | (Reserved)                                                                                                                                                                                           | 0   |                                                                                                                                                                                                     |                 |

| D13     | R/W   | * AUTOCALIBRATION                                                                                                                                                                                    | 0   | Initiates autocalibration. Completion is available as an interrupt condition.                                                                                                                       | 3.5             |

| D14     | RO    | AUTOCAL STATUS FLAG                                                                                                                                                                                  | 0   | Records the status of autocalibration; LOW for pass, HIGH for fail.                                                                                                                                 |                 |

| D15     | R/W   | *INITIALIZE                                                                                                                                                                                          | 0   | Initializes the board when set HIGH.<br>Sets all defaults for all registers.                                                                                                                        | 3.3.2           |

| D16     | R/W   | OUTPUT RANGE                                                                                                                                                                                         | 0   | Selects the output voltage range as:<br>High-Level Outputs:<br>$0 \Rightarrow \pm 5V$ , $1 \Rightarrow \pm 10V$ ,<br>High-Current Outputs:<br>$0 \Rightarrow \pm 1.5V$ , $1 \Rightarrow \pm 2.5V$ . | 3.4.1.4         |

| D17     | R/W   | (Reserved)                                                                                                                                                                                           | 0   |                                                                                                                                                                                                     |                 |

| D18-D19 | R/W   | OUTPUT FILTER                                                                                                                                                                                        | 0   | Selects the output filter for all channels:<br>0 => Direct outputs; No filter,<br>1 => Direct outputs; No filter,<br>2 => Filter-A,<br>3 => Filter-B.                                               | 3-12            |

| D20-D31 |       | (Reserved)                                                                                                                                                                                           | 0   | Inactive. Returns all-zero.                                                                                                                                                                         |                 |

# Table 3.2-1. Board Control Register

#### Default: 0000 0810h

$^{\ast}\,$  Cleared automatically when operation is completed.

R/W = Read/Write; RO=Read-Only.

Board configuration terminates with the PCI interrupts disabled. Attempts to access the local bus during configuration should be avoided until the PCI interrupts are enabled and an initialization-complete interrupt request is asserted.

| Operation                                                | Maximum Duration |

|----------------------------------------------------------|------------------|

| PCI configuration registers are loaded from internal ROM | 3 ms             |

| Internal control logic is configured from internal ROM   | 300 ms           |

| Internal control logic is initialized                    | 3 ms             |

Table 3.3-1.

Configuration Operations

Loading of the PCI configuration registers is completed within 3 milliseconds or less after the assertion of a PCI bus reset, and should be required only once after the initial application of power. PCI register configuration terminates with the PCI interrupts disabled (Paragraph 3.6).

# 3.3.2 Initialization

Internal control logic can be initialized without invoking configuration by setting the INITIALIZE control bit in the BCR. This action causes the internal logic to be initialized, but does not affect the PCI configuration registers and does not reconfigure the internal control logic. Initialization requires 3 milliseconds or less for completion, and produces the following default conditions:

- The BCR is initialized; all defaults are invoked (Paragraph 3.2),

- All analog outputs are set to zero-level (3.4.1.1),

- All channels are active (3.4.1.1.1),

- Data coding format is offset binary (3.4.1.3.2),

- The low output range (±1.5V or ±5V) is selected (3.4.1.4),

- The analog output buffer is reset to empty (3.4.2),

- Buffer configuration is open (3.4.2.4), with maximum size selected (3.4.2.2),

- Internal clocking is selected (3.4.3.1), and clocking is disabled (3.4.3),

- The clocking rate generator is adjusted to 152.880KSPS (3.4.3.1.2),

- Clocking mode is sequential (3.4.3.3) and continuous (3.4.4.1),

- TTL sync I/O logic is selected (3.4.5),

- The local interrupt request is asserted (ignored unless PCI interrupts are enabled) (3.6),

- Remote ground sensing is disabled (3.7).

- The adjustable clock rate generator is disabled (3.10),

- Direct outputs are selected, and the output filters are disabled (3.12).

Upon completion of initialization, the INITIALIZE control bit in the BCR is cleared automatically.

### 3.4 Analog Output Control

This section describes those operations that control the movement of data from the PCI bus through the analog output buffer. These functions include the selection of active channels, the organization of data within the buffer, and the clocking of data from the buffer to the analog outputs. The principal parameters associated with controlling the analog output channels are summarized below in Table 3.4-1. Section 3.8 provides detailed examples of analog output operations.

| Parameter               | Mode                              | Description                                                                                                                                                                                                                |

|-------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Control            | Active Channels;<br>Channel Group | A single set of all active output channels constitutes an <i>Active Channel Group</i> . Active channels are selected under a channel mask.                                                                                 |

|                         | Data Frame                        | All data values in the buffer comprise a Data Frame.                                                                                                                                                                       |

|                         | Data Coding                       | Output data can be coded either in offset-binary format or in two's complement format.                                                                                                                                     |

| Active Buffer           | Size Selection                    | The active buffer is a subset of the physical output data buffer.<br>Active buffer size is determined by the SIZE[30] control-bit field in<br>the buffer operations register.                                              |

|                         | Status Flags                      | Status flags buffer-empty, buffer-low-quarter, buffer-high-quarter and buffer-full are provided for the active buffer.                                                                                                     |

| Buffer<br>Configuration | Open                              | Data read from the buffer is used and then discarded, until the buffer is empty.                                                                                                                                           |

|                         | Circular (closed)                 | Data within the buffer is recirculated. Each value read from the output of the buffer FIFO is written back to the input of the FIFO. An end-of-frame (EOF) flag tracks the movement of data through the buffer.            |

| Clock Source            | External                          | External hardware provides the sample clock.                                                                                                                                                                               |

|                         | Internal                          | The sample clock is provided by an internal rate generator, at a rate determined by the sample rate control register.                                                                                                      |

| Clocking Mode           | Simultaneous                      | At each clock occurrence, the next channel group (i.e.: a single group of all active channel values) in the output buffer is transferred to the respective analog output channels. All outputs are updated simultaneously. |

|                         | Sequential                        | At each clock occurrence, the next active channel value in the output buffer is transferred to the associated analog output channel, which is updated immediately.                                                         |

| Sampling Mode           | Continuous                        | The contents of the output buffer are sampled continuously at the selected clock rate.                                                                                                                                     |

|                         | Triggered Burst                   | A single data frame in the buffer is clocked to the outputs.                                                                                                                                                               |

| Table 3.4-1. | Summary of | <b>Output Control</b> | Parameters |

|--------------|------------|-----------------------|------------|

|--------------|------------|-----------------------|------------|

### 3.4.1 Data Organization

#### 3.4.1.1 Active Channels

Analog output data is loaded into the output buffer in discrete groups, or frames, of channel data. An active *channel group* consists of a single set of output values for all active channels.

Only active output channels receive data from the output buffer. A channel that is deselected to the inactive state retains the last value that was received while the channel was still active. During initialization, all channels are selected as active and are set to midrange (zero output level).

#### 3.4.1.1.1 Selection

Offset: 0004h

An output channel is selected as *active* by setting the corresponding ENABLE CHANNEL XX selection bit HIGH in the Channel Selection Register, as shown in Table 3.4-2. A channel is deselected to the *inactive* state by clearing the corresponding selection bit. To select Channels 3, 9 and 14 as active for example, the Channel Selection register would have the value 0000\_4208h.

Channels 00-07 are available with 8-Channel boards, and Channels 00-11 are available with 12-Channel boards.

| BIT         | MODE | DESIGNATION          | DESCRIPTION                                                    |

|-------------|------|----------------------|----------------------------------------------------------------|

| D00         | R/W  | ENABLE CHANNEL 00    | Channel-Enable mask. A channel is enabled if the               |

| D01         | R/W  | ENABLE CHANNEL 01    | associated mask bit is HIGH, or is disabled if the bit is LOW. |

| D02         | R/W  | ENABLE CHANNEL 02    |                                                                |

| D03         | R/W  | ENABLE CHANNEL 03    |                                                                |

| D04-<br>D15 | R/W  | ENABLE CHANNEL 04-15 |                                                                |

| D16-<br>D32 | RO   | (Reserved)           | Inactive. Returns all-zero.                                    |

### Table 3.4-2. Channel Selection Register

#### Default: 0000 FFFFh

#### 3.4.1.1.2 Loading

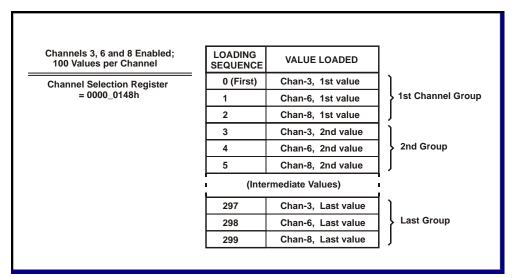

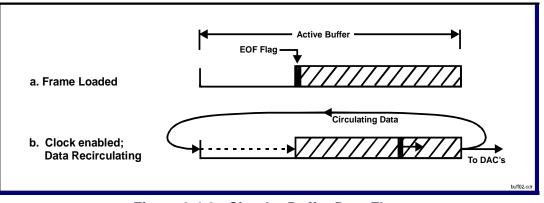

Channel data values are loaded into the output buffer in ascending order of the active channels. The channel groups are loaded contiguously, beginning with the first group to be transferred to the outputs, and proceeding sequentially to the last group. Figure 3.4-1 illustrates a loading example that represents three active channels, with 100 values per channel. Each channel group consists of active channels 3, 6 and 8, and consequently the value in the channel selection register is 0000\_0148h.

Figure 3.4-1. Typical Buffer Loading Sequence

#### 3.4.1.2 Data Frame

A data frame consists of an integral number of contiguous channel groups.

For triggered bursts, or for function concatenation, the last active channel in the last channel group is designated as the *end-of-frame* (EOF). The EOF designation is applied by setting the EOF flag (D16) HIGH when loading the last channel value into the buffer. Thereafter, the EOF flag follows the last channel value through the buffer.

#### 3.4.1.3 Output Data Format

#### 3.4.1.3.1 Output Data Buffer

Analog output data values are written in word-serial sequence from the PCI bus to the Output Data Buffer register shown in Table 3.4-3. Bits D15..0 represent the output data value. Bit D16 is set HIGH to indicate the last value in a data frame, and is the end-of-frame (EOF) flag. Bits D31..17 are inactive and have no effect. Access to the output buffer is supported for both single-longword transfers and single-address multiple-longword DMA transfers.

| Offset: 001 | 8h | ·                 | Default: N/A (Write-Only)  |

|-------------|----|-------------------|----------------------------|

| BIT MODE*   |    | DESIGNATION       | DESCRIPTION                |

| D00         | WO | DATA 00           | Least significant data bit |

| D01-D14     | WO | DATA 01 - DATA 14 | Intermediate data bits     |

| D15         | WO | DATA 15           | Most significant data bit  |

| D16         | WO | EOF FLAG          | End-of-frame (EOF) flag.   |

| D17-D31     | WO |                   | (Inactive)                 |

\* WO indicates write-only access. Read-access returns all-zero value.

# 3.4.1.3.2 Output Data Coding

Analog output data can be coded either in 16-bit offset binary format (Table 3.4-4) by asserting the OFFSET BINARY control bit HIGH in the BCR, or in two's complement format by clearing the control bit LOW. Analog output data transactions are D32 (32 bits), but the data significance is 16 bits.

| ANALOG OUTPUT LEVEL             | DIGITAL VALUE (Hex) |                  |

|---------------------------------|---------------------|------------------|

|                                 | OFFSET BINARY       | TWO'S COMPLEMENT |

| Positive Full Scale minus 1 LSB | XXXX FFFF           | XXXX 7FFF        |

| Zero plus 1 LSB                 | XXXX 8001           | XXXX 0001        |

| Zero                            | XXXX 8000           | XXXX 0000        |

| Zero minus 1 LSB                | XXXX 7FFF           | XXXX FFFF        |

| Negative Full Scale plus 1 LSB  | XXXX 0001           | XXXX 8001        |

| Negative Full Scale             | XXXX 0000           | XXXX 8000        |

Table 3.4-4.

Output Data Coding; D15..D00

*Positive Full Scale* is a positive level that equals the range option defined for the board (e.g.:  $\pm 5.000$  Volts for the  $\pm 5V$  option). *Negative Full Scale* is the negative equivalent of positive full-scale. *Full-scale Range* (FSR) is the total voltage range for the output channel. One LSB equals the full-scale range divided by 65,536. (e.g.: 152.59 microvolts for the  $\pm 5V$  option).

#### 3.4.1.4 Voltage Range Selection

The OUTPUT RANGE control bit in the BCR selects the output range for all channels as  $\pm 10V$  or  $\pm 5V$  for the High-Level range option, or as  $\pm 2.5V$  or  $\pm 1.5V$  for the High-Current option. To minimize potential stresses on sensitive load networks, the board initializes to the lowest available range.

For maximum accuracy, autocalibration should always be performed after a new output range is selected.

#### 3.4.2 Output Buffer

The *physical output buffer* consists of a 17-bit wide FIFO that has a capacity of 256K output values. Each output value is 16 bits wide and occupies a single location within the FIFO. The 17th bit is an end-of-frame flag that is attached to the last value in a data frame (Table 3.4-3). Data values are transferred from the PCI bus to the analog output channels through an *active buffer*, which is a subset of the physical buffer.

#### 3.4.2.1 Buffer Operations Register

The *buffer operations register* (BOR) controls the configuration of the output buffer, as well as related functions such as clocking and loading.

| Table 3.4-5. | Buffer | Operations | Register |

|--------------|--------|------------|----------|

|--------------|--------|------------|----------|

Offset: 000Ch

#### Default: 0000\_340Fh

| BIT     | MODE | DESIGNATION            | DEF | DESCRIPTION                                                                                                                                                                                                                                     |  |

|---------|------|------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D00-D03 | R/W  | SIZE 00-SIZE 03        | Fh  | Size-selection bit field for the active buffer.<br>Defaults to 256K Samples.                                                                                                                                                                    |  |

| D04     | R/W  | EXTERNAL CLOCK         | 0   | Selects hardware or software clock source when HIGH, or<br>the internal rate generator when LOW. Default is LOW<br>(internal rate generator).                                                                                                   |  |

| D05     | R/W  | ENABLE CLOCK           | 0   | Enables output clocking when HIGH. Disables clocking when LOW. Default is LOW (clocking disabled).                                                                                                                                              |  |

| D06     | RO   | CLOCK READY            | 0   | If external clocking is selected, indicates when HIGH that a hardware or software clock will be accepted. If LOW, indicates that the output is not ready to accept a clock. Active only when external clocking is selected.                     |  |

| D07     | R/W  | *SW CLOCK              | 0   | If external clocking is selected, produces a single output clock event when asserted. Clears LOW automatically when the clock event is completed. Active only when external clocking is selected.                                               |  |

| D08     | R/W  | CIRCULAR BUFFER        | 0   | Selects circular buffer configuration if HIGH, or open self-<br>flushing buffer configuration if LOW. Access for loading new<br>data into the circular buffer must be requested by asserting<br>LOAD REQUEST. Default is LOW; i.e. open buffer. |  |

| D09     | R/W  | *LOAD REQUEST          | 0   | When set HIGH, requests loading access to the circular buffer. Initializes LOW.                                                                                                                                                                 |  |

| D10     | RO   | LOAD READY             | 1   | Set HIGH when the frame index passes through zero, if both CIRCULAR BUFFER and LOAD REQUEST are HIGH. When HIGH, indicates that the circular buffer is ready to accept new data. Available as an interrupt condition. Defaults HIGH.            |  |

| D11     | R/W  | *CLEAR BUFFER          | 0   | Resets the buffer to empty.                                                                                                                                                                                                                     |  |

| D12     | R/W  | BUFFER EMPTY           | 1   | Status flags for the active buffer. Empty, lo-quarter and                                                                                                                                                                                       |  |

| D13     | RO   | BUFFER LOW<br>QUARTER  | 1   | hi-quarter flags are available as interrupt events.                                                                                                                                                                                             |  |

| D14     | RO   | BUFFER HIGH<br>QUARTER | 0   |                                                                                                                                                                                                                                                 |  |

| D15     | RO   | BUFFER FULL            | 0   |                                                                                                                                                                                                                                                 |  |

| D16     | R/W  | BUFFER OVERFLOW        | 0   | Set HIGH when data is written to a full buffer. **                                                                                                                                                                                              |  |

| D17     | R/W  | FRAME OVERFLOW         | 0   | Set HIGH when data is written to a closed buffer. **                                                                                                                                                                                            |  |

| D18-D31 | RO   | (Reserved)             | 0   | Inactive. Returns all-zero.                                                                                                                                                                                                                     |  |

\* Clears LOW automatically when operation is completed.

$^{\star\star}\,$  Remains HIGH until cleared by a direct write as LOW, or by initialization.

#### 3.4.2.2 Active Buffer

The *active buffer* is a virtual buffer that represents a subset of the physical buffer, and which is the working buffer through which all output data flows. The size of the active buffer is adjustable from eight values up to the full size of the physical buffer. The buffer can be cleared to the empty state by setting the CLEAR BUFFER control bit HIGH in the buffer operations register. CLEAR BUFFER clears automatically after the reset operation has been completed.

#### NOTE: Data loss may occur if the buffer is allowed to fill completely.

The active buffer performs exactly like a physical buffer of the same size. That is, a full buffer will accept no further data from the bus, and an empty buffer indicates that all outputs are idle. Buffer status flags (empty, low-quarter, high-quarter and full) respond to the size of the *active buffer*, not to the size of the physical buffer.

Active buffer size is determined by the SIZE[3..0] control bit field in the buffer operations register. Available active buffer sizes are listed in Table 3.4-6.

| SIZE[3:0] | BUFFER SIZE<br>(Total Channel Values) |

|-----------|---------------------------------------|

| 0         | 8                                     |

| 1         | 16                                    |

| 2         | 32                                    |

| 3         | 64                                    |

| 4         | 128                                   |

| 5         | 256                                   |

| 6         | 512                                   |

| 7         | 1024                                  |

Table 3.4-6. Active Buffer Size

| SIZE[3:0] | BUFFER SIZE<br>(Total Channel Values) |

|-----------|---------------------------------------|

| 8         | 2048                                  |

| 9         | 4096                                  |

| А         | 8192                                  |

| В         | 16384                                 |

| С         | 32768                                 |

| D         | 65536                                 |

| E         | 131072                                |

| F         | 262144                                |

#### 3.4.2.3 Status Flags

Status flags for the buffer operate with respect to the active buffer, and can initiate an interrupt request if the active buffer becomes empty, 3/4-full, or less than 1/4-full. These flags are located in the buffer operations register (Table 3.4-5), and are available as interrupt events (Table 3.6-1).

The BUFFER OVERFLOW flag is set HIGH if data is written to a full buffer, and the FRAME OVERFLOW flag indicates that an attempt was made to write data to a closed buffer, each indicating data loss. Once set, each of these flags remains HIGH until written LOW directly from the bus, or by initialization .

#### 3.4.2.4 Open Buffer

Data in an open buffer is discarded as it is used. Consequently, the buffer is self-flushing, and will empty itself unless it is replenished from the bus. This mode of operation permits the continuous flow of data from the PCI bus to the analog outputs. The buffer status flags are useful in this situation, and provide an indication of whether the buffer is empty, less than 1/4 full (low-quarter), greater than 3/4 full (high-quarter), or full. A full buffer will discard additional data from the bus, while an empty buffer indicates that the outputs are idle. The low-quarter and high-quarter flags are used to control data flow through the buffer when generating continuous functions.

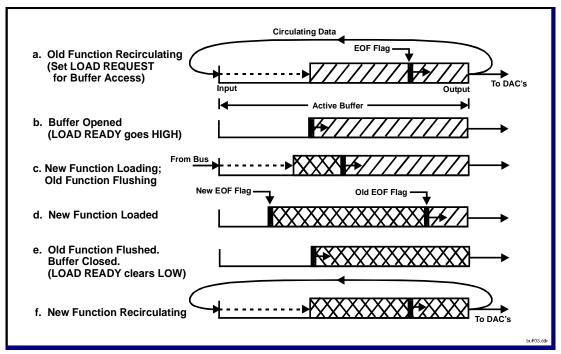

The open-buffer configuration also can be used to produce a one-shot waveform, provided the particular waveform is to be used only once. Figure 3.4-2 illustrates the movement of a single data frame through an open buffer.

#### 3.4.2.5 Circular Buffer

Data in a circular (closed) buffer is retained indefinitely. This configuration generally is implemented to produce either periodic waveforms of constant frequency, or one-shot transient waveforms that will be used repeatedly but not necessarily periodically. While closed, the buffer is not accessible from the bus.

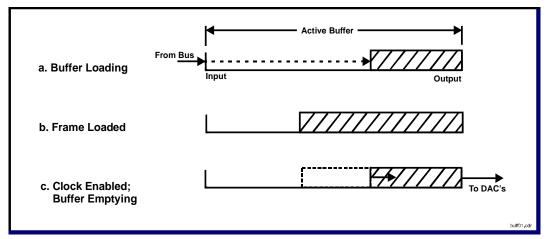

In Figure 3.4-3, a single data frame is loaded into the buffer. The buffer is then closed (CIRCULAR BUFFER set HIGH) and clocking is enabled. The data frame subsequently circulates in the buffer while passing data values to the output channels.

Figure 3.4-2. Open Buffer Data Flow

An end-of-frame (EOF) flag accompanies the end-point, or last value in a data frame. The EOF flag is D16 in the buffer, and is set HIGH when the last value in a data frame is loaded. This flag is used during a triggered burst to define the last value in the burst. Multiple contiguous burst functions can reside in the buffer simultaneously.

Figure 3.4-3. Circular Buffer Data Flow

#### 3.4.3 Output Clocking

When the ENABLE CLOCK control bit in the buffer operations register is asserted HIGH, clocking is enabled and the active analog outputs are updated at each occurrence of the sample clock. The sample clock can be generated internally by the rate generator, or can be supplied externally through the I/O connector. Clocking is disabled when the ENABLE CLOCK control bit is LOW.

# NOTE: Refer to Section 3.10 for additional information pertaining to external clocking configurations, and to operation with the adjustable reference frequency.

Hardware output signal DAC CLOCK OUT (Table 2.2-1) goes LOW momentarily each time a sample clock occurs, Connecting this signal to the CLOCK IO pins of other boards permits synchronous clocking of multiple boards.

#### 3.4.3.1 Clock Source

When buffer operations register bit EXTERNAL CLOCK is HIGH, the sample clock is supplied externally through the I/O connector as CLOCK IO. If the EXTERNAL CLOCK control bit is LOW, the sample clock is derived from the internal rate generator. (See also Section 3.10).

#### 3.4.3.1.1 External Clock

The external clock source can have any frequency up to the maximum value specified for the sampling rate. When the external clock source is selected, sampling occurs on a HIGH-to-LOW transition of the CLOCK IO pin in the I/O connector.

#### 3.4.3.1.2 Internal Rate Generator

The internal rate generator provides a sample clock that is adjustable by the RATE[17..0] control bits in the Sample Rate control register (Table 3.4-7).

| _ | Offset: 000 | 8h                     | Default: 0000_009 |                             |  |

|---|-------------|------------------------|-------------------|-----------------------------|--|

|   | DATA BIT    | A BIT MODE DESIGNATION |                   | DESCRIPTION                 |  |

|   | D00         | R/W                    | RATE 00           | Least significant rate bit  |  |

|   | D01-D16     | R/W                    | RATE 01 - RATE 16 | Intermediate rate bits      |  |

|   | D17         | R/W                    | RATE 17           | Most significant rate bit   |  |

|   | D18-D31     | RO                     |                   | Inactive. Returns all-zero. |  |

Table 3.4-7.

Sample Rate Control Register

The sample rate **Fsamp** is calculated from the relationship:

#### Fsamp (Hz) = 22,932,000 / Nrate ,

where **Nrate** is the decimal equivalent of the value in the RATE value in the Sample Rate control register. Table 3.4-8 illustrates the effect of **Nrate** on the sample rate. Clocking rates above **450 KSPS** can produce unpredictable results and are not recommended. **Nrate** can be changed before or during function generation. Refer to Section 3.10 for operation with the adjustable reference frequency.

| Nrate  | ( RATE[150] ) | SAMPLE RATE Fsamp *             |

|--------|---------------|---------------------------------|

| (Dec)  | (Hex)         | (Samples per Second)            |

| 51     | 00033         | 449,647                         |

| 52     | 00034         | 441,000                         |

|        |               |                                 |

|        |               | Fsamp (Hz) = 22,932,000 / Nrate |

|        |               |                                 |

| 262143 | 3FFFF         | 87.479                          |

\* ±25PPM, or ±5PPM with special order..

#### 3.4.3.2 Simultaneous Clocking

*Simultaneous sampling* is selected by setting the SIMULTANEOUS OUTPUTS control bit in the board control register HIGH. If simultaneous sampling is selected, the analog values in each successive channel group appear simultaneously at the outputs, with minimum time-skew between channels. Upon each occurrence of the sampling clock, an entire active channel group is transferred from the output buffer, and all outputs are updated simultaneously. In this mode, the effective sample rate for each channel equals the sample rate **Fsamp**.

#### 3.4.3.3 Sequential Operation

Sequential sampling is selected when the SIMULTANEOUS OUTPUTS control bit in the board control register is LOW. At each clock occurrence in sequential operation, a single channel value is transferred from the buffer to the associated output channel, and the channel is updated immediately. Channel values are read from the buffer beginning with the lowest-numbered active channel in a channel group, and proceeding upward through the highest-numbered active channel. When operating in this mode, the effective sample rate for each channel equals the sample rate **Fsamp** divided by the number of active channels.

#### 3.4.4 Sampling Mode

#### 3.4.4.1 Continuous Sampling

When the *continuous sampling* mode is selected, data is transferred continuously from the buffer to the analog outputs, assuming that the buffer is not empty and that a sample clock is present. In order for a sample clock to be present, the ENABLE CLOCK control bit in the buffer control register must be HIGH. Continuous sampling is selected when the BURST ENABLED control bit in the board control register is LOW.

#### 3.4.4.2 Data Bursts

During a *triggered burst*, data is transferred continuously from the buffer to the analog outputs until either the *buffer goes empty, or the end-of-frame (EOF) flag is encountered*. In the triggered-burst sampling mode, a software or hardware trigger initiates the transfer of data from the output buffer to the output channels. A software trigger occurs when the BURST TRIGGER control bit in the board control register is set HIGH, whether or not external clocking is selected. The BURST TRIGGER bit remains HIGH during the burst, and clears automatically when the burst is completed.

A hardware burst trigger occurs upon a HIGH-to-LOW transition of the TRIGGER IN pin of the I/O connector, *if* the BURST ENABLED control bit in the BCR is HIGH, *and* if the BURST READY flag in the BCR also is HIGH. The BURST READY flag is LOW during a burst, and is HIGH if no burst is in progress. (The external trigger input can be disabled by setting the DISABLE EXT BURST TRIG control bit HIGH in the BCR).

Hardware output signal TRIGGER OUT is LOW during a burst, and is HIGH when the burst is completed. Connecting this signal to the TRIGGER IN pins of other boards permits synchronous burst triggering of multiple boards.

Multiple burst functions can exist simultaneously within the buffer if the end-of-frame (EOF) flag is used (Paragraph 3.4.1.2). The EOF flag defines the last output value in each data burst. After a burst is triggered, data values from the buffer are clocked to the analog outputs at the selected sample rate until the EOF flag is encountered. The burst then terminates, and clocking of the buffer ceases until a subsequent trigger occurs.

#### 3.4.5 Multiboard Synchronization

Boards that are configured for *synchronous clocking* update their outputs simultaneously in response to a common *clock* signal. Boards that are configured for *synchronous burst triggering* initiate data bursts simultaneously in response to a common *trigger* signal. Multiple boards can be arranged to operate with:

- a. Independent clocking and burst triggering

- b. Synchronous burst triggering (Common burst trigger)

- c. Synchronous clocking (Common DAC clock)

- d. Synchronous clocking and burst triggering (Common trigger and DAC clock).

As many as four boards can be synchronized together. External clock and trigger I/O signaling uses standard TTL levels when the DIFFERENTIAL SYNC I/O control bit is LOW in the BCR, or uses low-voltage differential signaling (LVDS) when the control bit is HIGH.

#### 3.4.5.1 Synchronous Bursts

To **burst-synchronize** a group of boards, the TRIGGER OUT from one board, the *burst-initiator*, is connected to the TRIGGER INP pins of a group *of burst-target* boards. Each burst-target, when operated in the triggered-burst mode (BURST ENABLED set HIGH in the board control register), initiates a single burst from its buffer each time the burst-initiator initiates a burst. The initiator can be configured for either continuous or burst operation.

#### 3.4.5.2 Synchronous Clocking