# Student Papers in Computer Architecture, 2004

# Sandra Taha, Tommy Löfstedt and Ola Ågren (editors)

Technical report, 2005 UMINF 05.27 ISSN 0348-0542

DEPARTMENT OF COMPUTING SCIENCE UMEÅ UNIVERSITY SE-901 87 UMEÅ SWEDEN

COPYRIGHT ©2005

UMINF 05.27 ISSN 0348-0542

# Umeå's Ninth Student Workshop in Computer Architecture

This book is the proceeding from Umeå's Ninth Student Workshop in Computer Architecture. It contains a collection of short technical articles about past and present processors, medias, busses and protocols. The articles have been written by the students of the autumn 2005 offering of the course in Computer Architecture.

#### Introduction

Another year has gone by since the last student workshop in Computer Architectur, and the time has come for a new one. The main topic of the course is still the same (as can be seen above) but one major and some minor changes has been done in the formatting department. This is the first year that we generate one continuous pdf file containing all the reports. This means that a slightly different style file had to be used, and we have had to enforce a stricter set of allowable things to do (no user-defined definitions outside of the bibliographies, labels must be unique, etc.)

The main purpose of this book is to give an overview of the current (and the not so current) state of Computer Architecture as well as to show the effort put into the course by the students. My wish is that the reader might find something interesting to them, something that is worth further research and therefore further enlightenment.

I hope you'll find it a pleasurable book to read.

September 2005 Program committee: Taha, Löfstedt and Ågren

# A Note on Trademarks and Registered Trademarks

All brand names or product names referred to in this work are the property of their respective holders, and their use here should not be seen as a violation of current trademark laws. The program committee takes no responsibility for uses of such names without further references.

CONTENTS

# **Contents**

| I  | Processors                                                             | 1  |

|----|------------------------------------------------------------------------|----|

| 1  | AMD Athlon 64  Johan Lundström & Johan Stenberg                        | 3  |

| 2  | AMD Athlon X2 Dual-Core Oskar Norberg and Robert Johansson             | 7  |

| 3  | ARM7 Björn Hellstrandh and Daniel Wikman                               | 11 |

| 4  | ARM926EJ-S Emanuel Dohi and Mattias Haraldsson                         | 15 |

| 5  | Intel Pentium Pro Daniel Skoglund and Conny Tegström                   | 21 |

| 6  | Intel Pentium III processor Erik Linder and Emanuel Nilsson            | 25 |

| 7  | Intel Pentium D with Dual-Core Freddie Albertsman and Benny Schaerlund | 29 |

| 8  | Intel Itanium (IA-64 Merced) Andreas Mattsson                          | 33 |

| 9  | IBM PowerPC G5 Anton Haglund                                           | 37 |

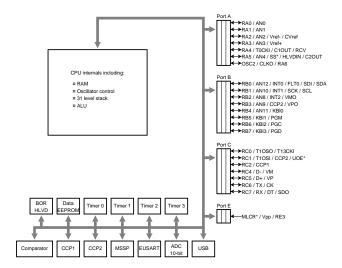

| 10 | Microchip PIC18F2550 Dennis Olsson                                     | 41 |

| 11 | MIPS R5000 Peter Svensson                                              | 45 |

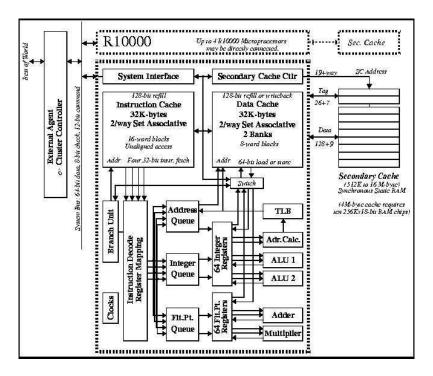

| 12 | MIPS R10000<br>Hannes Kock                                             | 49 |

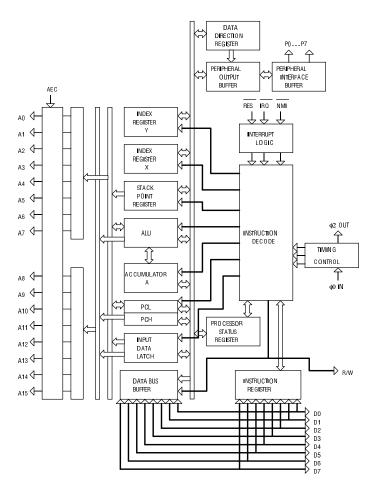

| 13 | MOS Technology 6502<br>Erik Schlyter and Mattias Johansson             | 53 |

| 14 | MOS Technology 6510<br>Markus Eriksson and Dan Kindeborg               | 59 |

| 15 | Motorola 68HC11<br>Jenny Lagerlöf                                      | 65 |

vi CONTENTS

| 16 | Motorola 68000<br>Simon Westerberg                    | 69  |

|----|-------------------------------------------------------|-----|

| 17 | Ricoh 2A03<br>Henrik Tegman and Fredrik Vallström     | 73  |

| 18 | Sun Niagara: A Multithreaded Processor Eva Nylander   | 77  |

| 19 | Transmeta Crusoe<br>Johan Westerlund and Anton Lundin | 81  |

| II | Media and Memory                                      | 85  |

| 20 | Blu-ray<br>Pia Skotare and Johanna Zetterlund Häggrot | 87  |

| 21 | CD-RW<br>Morgan Nätterlund and Patrik Wall            | 91  |

| 22 | DVD<br>Nader Saidi                                    | 95  |

| 23 | SDRAM<br>Kristoffer Cavallin                          | 101 |

| II | Busses and Protocols                                  | 105 |

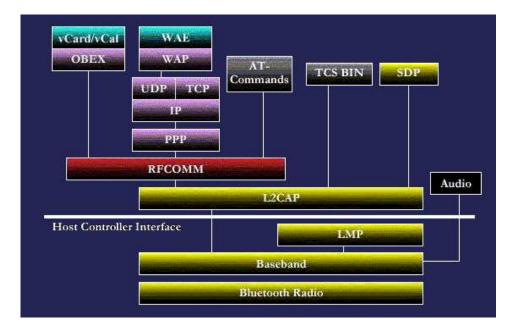

| 24 | Bluetooth<br>Anders Nilsson and Daniel Henriksson     | 107 |

| 25 | FireWire - IEEE 1394  Malin Berggren and Ida Lindahl  | 115 |

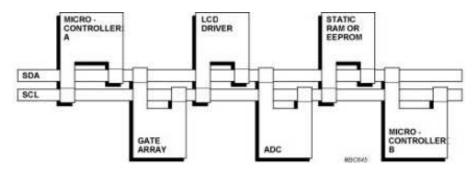

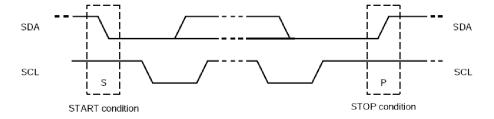

| 26 | I <sup>2</sup> C-bus<br>Erik Waling and P-a Bäckström | 119 |

| 27 | PCI Express Klas Fahlberg and Lars Viklund            | 123 |

| 28 | Serial ATA Emil Ernerfeldt and Mattias Gunnarsson     | 127 |

| 29 | Universal Serial Bus<br>Robert Helgesson              | 131 |

|    | List of Authors                                       | 135 |

# Part I

# **Processors**

# 1. AMD Athlon 64

#### 1.1 Introduction

The AMD Athlon 64 was released on September 23, 2003 and is the first 64-bit processor on the market fully compatible with the 32-bit legacy x86 architecture. This makes any Athlon 64 based system compatible with all existing 32-bit x86 software such as Windows and all its software. The AMD Athlon 64 is used in desktop computers.

The AMD Athlon 64 is built upon the x86-64 architecture which is a extension of the existing x86 architecture and it was developed by Advanced Micro Devices, Inc. as an attempt to create a seamless transaction between the 32- and 64-bit computing platforms. This is because today it would be almost impossible to go to a new pure 64-bit platform, which would require that all software was ported and recompiled. And that is not done overnight [2].

The first 64-bit AMD processor was the Opteron. It was released in April 2003 with clock speeds of 1.4, 1.6 and 1.8 GHz. The 2.0 GHz Athlon 64 and the 2.2 GHz Athlon 64 FX was released in September 2003. The latest addition to the AMD64 family is the dual-core Athlon X2 that was introduced in June 2005. It came in 4 different versions, 4200+, 4400+, 4600+ and 4800+ [4].

#### 1.2 Overview

#### 1.2.1 Registers

When the processor is run in the x86 32-bit legacy mode the processor will have eight 32-bit general purpose registers, eight 64-bit MMX and floating point registers, eight 128-bit SSE extension registers a 32-bit flag register and a 32-bit instruction pointer. This is normal for any modern x86 processor but when the processor is run in 64-bit mode there will be eight more general purpose registers totaling 16 and they will all be 64 bits, there will also be 16 SSE extension registers available and the instruction pointer will be extended to 64 bits [2].

#### 1.2.2 Instruction Formats

The processor can be run in two major modes. The first is 32-bit legacy mode which makes the processor able to run an unmodified 32-bit OS natively. The other mode is long mode where all the x86-64 extensions is enabled. This mode is divided into two submodes, compatibility mode and 64-bit mode. The compatibility mode can be run by a 64-bit OS with 64-bit programs and at the same time run all old 32-bit x86 software which can be run in x86 protected mode. When run in compatibility mode the programs will see it as a x86 protected mode while the OS can use all the 64-bit mechanisms on the processor. The second submode of long-mode is the 64-bit mode which is made for the pure 64 bits applications and in this mode the program can access all the 64-bit extensions.

Defaults 1 Operating Application Mode System Recompile Address Operand GPR Register Required Required Width Extensions<sup>2</sup> (bits) (bits) (bits) 64-Bit yes 64 yes 64 Mode New 32 Long Mode 64-bit OS 32 Compatibility 32 no no Mode 16 32 Legacy 32 32-bit or 16no no Legacy Mode<sup>4</sup> bit OS 16 16

The processor also fully implements SSE1/2, MMX, 3DNow! [1, 2].

- 1. Defaults can be overridden in most modes using an instruction prefix or system control bit.

- 2. Register extensions includes eight new GPRs and eight new XMM registers (also called SSE registers).

- Long mode supports only x86 protected mode. It does not support x86 real mode or virtual-8086 mode. Also, it does not support task switching.

- 4. Legacy mode supports x86 real mode, virtual-8086 mode, and protected mode.

Figure 1.1: Processor operating modes (from [2])

#### 1.2.3 Instruction Set Extensions

#### 3DNow!

3DNow! is a multimedia extension created by AMD in 1998 for their K6 processors. It's an addition of SIMD instructions to the x86 instruction set, to better cope with the vector-processing requirements of many graphic-intensive applications. It was originally developed to extend the integer only MMX instruction set to allow floating-point calculations.

3DNow! have been updated two times. The first "Enhanced 3DNow!" was introduced with the first generation of Athlons and only minor additions were made. The second was introduced with the first Athlon XP processors where they combined their 3DNow! with Intel's SSE1 and called it "3DNow! Professional" [6].

#### SSE1, SSE2 & SSE3

Streaming SIMD Extensions (SSE) was developed by Intel as a reply to AMD's 3DNow! It also replaced the by Intel's generally disappointing MMX set instructions which had two major flaws. First it re-used existing floating-point registers making the CPU unable to work with both floating-point and SIMD data at the same time, and second it only worked with integers. SSE fixed the second issue, that it didn't use floating point numbers, but the first issue was not fixed until the release of SSE2.

SSE also adds eight 128-bit registers called XMM0 through XMM7 that contains four 32-bit single precision floating-point numbers.

SSE2 adds support for 64-bit double precision floating-point and for 64-, 32-, 16- and 8-bit integer operations on the eight XMM registers, this made the MMX instruc-

tion set redundant. This was on the version that Intel developed for their Pentium 4 in 2001. AMD also added support for SSE2 to their Opteron and Athlon 64 in 2003 but they also extended the SSE2 with 8 more XMM registers to a total of 16 to be used while running in 64-bit mode.

SSE3 was introduced with the 64-bit Pentium 4 which added 13 new instructions that simplified the implementations of a number of DSP and 3D operations. The SSE3 is not supported in the 64-bit AMD processors [6].

#### **SIMD**

Single Instruction, Multiple Data (SIMD) is a computing term that refers to operations that efficiently handling of large quantities of data, e.g. adding the same value to large number of data points. SIMD is commonly referred as multimedia instruction set. MMX, SSE, SSE2, SSE3 and 3DNow! are all SIMD instruction sets [6].

## 1.3 Memory Hierarchy

#### 1.3.1 Instruction, Data and 2nd Level Cache

As many modern computers, the memory hierarchy consist of three layers. The fastest is the processor cache, which is made of SRAM, main memory comes second which is made of DRAM and last and slowest is storage memory which is a magnetic disk.

The processor cache is divided into two parts, L1 cache, or primary cache where the instructions and registers are stored and L2 cache, or secondary memory, which is the link between the L1 cache and main memory. SRAM that the processor cache is made of have a typical access time of 0.5 - 5 ns.

Data that is needed by the processor, for example programs, is loaded into the main memory. DRAM have a typical access time of 50 - 70 ns.

In the storage memory is data such as the OS, programs and files stored with a typical access time is 5 - 20 ms.

The AMD Athlon 64 has a 128 kB L1 cache, where 64 kB is for instructions and 64 kB for the registers. It also has 1 MB on-die L2 cache [4, 5].

#### 1.4 Execution

The AMD Athlon 64 processors has 3 integer execution units, where only one have a multiplier and each with an eight entry scheduler. One floating-point execution unit with three pipelines (FADD, FMUL, FMISC) and a 36 entry scheduler.

#### 1.4.1 Pipeline Organization

The first step is to fetch 16 bytes of instruction code from the instruction cache, then it will pick three instructions from the data stream and decode them either as a direct path operation (RISC like) or a vector path operation. The vector path operation is a more complex CISC like operation, which has to be loaded from a microcode ROM

as a microprogram. The hammer architecture introduces a new class of instructions, the double dispatch operations. They are split into two individual operations at the end of the decode stage, thus making the processor capable of starting six operations in a three-way pipeline. The instructions are then packed back into three operations in the following pack stage before the final decode stage.

The operations are then sent to the execution schedulers where they await their dependencies. The schedulers operates in an out-of-order manner meaning, that they will execute a operation in their buffer as soon as their dependencies are solved. When the operations has been executed they will be placed in an reorder buffer where they will wait for all the operations that should have been executed before themselves, prior to being stored in the registers [3, 4].

#### 1.4.2 Branch Prediction

The AMD Athlon 64 has dynamic branch prediction with a 2,048 entry Branch History Table (BHT) and uses the 2-bit Smith Algorithm. The BHT contains information if a branch was recently taken or not. The 2-bit Smith algorithm uses 2 bits to remember if a branch was taken or not, which implies that a branch has to be predicted wrong two times in a row to change prediction for the branch. This implies that you get a much more accurate branch prediction [4, 5].

#### 1.5 References

- [1] ADVANCED MICRO DEVICES. (AMD Athlon 64 processor) Key architectural features, June 17, 2005. http://www.amd.com/us-en/Processors/-ProductInformation/0,30\_118\_9485\_9487%5E9493,00.html.

- [2] CLEVELAND, S. AMD x86-64 technology. White paper, Advanced Micro Devices, Aug. 2000. Available at http://www.amd.com/us-en/assets/content\_type/white\_papers\_and\_tech\_docs/x86-64\_wp.pdf.

- [3] HANS DE VRIES. Understanding the detailed architecture of amd's 64 bit core, Sept. 21, 2003. http://chip-architect.com/news/-2003\_09\_21\_Detailed\_Architecture\_of\_AMDs\_64bit\_Core.html#4.

- [4] LUDLOFF, C. sandpile.org AA-64 implementation AMD K8. Web page, July 26, 2004. http://www.sandpile.org/impl/k8.htm.

- [5] PATTERSON, D. A., AND HENNESSY, J. L. Computer Organization & Design: the Hardware/Software Interface, second ed. Morgan Kaufmann Publishers, Inc., San Francisco, California, 1998.

- [6] WIKIPEDIA. 3DNow! Facts, Info, and Encyclopedia article. Web page, Aug. 31, 2005. http://www.absoluteastronomy.com/encyclopedia/3/3d/3dnow3.htm.

# 2. AMD Athlon X2 Dual-Core

#### 2.1 Introduction

The AMD Athlon X2 Dual-Core processor was released on the ninth of May, 2005 and was a natural successor to the AMD Athlon 64, which in turn was based upon the much celebrated Athlon XP series. AMD's goal has since the late 1990s, when they announced their current architecture, been to put multiple cores on a single processor. The AMD64 architecture, which the Athlon X2 Dual-Core processor is based upon, was designed from the ground up to accommodate the use of multiple cores on a single processor [2].

#### 2.1.1 Overview of the Processor

The Athlon X2 Dual-Core processor has, opposed to Athlon 64 two logical cores for symmetric multiprocessing. Because the Athlon 64 X2 actually consist of two Athlon 64 cores mounted on one and the same chip with some additional control logic, it has inherited the register structure from the AMD64 architecture which is used in Athlon 64. The AMD64 architecture extends the legacy of x86 architecture with sixteen new 64-bit general-purpose integer registers, sixteen new 128-bit XMM¹ registers for enhanced multimedia which includes SSE/SSE2/SSE3² and full 64-bit virtual addressing with 52 bits physical memory addressing. Each core in the processor is equipped with 128 KB L1 cache, 64 KB for instructions and 64 KB for data. It also has, depending on model, 512 KB or 1024 KB L2 cache [1].

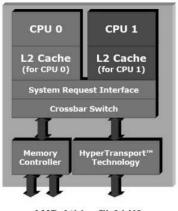

When using the shared resources, the two cores communicate via the special Crossbar-switch and the System Request Queue. They interact with each other on the same level in order to solve cache coherency issues without the involvement of the system bus or the memory bus. Furthermore, communication with the I/O peripherals and the hard drives is done using a single HyperTransport link running at 2 GHz, 1 GHz full duplex to be more precise, and communication with the RAM via the shared Memory Controller at a speed of 6.4 GB/sec [4, 3]. Because the Memory Controller is built in, the processor does not have to go via the northbridge to access the RAM, this means that requests reach RAM faster and data is returned from the RAM more quickly. One effect of the built in Memory Controller is that it benefits from the frequency of the processor. Thus, when the processor clockspeed increases the Memory Controller will go faster, see Figure 2.1 on the following page [5].

<sup>&</sup>lt;sup>1</sup>eXtended Memory Management.

<sup>&</sup>lt;sup>2</sup>Streaming SIMD Extensions.

AMD Athlon™ 64 X2 Dual-Core Processor Design

Figure 2.1: AMD Athlon X2 Dual-Core (from [4])

#### 2.2 Execution

#### 2.2.1 Pipeline

The Athlon X2 Dual-Core has the same pipeline as the Athlon 64. When compared to the old Athlon XP, it is evident that the pipeline has been increased from ten to twelve stages, see Table 2.1 on the next page. The new stages allow the processor to scale to higher clockspeeds then the Athlon XP. The main difference between Athlon X2 Dual-Core and Athlon XP pipelines lies in the first stages [5].

The fetch phase of the Athlon 64 X2 Dual-Core processor fetches 16 byte of instructions from the L1 cache. The fetch phase is divided in two stages to decouple the clockspeed from the L1 cache. In the Pick stage of the pipeline the processor moves the 16 bytes into a 32-byte buffer, appending the new 16 byte with the previous 16-byte group. Then the processor scans the 32-byte buffer after instructions and sorts the instructions into one of two types; those who can be decoded by the Fastpath decoder and those who must be decoded by the microcode engine. The Fastpath decoder and the microcode engine translates the x86 instructions into an internal format that looks like a RISC-format which is easier for the processor to manage and schedule. The Fastpath decoder can handle the shortest and simplest x86 instructions and it can handle up to three instructions at the same time. The microcode engine handles the more complex instructions but it can only handle one instruction per clock cycle [5].

#### 2.2.2 Branch Prediction

The branch prediction of the Athlon 64 X2 architecture has, just like the Athlon XP, two main structures consisting of a local history table and a global history table. The local history table keeps track of the execution history of each individual branch in order to predict whether the branches will be taken or not taken. The global history table keeps

|    | Athlon XP             | Athlon 64 X2 Dual-Core |

|----|-----------------------|------------------------|

| 1  | Fetch                 | Fetch1                 |

| 2  | Scan                  | Fetch2                 |

| 3  | Align1                | Pick                   |

| 4  | Align2                | Decode1                |

| 5  | Decode1 (EDEC)        | Decode2                |

| 6  | Decode2 (IDEC/Rename) | Pack                   |

| 7  | Schedule              | Pack/Decode            |

| 8  | AGU/ALU               | Dispatch               |

| 9  | L1 Address Generation | Schedule               |

| 10 | Data Cache            | AGU/ALU                |

| 11 |                       | Data Cache 1           |

| 12 |                       | Data Cache 2           |

Table 2.1: AMD Athlon XP and Athlon X2 Dual-Core pipelines (from [5])

track of the history of a large number of branches and predicts which way each of these will go by correlating them to the execution histories of the other branches in the table. Furthermore, a branch selector table chooses between the two tables depending upon which of the two prediction schemes that has produced the most accurate result for each branch. This way, superpipelined machines like the Athlon 64 X2 can be provided with just what it needs; a very accurate branch prediction [5].

When compared to the Athlon XP, the number of branch selectors of the Athlon 64 X2 is twice as many and the size of the global history table has quadrupled to over 16 000 entries, which results in an five to ten percent improvement in branch prediction accuracy over the Athlon XP [5].

When the branch predictor decides that a particular branch should continue to execute, it needs to know the address, which can either be specified in the branch instruction itself or be the result of a calculation to which it should jump. In cases where the branch target is the result of a calculation, the Athlon 64 X2 stores the calculated target address in yet another essential structure in the Athlon 64 X2's, as well as the Athlon XP's, branch prediction units, that is called the branch target buffer. As a result, no recalculation of the branch target is needed when, later on in a program execution, a particular branch is reencountered and predicted as taken. Instead it retrieves the address from the branch target buffer [5].

Both the Athlon XP's and the Athlon 64 X2's branch target buffer can hold information about 2048 branches. The branch target buffer of the Athlon 64 X2 is backed up by a branch target address calculator that diminishes the penalty caused by a wrongful prediction when the branch target buffer is holding the incorrect branch target for a branch. This is done by comparing the result given by the branch target address calculator with the branch target produced by the branch target buffer; if the two do not match, then the branch predictor calls mispredict and thereby eludes penalty cycles caused by a wrongful prediction mentioned above [5].

## 2.3 Comparing to the Intel Pentium D

The Pentium D is Intel's contribution to the dual core technology and is the main competitor to the Athlon 64 X2 Dual-Core. The main difference between these two is that the Pentium D has a much longer pipeline, 31 steps compared to 12 steps of the Athlon X2, which in turn leads to an advantage in clock frequency for the Pentium D. The higher clock frequency of the Pentium D has some disadvantages though, it has a larger power consumption then the Athlon X2 and is therefore generating more heat. Another difference is that the Pentium D needs a new Northbridge because it must handle the communications between the cores. All communication between the RAM and the processor must also go through the Northbridge because the Pentium lacks the integrated Memory Controller.

Generally it seems that most people that have compared these two processors have come to the same conclusion; the Pentium D is the best choice when running multiple applications simultaneously on a system due to its HyperThreading technology but when running a single application or two applications the Athlon 64 X2 is the best choice with up to 30 % better performance [6].

#### 2.4 References

- [1] ADVANCED MICRO DEVICES. Athlon 64 X2 Dual-Core Product Data Sheet, May 2005. Also available at http://www.amd.com/us-en/assets/content\_type/white\_papers\_and\_tech\_docs/33425.pdf.

- [2] ADVANCED MICRO DEVICES. *Multi-core processors the next evolution in computing*, May 2005. Also available at http://multicore.amd.com/WhitePapers/-Multi-Core\_Processors\_WhitePaper.pdf.

- [3] FREEMAN, V. Athlon 64 x2 4800+ processor review. Web page, June 22, 2005. http://www.sharkyextreme.com/hardware/cpu/article.php/3514901.

- **AMD** 4800 +[4] GAVRICHENKOV, athlon  $x^2$ dual-I. 64 Aug. processor review. Web page, 5. 2005. http://www.xbitlabs.com/articles/cpu/display/athlon64-x2.html.

- [5] STOKES, J. Inside AMD's Hammer: the 64-bit architecture behind the Opteron and Athlon 64. Web page, Feb. 1, 2005. http://arstechnica.com/articles/paedia/cpu/amd-hammer-1.ars.

- [6] VÖLKEL, F., TÖPELT, B., AND SCHUHMANN, D. Stress test: Athlon 64 x2 4800+ vs. pentium 840 ee. Web page, June 24, 2005. http://www.tomshardware.com/cpu/20050603/index.html.

# **3. ARM7**

#### 3.1 Introduction

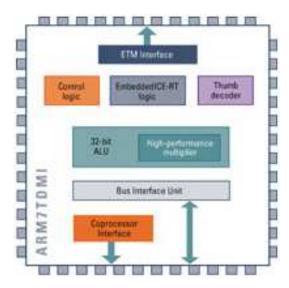

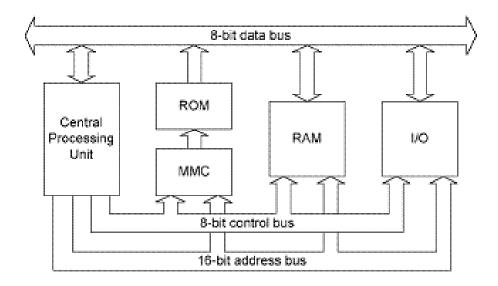

The ARM7 family of processors is one of the most widespread in the world. It is used in many types of embedded systems, especially in portable devices due to its low power consumption and reasonable performance<sup>1</sup>. The ARM architecture features a 32-bit RISC<sup>2</sup> processor with 37 pieces of 32-bit registers, 16 of which is available for the programmer. Due to its simple structure it has reasonably good speed/power consumption ratio.

The ARM company was founded in 1990 after a collaboration project between Apple and Acron on the existing ARM<sup>3</sup> that produced such significant results that it made the companies come together and start the new ARM<sup>4</sup> company. This work eventually led to the release of the ARM6 family which is a predecessor to the ARM7 family. The most successful implementation so far has been the ARM7TDMI which can be found in millions of mobile phones, mp3 players, portable game consoles, to name only a few. Today ARM processors account for 75 % of all 32-bit embedded CPUs [5].

Figure 3.1: ARM7TDMI (from [1])

<sup>&</sup>lt;sup>1</sup>MIPS/Watt.

<sup>&</sup>lt;sup>2</sup>Reduced Instruction Set Computer.

<sup>&</sup>lt;sup>3</sup>At the time Acron RISC Machines.

<sup>&</sup>lt;sup>4</sup>Advanced RISC Machines.

# 3.2 Registers

The ARM7 is a load-store architecture. This means that in order to perform any data processing instructions the data first has to be moved from the memory into a central set of registers. After this the instructions can be executed and the data moved back into the memory. The ARM register structure is dependent of what type of mode is selected. There are seven different modes available in the ARM processor, each of which has their own register availability. In the table below is an overview of the registers available in the different states.

| sys & usr | fiq       | svc       | abt       | irq       | und       |

|-----------|-----------|-----------|-----------|-----------|-----------|

| R0        | R0        | R0        | R0        | R0        | R0        |

| R1        | R1        | R1        | R1        | R1        | R1        |

| R2        | R2        | R2        | R2        | R2        | R2        |

| R3        | R3        | R3        | R3        | R3        | R3        |

| R4        | R4        | R4        | R4        | R4        | R4        |

| R5        | R5        | R5        | R5        | R5        | R5        |

| R6        | R6        | R6        | R6        | R6        | R6        |

| R7        | R7        | R7        | R7        | R7        | R7        |

| R8        | * R8_fiq  | R8        | R8        | R8        | R8        |

| R9        | * R9_fiq  | R9        | R9        | R9        | R9        |

| R10       | * R10_fiq | R10       | R10       | R10       | R10       |

| R11       | * R11_fiq | R11       | R11       | R11       | R11       |

| R12       | * R12_fiq | R12       | R12       | R12       | R12       |

| R13       | * R13_fiq | * R13_svc | * R13_abt | * R13_irq | * R13_und |

| R14       | * R14_fiq | * R14_svc | * R14_abt | * R14_irq | * R14_und |

| R15 (PC)  |

Table 3.1: Register table for different modes (from [2])

Explanations of the different modes in Table  $3.1^5$ :

- User (usr): Normal program execution state.

- FIQ (fiq): Data transfer state.

- IRQ (irq): Used for general interrupt services.

- Supervisor (svc): Protected mode for operating system support.

- Abort mode (abt): Selected when data or instruction fetch is aborted.

<sup>&</sup>lt;sup>5</sup>Register banking (fields marked with an \*) means that there are several copies of the register and whether one is visible depends upon which mode the ARM is in. The reason for having these banked registers is to get faster interrupt handlers and OS services, as these can use their own banked registers without having to save user mode registers.

- System (sys): Operating "privilege" mode for user.

- Undefined: (und): Selected when undefined instructions are fetched.

As we can see in the table there are 16 32-bit registers available in normal (usr) ARM-mode. R0 to R12 are standard registers. The R13 register is always used for the stack pointer, R14 is the link register (it holds the address to return to from a function) and R15 is the program counter (referred to as PC from now on). The R16 is the Current Program Status Register (CPSR) which holds information about the current state the processor is in.

#### 3.3 Instruction Set

The 32-bit ARM instruction set is fully conditional. This means that every instruction is executed with one of sixteen conditional mnemonic in front of them. For instructions that don't need any condition the prefix AL (Always) is used. The advantage with this is that you get a diverse instruction set with the possibility to execute every instruction with a condition, 16 different mnemonics that can be applied to the beginning of the instruction. Another benefit with this is that if an instruction does not satisfy the condition it will be handled like a NOP. This is done to make sure a smooth flow through the pipeline is kept.

## 3.4 Pipelining

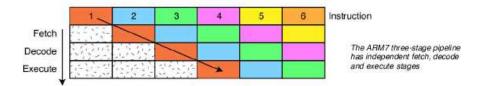

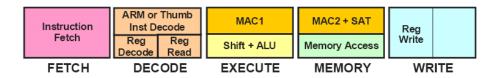

The ARM7 has a three-stage pipeline, consisting of fetch, decode and execute. This allows the CPU to execute one instruction while decoding a second and fetching a third instruction.

Figure 3.2: Illustration of the pipeline in ARM7 (from [3])

The pipeline performs at its best in linear code, as soon as a branch is encountered the pipeline is flushed and needs to be refilled before full execution speed is resumed. Because of the use of a pipeline the programmer needs to be careful when modifying the PC and remember that it is eight bytes ahead of the instruction being executed.

#### 3.5 Thumbs

As mentioned before, the ARM7 is a 32-bit processor, but with the use of Thumbs<sup>6</sup> it has a second 16-bit instruction set. This makes it possible for the processor to cut the memory use with about 30 % when dealing with 16-bit code. On the other hand the normal ARM instruction set is about 40 % faster when dealing with 32-bit code [4]. So the advantage of Thumbs is the possibility to switch between the two instruction sets when dealing with different code.

#### 3.6 References

- [1] ADVANCED RISC MACHINES LIMITED. ARM7TDMI. Web page, Sept. 18, 2005. http://www.arm.com/products/CPUs/ARM7TDMI.html, date visited given.

- [2] ATMEL. *Embedded RISC Microcontroller Core*, Nov. 1999. Also available at http://www.atmel.com/dyn/resources/prod\_documents/0673s.pdf.

- [3] TREVOR MARTIN. The Insider's Guide To The Philips ARM7-Based Microcontrollers. Hitex (UK) Ltd., 2005. Also available at http://www.hitex.co.uk/arm/lpc2000book/lpc-ARM-book\_srn.pdf.

- [4] VILLE PIETKÄINEN. ARM Architecture. PDF presentation, 2002. http://tisu.mit.jyu.fi/embedded/TIE345/luentokalvotEmbedded\_3\_ARM.pdf.

- [5] WIKIPEDIA. ARM architecture, Sept. 18, 2005. http://en.wikipedia.org/-ARM\_architecture, date visited given.

<sup>&</sup>lt;sup>6</sup>Thumbs is to be found in all ARM7 processors with a T following the ARM7.

# 4. ARM926EJ-S

#### 4.1 Introduction

The ARM design was started on in 1983 by Acron Computers Ltd. and in 1985 the team released development samples called ARM1, and the first real production systems called ARM2 the following year. The ARM2 was possibly the simplest useful 32-bit microprocessor in the world at the time, with only 30,000 transistors.

In the late 1980s, Apple Computer started working with Acron on newer versions of the ARM core. The work was so important that Acron spun off the design team in 1990 into a new company called Advanced RISC Machines. This work would eventually turn into the ARM6 with the first models released in 1991. Apple used the ARM6-based ARM 610 as the basis for their Apple Newton PDA in 1994, while Acron used it as the main CPU in their RiscPCs.

The most successful implementation has been the ARM7TDMI with hundreds of millions sold for use in cellular phones. DEC licensed the design and produced the StrongARM. At 233MHz this CPU only consumed 1 watt off power.

The ARM7 family also includes the ARM7TDMI-S and ARM7EJ-S cores and the ARM720T macrocell, each of which has been developed to address different market requirements. This family was later developed into the ARM9 series [10].

#### 4.1.1 ARM9 Processor Family

The ARM7 has only 3 pipeline stages, this was later increased to 5 stages for the ARM9. The ARM9 processor family is built around the ARM9TDMI processor and incorporates the 16-bit Thumb instruction set, which improves code density by as much as 35 % [7].

The ARM926EJ-S processor, which was released on June 13, 2001 [2], and can for example be found in the cellular phone V800 by Sony Ericsson, has extensions such as Jazelle and Digital Signal Processing (DSP). The ARM DSP extensions that offer enhanced 16- and 32-bit arithmetic capabilities within the functionality of the CPU, improves performance and flexibility.

ARM's Java acceleration technology consist of two parts: Jazelle [9], a hardware component and JTEK, a highly optimized software component. These components must be together to provide a complete Java acceleration solution. ARM Jazelle technology provides hardware Java acceleration to deliver significantly higher performance. It dynamically executes some 90 % [8] of Java bytecode directly on the core to give both performance improvement and power savings.

IBM, Texas Instruments, Nintendo, Philips, Atmel, Sharp, Samsung, etc have also licensed the basic ARM design for various uses. The ARM chip has become one of the most used CPU designs in the world, found in a wide variety of devices such as: cell phones, cars, toys, routers etc. Today it accounts for over 75 % [5] of all 32-bits embedded CPUs.

#### 4.2 Overview of the Processor

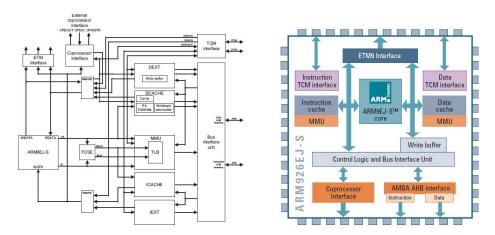

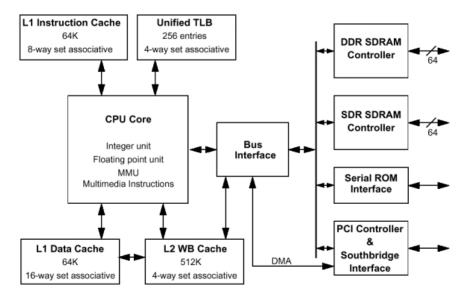

The different details of the ARM926EJ-S that are discussed in this section can be observed in Figure 4.1. More in-depth information can be found in [3, 4, 6].

Figure 4.1: ARM926EJ-S overview (from [3, 6])

#### **4.2.1** Tightly Coupled Memory (TCM)

There is a separate interface, the TCM, which the processor provides access too. The TCM can be used for storing instructions and data. It is designed to allow single cycle access that can be extended by a wait signal which in turn allows nonzero wait state memory to be used, and for DMA-type access to occur.

There is no restriction on the type of memory or memory system attached to the interface other than that it must not contain read-sensitive locations. The physical addresses and write accesses are protected based on the information stored in the Memory Management Unit (MMU). The TCMs are typically used to store critical code and data for which deterministic access times are required, which is not not always the case for code or data that resides in a cacheable region of memory [4].

#### **4.2.2** Memory Management Unit (MMU)

The MMU supports a demand page virtual memory system required by operating systems such as Linux and Windows CE. The MMU provides the access protection mechanism for all memory access. The address translation, protection and region type information is stored in a series of page tables in main memory. The MMU contains hardware for automatically reading and processing these tables, and storing the resulting Translation Look-aside Buffer (TLB) [4].

#### **4.2.3** Caches

The ARM926EJ-S uses separate caches for instructions and data, allowing both an instruction fetch and a load/store access to take place simultaneously. The cache is constructed using standard compiled SRAM blocks, allowing a wide range of processes and libraries to be targeted. The size of each cache can be selected in 4, 8, 16, 32, 64 and 128 kB range. The caches are virtually addressed, with each cache line containing eight words. A cacheable memory region can be defined as either being write-back (copyback) or write-through. This is controlled in the page table entry for the region [4].

#### 4.2.4 Coprocessor

ARM926EJ-S supports the connection of an on-chip coprocessor trough an external coprocessor interface. All ARM processors feature a coprocessor interface to allow the developers the flexibility to enhance the feature set of the core, adding support for new features and extensions to the instruction set [4].

Such an extension is the DSP instruction set that provides the following features:

- 1. 16-bit data operations

- 2. Saturating, signed arithmetic on both 16- and 32-bit data

- 3. Enhanced Multiply Accumulate (MAC) operations

Multiply instructions are processed using single-cycle 32x16 implementation. There are 32x32, 32x16 and 16x16 multiply instructions or Multiply Accumulate (MAC), and the pipeline allows one multiply operation to start each cycle.

#### 4.2.5 Registers

The processor core consists of a 32-bit datapath and associated control logic. The datapath contains 32 registers coupled to a full shifter, Arithmetic Logic Unit (ALU), and multiplier. At any time, 16 registers are visible to the user. The remainder are banked registers used to speed up exception processing [3].

#### 4.3 Execution

Figure 4.2: ARM926EJ-S pipeline (from [1])

The processor core implements a 5-stage pipeline design. It has a Harvard architecture, meaning that data accesses do not have to compete with instruction fetches for the use of one bus. Result-forwarding makes it faster in the sense that results from the ALU and data loaded from memory gets fed back immediately to be used by the following instruction.

In this pipeline design, dedicated pipeline stages have been added for memory access and for writing results back to the register bank, see Figure 4.2 on the preceding page. Register read has been moved back into the decode stage. These changes allow for higher clock frequencies by reducing the maximum amount of logic which must operate in a single clock cycle.

#### 4.4 Performance

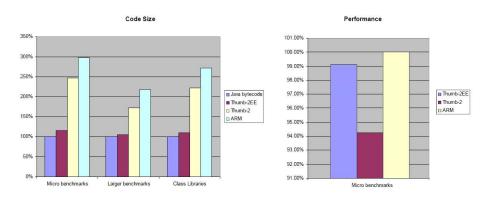

Figure 4.3: ARM926EJ-S performance comparison of both size and speed (from [9])

Figure 4.3 illustrates results from a compilation of Java bytecode using the ARM Ahead Of Time (AOT) compiler. The compiler output includes ARM code, Thumb-2 code and Thumb-2EE (Jazelle RCT) code, the results are shown normalized against the original Java bytecode. Note that this compiler is highly optimized for code density rather than performance, so code bloat for all ISAs is the low end of the possible range [1].

# 4.5 Special

Some of the richer features of this processor is that it can execute 80 % of javas code directly and that it has extensions for both encoding and decoding of MPEG4.

#### 4.6 References

- [1] ADVANCED RISC MACHINES LTD. *Product Comparison*, Sept. 2, 2000. Also available at http://www.arm.com/comparison-arm7-arm9-v1.pdf.

- [2] ADVANCED RISC MACHINES LTD. ARM discloses technical details of ARM926EJ-S core. Web page, June 13, 2001. http://www.us.design-reuse.com/news/news631.html.

- [3] ADVANCED RISC MACHINES LTD. ARM926EJ-S Product Overview, Sept. 19, 2001. Also available at http://www.arm.com/pdfs/DVI0035B\_926\_P0.pdf.

- [4] ADVANCED RISC MACHINES LTD. ARM926EJ-S Technical Reference Manual, Jan. 26, 2004. Also available at http://www.arm.com/pdfs/DDI0198D\_926\_TRM.pdf.

- [5] ADVANCED RISC MACHINES LTD. ARM CPU:s information. Web page, Sept. 19, 2005. http://www.arm.com/products/CPUs/index.html, date visited given.

- [6] ADVANCED RISC MACHINES LTD. ARM926EJ-S. Web page, Sept. 19, 2005. http://www.arm.com/products/CPUs/ARM926EJ-S.html, date visited given.

- [7] ADVANCED RISC MACHINES LTD. ARM926EJ-S architecture. Web page, Sept. 19, 2005. http://www.arm.com/products/CPUs/architecture.html, date visited given.

- [8] ADVANCED RISC MACHINES LTD. Foundry program. Program flyer, Sept. 19, 2005. Also available at http://www.arm.com/pdfs/foundry%20program%20flyer%2099-6.pdf.

- [9] PORTHOUSE, C. Jazelle technology: ARM acceleration technology for the Java Platform. Advanced RISC Machines Ltd, Sept. 2004. Also available at http://www.arm.com/pdfs/Jazelle%20RCT%20White%20Paper%20\_final%201.0\_.pdf.

- [10] WIKIPEDIA. ARM architecture. Web page, Sept. 21, 2005. http://en.wikipedia.org/wiki/ARM\_family.

# 5. Intel Pentium Pro

#### 5.1 Introduction

The Pentium Pro processor by Intel is a sixth-generation x86 microprocessor that replaced its predecessor the original Pentium processor. The difference between the Pentium Pro and its predecessor is, despite the name, actually quite big. Based on the then new P6-core Pentium Pro uses the same core as the later Pentium II, Pentium III and Pentium M. So when the Pentium Pro was introduced in 1995 it was a big step for the Pentium processor family. Pentium Pro introduced several unique architectural features that had not been seen in any PC processor before.

#### 5.2 Overview of the Processor

Using a new way of processing instructions and several other technical advances the Pentium Pro achieves approximately 50 % higher performance than a Pentium of the same clockspeed. Some of the advances that contribute to the increased performance are [4]:

- 1. **Superpipelining:** To compare with the Pentium processor, which uses 4 execution steps in pipelining, Pentium Pro uses 14.

- 2. Out of Order Completion: The executions can be completed out of order.

- 3. Register renaming: This makes parallel performance of the pipelines better.

- 4. **Speculative Execution:** To reduce pipeline stall time in the core, the Pentium Pro uses speculative execution.

- 5. **Superior Branch Prediction Unit:** The Pro has a branch target buffer that is two times the Pentium's and its accuracy is increased.

- 6. **Wider Address Bus:** With a 36 bits address bus the Pentium Pro can address up to 64 GB of memory.

- 7. **Integrated Level 2 Cache:** A then new level 2 cache memory is used in the Pentium Pro. It uses integrated level 2 cache, which runs at the full processor speed, instead of using the motherboard-based cache that runs at the speed of the memory bus. The cache memory of Pentium Pro is also non-blocking, this makes the processor continue without waiting on a cache miss.

- 8. **32-Bit Optimization:** When the Pentium Pro was released most software used 32-bit code and because of that the Pentium Pro is optimized for that.

#### **5.2.1** Implementations

When the Pentium Pro was released it was mainly designed for high-end servers and workstations, because it was optimized for 32-bit code, preferably those computers that was using windows NT and UNIX systems. This made the processor poorly suitable for 16-bit code. When the Pro was released it was not well positioned to compete in the desktop market, because most desktops used Windows 3.1, which is using only 16-bit

code, and Windows 95, which was new at that time and therefore also using most 16-bit programs. To make a new processor improvement suitable for the desktop market Intel released Pentium MMX as the successor for the original Pentium. Today Pentium Pro still is popular for servers because its low costs [6].

## 5.3 Memory Hierarchy

#### 5.3.1 Register

The registers of the processor is the at the top level of the memory hierarchy. It is the register that provides the fastest access to data possible on the 80x86 CPU. The register is also the smallest memory in the hierarchy of the CPU with a size of 32 bits for the Pentium Pro. The register is a very expensive memory [1].

#### 5.3.2 Level 1 Cache

The next level of memory in the CPU is the level 1 cache. It is a fixed size memory provided by Intel and it can not be expanded. The size of this memory is 16 KB for the Pentium Pro, 8 KB for data and 8 KB for instruction. The cost per byte of level 1 cache is much lower than the register [1].

#### 5.3.3 Level 2 Cache

Below the level 1 cache in the hierarchy is the level 2 cache. The Pentium Pro has integrated level 2 cache which makes the cache run at the same speed as the processor (usually 180 or 200 MHz) instead of just the system bus speed (60 or 66 MHz). Because of the integrated cache memory it is not possible to expand this memory without replacing the whole CPU. Another drawback of this type of cache memory is that it is very expensive to manufacture the large chip required for the level 2 cache. This is the main reason why Intel did not use integrated level 2 cache when designing the next processor, the Pentium II [1].

#### 5.4 Execution

The Pentium Pro uses the three independent-engine approach which consists of a Fetch/Decode unit, Dispatch/Execute Unit and a Retire Unit.

#### 5.4.1 Instructions

The handling of instructions in Pentium Pro converts the Complex Instruction Set Computer (CISC) x86 instructions into Reduced Instruction Set Computer (RISC) microops. This conversion is to reduce the inherent limitations in the x86 instructions set, such as irregular instruction encoding and register-to-memory arithmetic operations.

It passes the micro-ops to a out-of-order execution engine that determines if the instructions are ready for execution and else if not, the micro-ops are shuffled to prevent pipeline stalls [5].

#### 5.4.2 Pipelining

The Pentium Pro was the first in the x86 family that implements superpipelining. The 14 stages trades less work per pipe stage for more stages. The pipe stage time is 33 percent less then the original Pentium, that results in a higher clock rate on any given process. The 14 stages are dived into three sections, called the three independent-engine approach. Eight stages consist of the in-order front end section, this handles decoding and issuing of instructions. There are three stages which executes the instructions called out-of-order core. The last three stages handles the in-order retirement. Superpipelining provide simultaneous, or parallel, processing within a CPU. It overlaps operations by moving data or instructions into a conceptual pipe with all stages of the pipe processing simultaneously. As an example, while one instruction is being executed, it is decoding the next instruction [2, 5].

#### 5.4.3 Dynamic Execution

Also a performance improvement for the Pentium Pro is the dynamic execution. This includes branch prediction, data flow analysis and speculative execution. These functions reduces the wasted clock cycles, by making predictions about the program flow. Consider memory latency problems when an instruction to memory is called and the CPU must wait for the data to be read from main memory and return it before executing an instruction on the data. This CPU stalls while waiting for this data. To avoid this latency problem, the Pentium Pro processor "looks-ahead" into the instruction pool at subsequent instructions and will do useful work rather than be stalled. This approach has the side effect that instructions are typically executed out-of-order. A call to memory will take many internal clocks, so the Pentium Pro processor core continues to look ahead that could be speculatively executed, and is typically looking 20 to 30 instructions ahead. Dynamic Execution can be summarized as optimally adjusting instruction execution by predicting program flow, having the ability to speculatively execute instructions in any order, and then analyzing the data flow to choose the best order to execute [2, 5].

#### 5.5 Performance

As already mentioned the Pentium Pro processor is designed to deliver optimal performance for 32-bit software. This made it especially suited for software like CAD, 3D, and multimedia applications. The processor became very popular for high performance desktops and workstations, as well as for large database and enterprise applications on servers. The processor delivers outstanding integer and floating-point performance. Many different benchmark tests exists and Table 5.1 on the following page displays the results from a few of them for the original Pentium, Pentium Pro and Pentium 2.

| Processor                   | CPUmark32 | Norton SI32 | iCOMP 2.0 |

|-----------------------------|-----------|-------------|-----------|

| Pentium 200MHz              | 382       | 44          | 142       |

| Pentium Pro 150 MHz         | 420       | 70          | 168       |

| Pentium Pro 166 MHz         | 465       | 78          | 186       |

| Pentium Pro 180 Mhz         | 497       | 81          | 197       |

| Pentium Pro 200 MHz(256 KB) | 553       | 90          | 220       |

| Pentium Pro 200 MHz(512 KB) | 611       | 98          | 240       |

| Pentium II 233 MHz          | 640       | 115         | 267       |

Table 5.1: Benchmarks, higher values is faster

As we can see from Table 5.1 the difference between the original Pentium 200 MHz and the Pentium Pro 200 MHz is bigger than the difference between the Pentium Pro 200 MHz and the later Pentium II 233 MHz. This tells something about how fast the Pentium Pro processor was. The high performance had some back draws, and, as mentioned above, the high prize for the integrated level 2 cache was one of them [3].

#### 5.6 References

- [1] HYDE, R. *The Art of Assembly Language Programming*. No Starch Press, San Francisco, CA, Sept. 2003, ch. 6: Memory Architecture. Also available at http://webster.cs.ucr.edu/AoA/Windows/HTML/MemoryArchitecture.html.

- [2] INTEL CORPORATION. *Pentium Pro Family Developer's Manual*, 1996. Also available at ftp://download.intel.com/design/archives/processors/pro/docs/24269001.pdf.

- [3] INTEL CORPORATION. *Pentium Pro Processor Performance Brief*, June 1997. ftp://download.intel.com/design/archives/processors/pro/docs/-24276806.pdf.

- [4] KOZIEROK, C. M. Intel Pentium Pro ("P6"). Web page, Apr. 17, 2001. http://pcguide.com/ref/cpu/fam/g6PPro-c.html.

- [5] PC TECHNOLOGY GUIDE. Pentium Pro. Web page, Sept.3, 2005. http://www.pctechguide.com/02procs\_Pentium\_Pro.htm.

- [6] WIKIPEDIA. Pentium Pro. Web page, Aug. 16, 2005. http://en.wikipedia.org/wiki/I686.

# 6. Intel Pentium III processor

#### 6.1 Introduction

The Pentium III processor is created by Intel, and was released in the end of February, 1999. It is based on the same architecture as its predecessor Pentium II, which in turn was built on the Pentium Pro core. The instruction set used by Pentium III is the IA-32 (Intel Architecture 32 bits), but with the addition of SSE (Serial SIMD Extension). Another difference between Pentium II and Pentium III is the controversial PSN (Processor Serial Number), a unique ID number hardcoded in each processor. Just like Pentium II, Pentium III also exists in two special versions. The slower and cheaper Celeron, and the faster, but more expensive Xeon. Pentium III has now been superseded by the newer Pentium 4 processor, but it is still used in a lot of places [7, 8].

## 6.2 General Information and History

Pentium III was first introduced in a version called Katmai. It was pretty much the same as Pentium II, but with the addition of the Streaming SIMD Extension (SSE), and an improved level 1 cache controller. It had a speed of 450 and 500 MHz. Later a version called Coppermine was released. It had an improved level 2 cache with lower latency, which made it a lot faster than Katmai. Versions with processor speeds of more than 1 GHz was created. Also the stalls that earlier existed in the instruction pipeline was fixed. Finally Intel released a third version, called Tualatin. It had as much as 512 KB level 2 cache, and existed with processor speeds of 1.4 GHz [8].

One big advantage Pentium III has compared to the older Pentium II processor is the addition of SSE. This is a set of instructions created to extend the MMX instruction set, that was introduced on Pentium II. Both MMX and SSE includes SIMD (Single Instruction, Multiple Data), which allows the processor to apply an instruction to large quantities of data in parallel. This is used to accelerate multimedia applications, since Intel saw a trend in the market requiring just that. Even though MMX was similar to SSE it had the big drawback that it could not handle floating point operations, which SSE could [7, 8, 9].

Another addition to the Pentium III was a Processor Serial Number (PSN), which was a unique ID number hardcoded into each processor. Even though it was possible to disable it, it was shown that web sites could still access the PSN. This caused groups of users, that did not want to be identified that easily, to file complaints against Intel. Eventually Intel had to accept this massive resistance, and declared that no future Intel processors would have the PSN. It is however still included in the Pentium III processors [5].

Intel also released a cheaper version of the Pentium III processor, called Celeron. It was more or less identical to Pentium III, with the significant difference that the level 2 cache was only half as big. This caused Celeron to be slower. On the other hand, a faster and more expensive version called Xeon was released. It had a much larger level 2 cache, up to 2 MB [8].

Since Pentium III processors are not created for some special area or machine, it can be found in regular home computers and laptops. It is also the processor used in Microsoft's gaming console X-box. A special variant of the Tualatin version called Pentium III-S was mostly used in servers where power consumption mattered [8].

#### **6.3** Processor Overview

The first Pentium III processors to be released had frequencies ranging from 450 to 600 MHz. This increased rapidly, and eventually processors with frequencies up to 1.4 GHz existed. The system bus runs at 100 or 133 MHz [8, 4].

The processor has two separate level 1 caches. Both are 16 KB, and one is used for instructions, and the other for data, see Figure 6.1. The level 2 cache is 512 KB on most versions of the Pentium III, but some exist where the cache is only 256 KB, and some where the cache is much larger [3, 4].

There are four different kinds of registers. Eight 32 bit registers for general purpose. Eight 128 bit registers for SSE. Eight 64 bit registers for MMX, and finally eight 80 bit floating points registers [4].

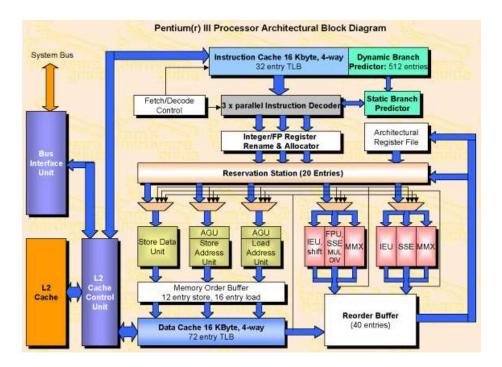

Figure 6.1: The Pentium III architecture (from [6]).

#### **6.4** Architecture and Execution

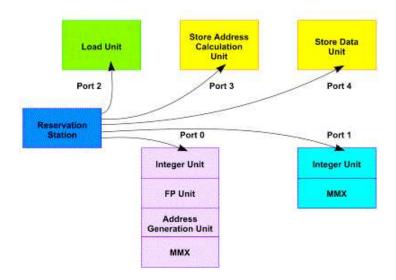

Pentium III uses the Intel P6 core, which features an out-of-order execution unit. A window is opened on all instructions that are not yet executed, which allows the execute phase of the processor to get a better overview of the stream of instructions. This gives it a better ability to schedule the execution of the instructions optimally. The P6 core breaks the x86 instructions into simpler instructions, called micro-ops. This task is performed by three parallel decoders. When the micro-ops are decoded they are sent to the Reservation Stations (RS). There they will wait until their data operands are available, and are then sent to an execution unit. The P6 core has five execution units, designed to execute different sets of instructions. Two handles ALU, MMX and SSE instructions. One handles Load, one Store Address and one Store Data instructions (see Figure 6.2). When a micro-op has been executed it is returned to the Reorder Buffer, where it will wait for retirement. In this stage data is written back to the memory, and the micro-ops will then retire in-order [6].

There are two problems with this approach, that needs to be handled in order to increase the performance of the processor. The first is that the execution units all have a well-defined set of operations to execute. If a large bulk of instructions of the same kind are sent, that execution unit will cause delays, while the other units are idle. To solve this, instructions often needs to be rearranged to create a balanced stream, that make sure that all five execution units has about the same amount of work. The other problem is to decrease the number of dependency bounds on the micro-ops, to make sure that they do not stall, waiting for their data operands to be available [6].

Pentium III has twelve pipeline steps, plus two out-of-order steps. It also supports Branch Prediction, to further increase the performance [4].

Figure 6.2: The five execution units (from [6]).

#### **6.5** Performance

The performance of the Pentium III processor has been measured in two different ways; SpecFP95 and SpecInt95. The test performed by the Standard Performance Evaluation Corporation (SPEC) was made on 500 MHz processors, and gave the result of an average ratio of 20.7 for SpecInt95, and 14.7 for SpecFP95 [2, 1].

#### 6.6 References

- [1] INTEL CORPORATION. SPECfp95: Intel SE440BX2 motherboard (500 MHz, Pentium III processor). Web page, Apr. 21, 2000. http://www.spec.org/cpu95/results/res99q1/cpu95-19990315-03454.html.

- [2] INTEL CORPORATION. SPECint95: Intel SE440BX2 motherboard (500 MHz, Pentium III processor). Web page, Apr. 21, 2000. http://www.spec.org/osg/cpu95/results/res99q1/cpu95-19990315-03453.html.

- [3] INTEL CORPORATION. Hardware Design: Archives Intel Pentium III Processor. Web page, July 6, 2005. http://www.intel.com/design/archives/processors/PentiumIII/index.htm.

- [4] LUDLOFF, C. sandpile.org IA-32 implementation Intel P3 (incl. Celeron and Xeon). Web page, July 12, 2003. http://www.sandpile.org/imp1/p3.htm.

- [5] THE CENTER FOR DEMOCRACY & TECHNOLOGY. A History of Privacy Issues: Intel Pentium III Processor Serial Number. Web page, Sept. 18, 2005. http://www.cdt.org/privacy/issues/pentium3/, date visited given.

- [6] TOMMESANI, S. Intel Pentium III microarchitecture. Web page, 2000. http://www.tommesani.com/IntelPentiumIII.html.

- [7] WALKER, A. Pentium III and a brief history of PC processors. *Cyberwalker.net* (Apr. 15, 1999). Available at http://www.cyberwalker.net/columns/apr99/041599.html.

- [8] WIKIPEDIA. Pentium III. Web page, Sept. 21, 2005. http://en.wikipedia.org/wiki/Pentium\_III.

- [9] WIKIPEDIA. Streaming SIMD Extensions. Web page, Aug. 8, 2005. http://en.wikipedia.org/wiki/Streaming\_SIMD\_Extensions.

# 7. Intel Pentium D with Dual-Core

#### 7.1 Introduction

Codenamed *Smithfield*, the Pentium<sup>®</sup> D was first released on May 26th, 2005, with clockspeeds of 2.8, 3.0, and 3.2 GHz. Its predecessor is Pentium<sup>®</sup> 4 with *Hyper Threading* technology. Other predecessors are the Pentuim<sup>®</sup> family [3].

#### 7.2 Overview

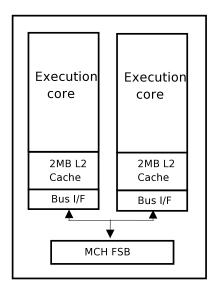

The Pentuim D processor dual-core features two Pentium 4 Prescott processors on the same die. Initially, the Pentium D processor did not support *Hyper Threading* although some Extreme Editions do [1].

Figure 7.1: Pentium D *Dual-core* from [2]

#### 7.2.1 Specification

The main feature of the Pentium D processor is the fact that it has two executing cores. The difference between that and Pentium 4 with *Hyper Threading* is that with the Pentium 4, processing threads are processed in the same core but with more efficiency than the normal Pentium processors (without *Hyper Threading*). With Dual-core technology, each processing thread is processed in a separate core, making it more easy and more effective to run different applications at the same time (see Figure 7.1). More-

over, Pentium D has Intel's EM64T technology which enables the processor to support 64-bit operating systems and applications. In addition to that, it:

- 1. Implements the 64-bit architecture.

- 2. Has 230 million transistors.

- 3. Features Enhanced Intel Speedstep<sup>®</sup>. Processor voltage and frequency adjust based on the needs of the application at hand which can result in less power usage and heat production.

- 4. Has 800 MHz Front Side Bus. High speed between the processor and the other peripherals.

- Features Execute Disable Bit. Can help to prevent some classes of viruses and worms that exploit buffer overrun vulnerabilities. EDB will render the system more secure.

- 6. Features 90 nm Process Technology. Newest generation manufacturing process with technologies to help increase processor performance.

- Has Level 1 cache (two 16 kB Data Caches and two 12 kB Micro-op Execution Trace Caches.

- 8. Has 2×1 MB Level 2 cache. Each processor core has its own 1 MB cache. This results in reducing the amount of Front Side Bus traffic.

The Pentium D is obviously optimal for server applications. But that is not its only major; it can be used with video editing and other demanding applications. Yet today's programs do not fully support this architecture although Windows and other operating systems such as Suse are compatible. Despite that, Pentium D is compatible with both 32-bit and 64-bit systems [1].

## 7.3 Registers

The Intel Pentium D processor supports EM64T<sup>®</sup> technology. EM64T increases the linear address space for software to 64 bits and support physical address space up to 40 bits. The technology also introduces a new operating mode referred to as IA-32e mode. IA-32e mode works in two ways; It either runs a 64-bit system and 32-bit programs or 64-bit operating system with programs that support 64-bits. These are the benefits with 64-bit mode [1]:

- 1. 64-bit flat linear addressing.

- 2. 8 additional general purpose registers(GPR).

- 3. 8 additional registers for streaming.

- 4. 64-bits-wide GPRs and instruction pointers.

- 5. Uniform byte-register addressing.

- 6. Fast interrupt-prioritization mechanism.

### 7.4 Memory Organization

The memory that the processor addresses on its bus is called **physical memory**.

Physical memory is organized as a sequence of 8-bit blocks, each of which is assigned a unique address called **physical address**. Intel EM64T supports physical address space greater than 64 Gbytes. The actual physical address size of IA-32 processors is implementation specific.

When employing the processor's memory management facilities, programs do not directly address physical memory. Instead, they access memory using on of three memory models [1]:

- 1. **Flat memory model** Memory appears to a program as a single, continuous address space which is called a linear address space.

- 2. Segmented memory model— Memory appears to a program as a group id independent address spaces called segments. Code, data, and stacks are typically contained in separate segments. In order for a program to address a byte segment, it issues a logical address that consists of a segment selector and an offset.

- 3. **Read-address mode memory model** This model is for the Intel 8086 processor. It is supported to provide compatibility with existing programs written to be run on the 8086 model.

### 7.4.1 Virtual Memory

With the flat or the segmented memory model, linear address space is mapped into the processor's physical address space either directly or through paging. When using direct mapping (paging disabled), each linear address has a one-to-one correspondence with physical address. Therefore, linear addresses are sent out on the processor without translation. While when using IA-32 architecture's paging mechanism, linear address space is divided into pages which are mapped to virtual memory. These pages are then mapped as needed into physical memory. When an operating system or executive uses paging, the paging mechanism is transparent to an application program. All that the application sees is linear address space [1].

#### 7.5 Execution

The Pentium D processor uses the NetBurst® micro architecture. The Arithmetic Logic Units(ALU) run at twice the processor frequency. Basic integer operation can be dispatched in 1/2 processor clock tick. The processor uses Hyper-Pipelined Technology, which means it has deep pipelines to increase the clock rates, frequency headroom and scalability. The processor also provides an Advanced Dynamic Execution which is a Deep, out-of-order, speculative execution engine. It can manage up to 126 instructions at once, up to 48 loads and more than 24 stores in pipeline. It also has an enhanced branch prediction capability. It reduces the misprediction penalty associated with deeper pipelines and it uses a 4K-entry branch target array and an advanced branch prediction algorithm. The Processor has a new cache subsystem. The first level caches has an advanced execution trace cache that stores decoded instructions. The advanced

execution cache trace removes decoder latency from main execution loops and integrates path of program execution flow into a single line. The L1 cache is a low latency data cache. The L2 cache is a full-speed, unified 8-way level 2 on-die advance transfer cache and its bandwidth and performance increases with the processor family [1].

### 7.6 Performance

In Table 7.1 are some values that Pentium D processors presented.

Table 7.1: Three Pentium D processors are tested. Test is taken from [2]

| Processor               | MIPS  | MFLOPS               |

|-------------------------|-------|----------------------|

| Pentium D 840           | 17407 | 4621 FPU / 7950 SSE2 |

| Pentium D 840(4.02 GHz) | 18113 | 5737 FPU / 8711 SSE2 |

| Pentium D 840 64-bit    | 18191 | 4970 FPU / 8770 SSE2 |

### 7.7 Conclusion

The Pentium D processor with dual-core is a good step towards faster systems. That is why it is important for the next generation operating systems to make use of this technology so that its power can be properly used.

### 7.8 References

- [1] INTEL CORPORATION. *IA-32 Intel Architecture Software Developer's Manuals, Volume 1: Basic Architecture*, Sept. 2005. Available for download at ftp://download.intel.com/design/Pentium4/manuals/25366517.pdf.

- [2] MIKE D. Intel Pentium D 840 dual-core LGA775 processor review. *pcstats.com* (Aug. 2005). Available at http://www.pcstats.com/artvnl.cfm?articleID=1838.

- [3] WIKIPEDIA. Pentium D. Web page, Sept. 20, 2005. Available at http://en.wikipedia.org/wiki/Pentium\_D.

Andreas Mattsson 33

# 8. Intel Itanium (IA-64 Merced)

### 8.1 Introduction

Itanium, also called Merced, is the first generation of processors built on the IA-64 architecture. It is the result of a cooperation between Intel and Hewlett-Packard whose goal was to create a 64-bit post-RISC architecture for heavy server applications. It was therefore intended to replace the Xeon series as Intel's foremost server CPU [7].

When the processor was released in June 2001 its performance didn't live up to expectations and had difficulties getting into the market [7].

### 8.2 Overview

When it was shipped in June 2001 it was available at the speeds 733 and 800 MHz manufactured with a 180 nm process. The system bus used was running at a mere 266 MHz which would prove to be one of Itanium's weak points. That is 33 % slower than the bus used by the Intel Pentium 4 sold at the same time. The CPU consists of approximately 25M transistors excluding the L3 cache which is off-die [7, 5].

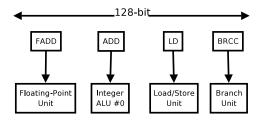

At its core the Itanium is basically a RISC design but with multiple functional units enabling it to execute 6 instructions in each cycle (6-wide super scalar). What makes this architecture stand out from the ordinary RISC design is the way instructions are fed and decoded by the CPU [2].

#### 8.2.1 Instruction Set

The instruction format for sending instructions to the CPU is called very long instruction word (VLIW). Each of these words is 16 bytes long and is called a bundle. A bundle is organized in three 41-bit instruction slots and a template field. Each instruction can take one or two slots depending on the size needed. The template field contains information about the instructions in the bundle and it tells if the bundle can be executed in parallel with the next bundle [4].

With this design the CPU can be expanded in later versions to handle more parallel instruction without changing the instruction set. In addition to the basic instructions the IA-64 architecture also contains instructions for multimedia and floating point operations. It is also possible to add more instructions by programming using an extensible firmware interface (EFI) program [6].

### 8.2.2 Registers

Itanium has a generous amount of registers, 256 of them, 128 each of 64 bits integer (r0 through r127) and 82 bits floating point registers (f0 through f127). Register r0 and register f0 is always set to 0 removing the need for the constant 0. The register f1 always hold the value 1. The CPU also has a feature called register rotation which is

used to rename registers in hardware to make as efficient use of registers as possible, thus improve performance [6].

### 8.3 Memory

#### **8.3.1** Caches

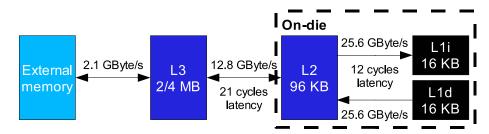

The cache memory of the Itanium consists of 2 or 4 MB off-die L3 cache, 96 KB L2 cache and 32 KB L1. The L1 cache is divided in half between instructions and data. As can be seen in Figure 8.1 the latency of the L3 cache is quite high which is one of the main bottlenecks of the CPU. The other latencies in the memory hierarchy is also quite high and the bandwidth of the memory bus is a bit poor. All these things were vastly improved in the next generation of the CPU [3, 7].

Figure 8.1: An illustration of the memory organization of the Itanium.

### 8.3.2 Virtual Memory

Itanium supports the following page sizes: 4 KB, 8 KB, 16 KB, 64 KB, 256 KB, 1 MB, 4 MB, 16 MB and 256 MB. It implements 54 virtual address bits and 44 physical address bits [5].

### 8.4 Execution

#### 8.4.1 Pipeline

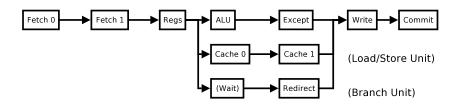

The pipeline of the Itanium is a highly parallel 10-stage pipeline. It is able to execute up to 6 instructions in every clock cycle. Figure 8.2 on the facing page shows the different stages in the pipeline and Table 8.1 on the next page contains brief explanations of each stage [2, 1].

The pipeline is divided into two groups of units, the front-end and the back-end. The front-end consists of the IGP, FET and ROT units which is responsible for fetching instruction bundles and doing branch prediction. It also does pre-fetching which hides fetch latency. The back-end consists of the other units and is responsible for the execution of the instructions. The communication of bundles is done via a decoupling

Andreas Mattsson 35

buffer with room for 8 bundles. This decoupling of the front-end and the back-end makes it possible for the front-end to keep running, fetching and pre-fetching if the back-end would stall [2, 1].

Figure 8.2: The 10 stages of the Itanium pipeline

Table 8.1: Explanations of the stages in the Itanium pipeline.

| State | Explanation                                                              |

|-------|--------------------------------------------------------------------------|

| IPG   | Instruction Pointer Generation. An address for the instruction pointer   |

|       | is generated.                                                            |

| FET   | Fetches bundles and passes them on to the next step.                     |

| ROT   | Determines which order bundles will be placed in the buffer which passes |

|       | them on to the back-end of the pipeline.                                 |

| EXP   | Disperses the instructions in the bundles to 9 issue ports.              |

| REN   | Register renamer.                                                        |

| WLD   | Word-line decode.                                                        |

| REG   | Read operands from the register file.                                    |

| EXE   | Instruction execution.                                                   |

| DET   | Exception detection.                                                     |

| WRB   | Write back.                                                              |

#### 8.4.2 Out-of-Order Execution

To create an efficient super scalar architecture it is necessary to implement an out-oforder decoder system which analyses the dependency between instructions to see what instructions can be executed i parallel. This is also the case in the Itanium, however instead of using some complex logic to accomplish this Itanium relies on the compiler to perform this task. The compiler is responsible for organizing the instructions so they can be executed in parallel to the greatest extent possible. This method is called explicitly parallel instruction computing (EPIC) [1, 6].

#### **8.4.3** Branch Prediction

In the Itanium design the complexity of branch prediction has been moved from the CPU to the compiler (EPIC). The CPU relies on the compiler to put information about this into the code being executed. The benefit of this is that since the compiler has a lot more time to decide on a branch and also access to the complete code it can often make better decisions. It also speeds up the execution of the code since the same decision doesn't have to be done every time the code is being executed. However the

runtime behavior of a program is not always obvious in the code that generates it. This sometimes makes it impossible for the compiler to correctly predict what probably could be predicted at runtime by some logic on the CPU itself [1, 6].

Using the information handed from the compiler the pre-fetch engine of the Itanium can see to that the instructions needed can be fetched from the L1 cache [1, 6].

### 8.5 Performance

The Itanium running at 800 MHz scores about 50 points in Spec95int and about 90 points in Spec95fp. That was, at the time of launch, not enough to persuade most of the customers. The reasons for this failure are many, a few has already been mentioned earlier in Section 8.3.1 on page 34. The main reason is probably the lengthy delays which dogged the development an resulted in the processor being old before if even reached the market [6, 7].

### 8.6 References

- [1] HODGIN, R. C. Intel's Itanium. *geek.com* (June 8, 2001). Available at http://www.geek.com/procspec/features/itanium/ (visited Sept. 22 2005).

- [2] INTEL CORPORATION. *Intel Itanium Processor Microarchitecture Overview*, Oct. 1999. Also available at http://www.dig64.org/More\_on\_DIG64/-microarch\_ovw.pdf.

- [3] INTEL CORPORATION. *Intel Itanium processor reference manual for software optimization*, Nov. 2001. Also available at http://www.intel.com/design/itanium/downloads/24547403.pdf.

- [4] INTEL CORPORATION. *Intel Itanium processor-specific application binary interface*, May 2001. Also available at http://www.intel.com/design/itanium/downloads/24537003.pdf.

- [5] INTEL CORPORATION. *Intel Itanium product brief*, 2001. Also available at http://www.intel.com/design/itanium/itanium/ItaniumProdBrief.pdf.

- [6] WIKIPEDIA. IA-64, Sept. 1, 2005. http://en.wikipedia.org/wiki/IA-64 (visited Sept. 22 2005).

- [7] WIKIPEDIA. Itanium, Sept. 22, 2005. http://en.wikipedia.org/wiki/Itanium (visited Sept. 22 2005).

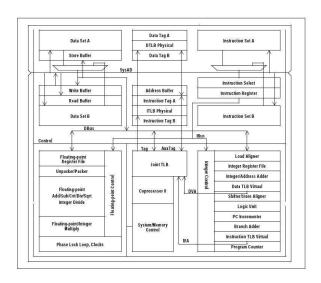

ANTON HAGLUND 37

# 9. IBM PowerPC G5

### 9.1 Introduction

PowerPC 970FX, also known as PowerPC G5, is a 64-bit processor from IBM used in Apple computers. This is a paper with some relevant information about G5. Apple introduced the G5 in June 2003, and made it one of the first 64-bit processors for the personal computer market [2]. G5 is based on the core from IBM's POWER4 that uses the same vector engine, VMX, as in G5's predecessor G4 [4].

PowerPC 970 is also called G5. The difference between 970 and 970FX is that 970 is built using a 130  $\mu$ m fabrication process and 970FX a 90  $\mu$ m [4]. In Apples white pages they are referring to the 970FX as G5 [2].

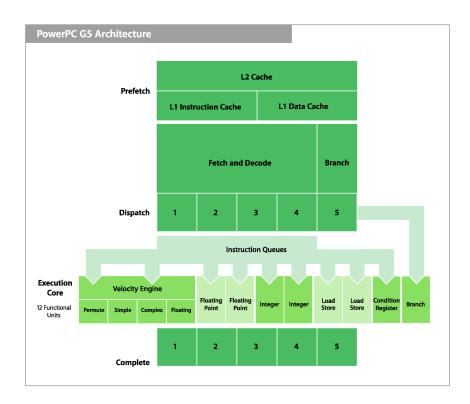

Figure 9.1: PowerPC G5 (from [4])

### 9.2 Overview of the Processor

G5 uses the Double Data Rate frontside bus for faster communication between memory controller and processor. Instead of transporting data in one direction at the time, G5 uses a dual-channel frontside bus that has 32 bits in each direction [2]. For a 2.7 GHz G5, the frontside bus operates at 1.35 GHz and get a theoretical bandwidth of 10.8 GB per processorsecond.

In Figure 9.2 on the next page you can see an abstract view over G5's architecture [2].

Figure 9.2: G5 Architecture (from [2])

### 9.2.1 Implementations

The G5 is used on the desktop PC Power Mac G5, the server Xserve G5 and the laptop iMac G5 [1].

## 9.3 Memory

Because memory addresses are computed in 64-bit registers capable of expressing integers up to 16 exabytes, G5 can theoretically address  $2^{64}$  bytes of virtual memory  $^{1}$  [2]. In practice, the physical memory is 42 bits or  $2^{42}$  bytes, which is 4 terabytes.

In fetch and decode, the second level cache is 512 kB at a rate up to 64 GB per second. The L1 instruction cache is at 64 kB, direct-mapped from the L2 cache [2].

For virtual memory handling, the storage description register (SDR1) specifies the page table base address used in virtual-to-physical address translation [3].

$<sup>^{1}</sup>$ 16 exabytes =  $2^{64}$

Anton Haglund 39

### 9.4 Execution

The execution core consists of 12 functional units and are explained in Table 9.1.

Table 9.1: Execution core

128-bit velocity engine A vector processing unit that support parallel internal op-

erations. It simultaneously process 128 bits of data in four 32-bit integers, eight 16-bit, sixteen 8-bit or four 32-

bit single-precision floating-point values [2].

Floating-point units G5 completes at least two 64-bit calculations per clock

cycle. Each of its two floating-point units can perform both an add and a multiply with a single instruction, as

well as square root calculations [2].

Integer units Two integer units that perform both 32- and 64-bit integer

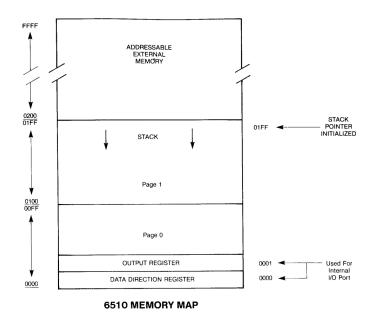

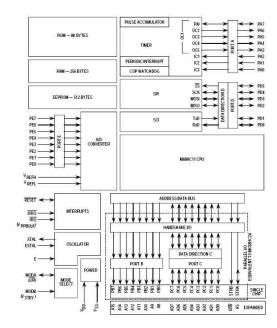

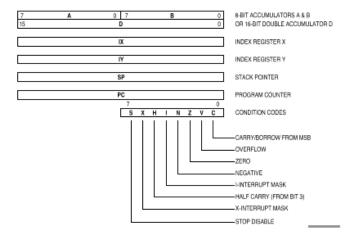

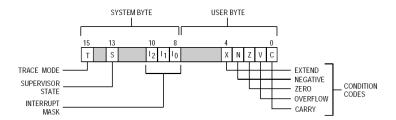

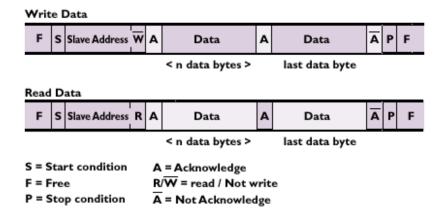

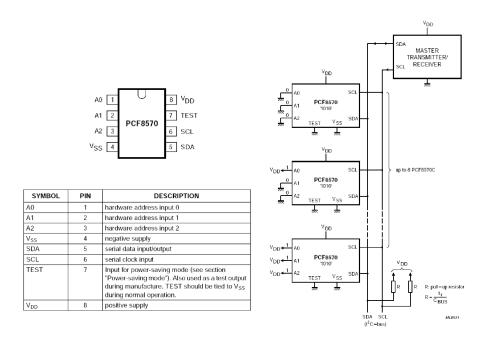

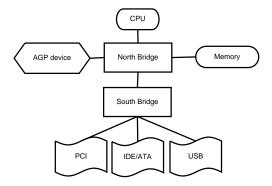

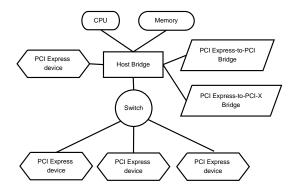

instructions.