© Copyright 2001-2009 Alpha Data

# The family\_t datatype

The family\_t datatype is used to symbolically represent a particular Xilinx FPGA family and is defined as follows:

```

type family_t is (

family_virtex, -- Virtex/Virtex-E/Virtex-EM

family_virtex2, -- Virtex-II

family_virtex2p, -- Virtex-II Pro

family_virtex4, -- Virtex-4

family_virtex5); -- Virtex-5

```

#### © Copyright 2001-2009 Alpha Data

## The ddr2sram\_port component

**Overview**

**HDL** source code

**Parameters**

**Signals**

**Performance**

#### Overview

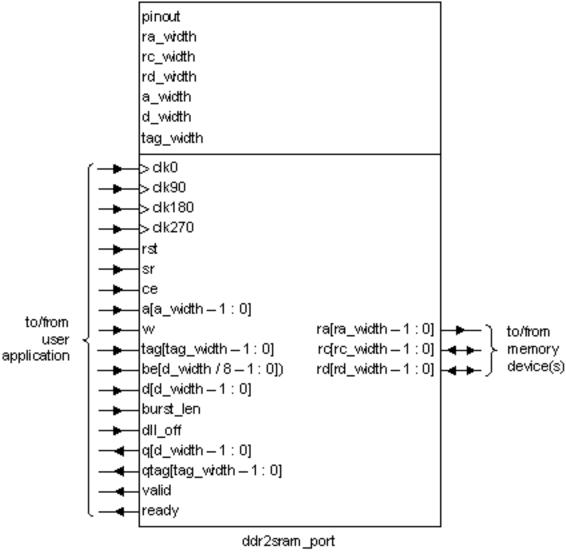

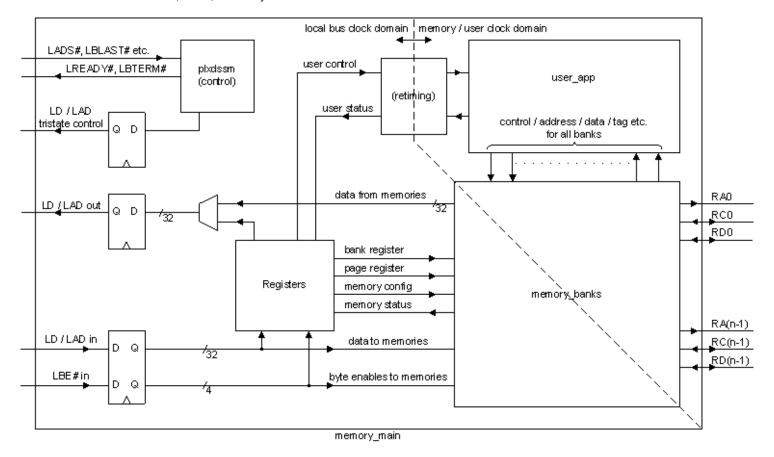

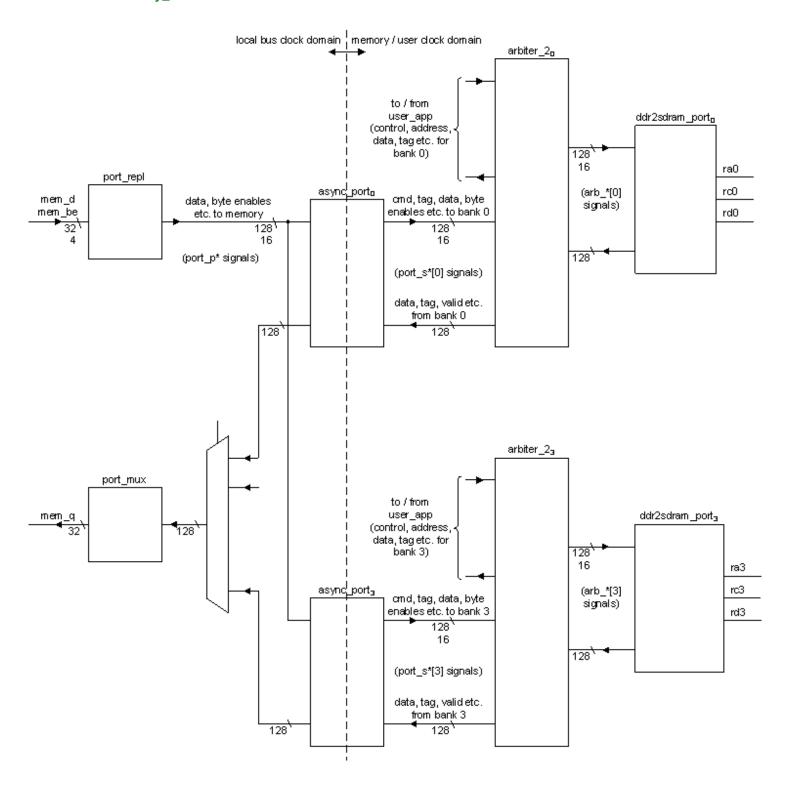

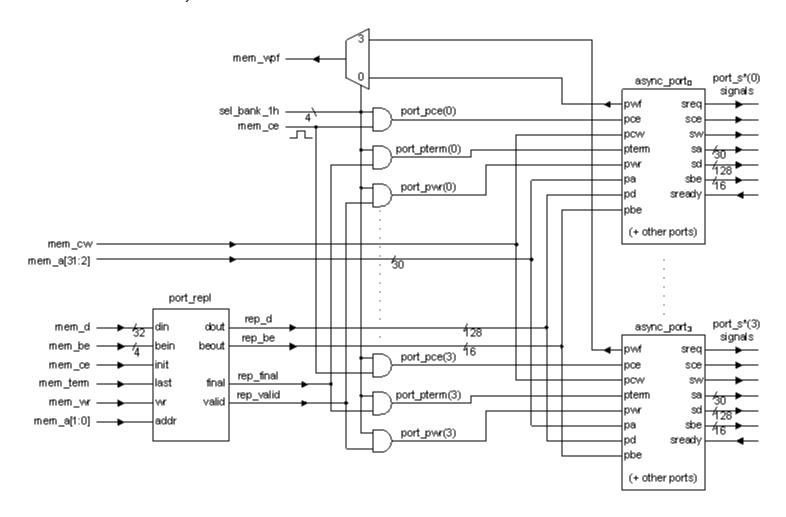

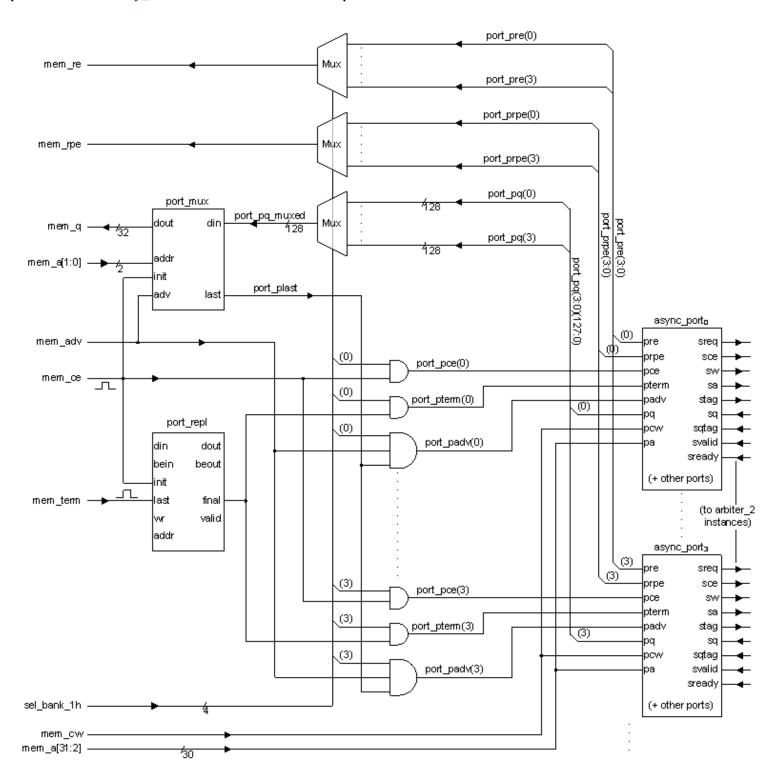

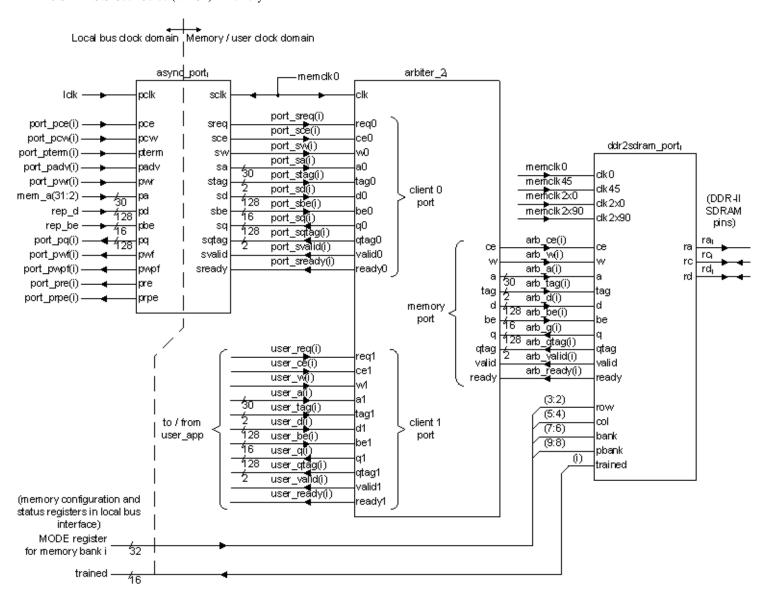

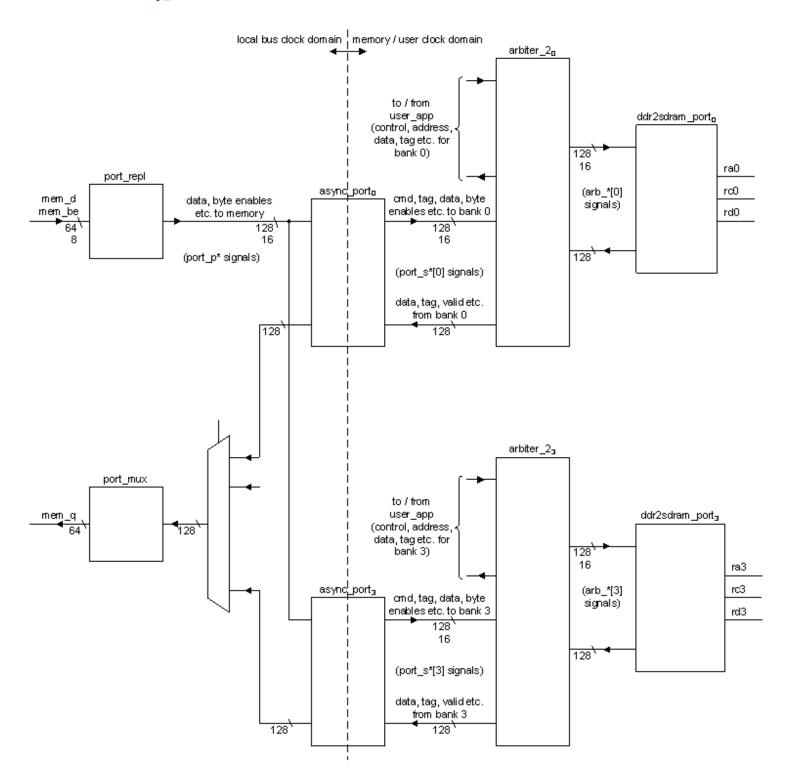

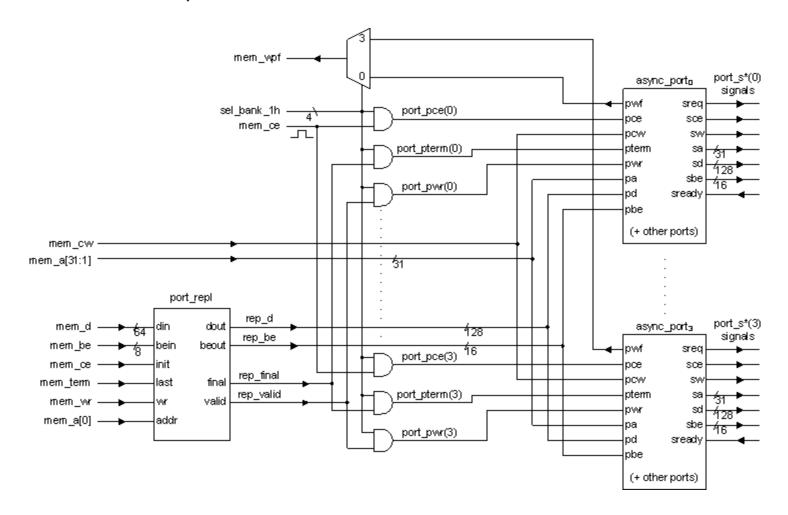

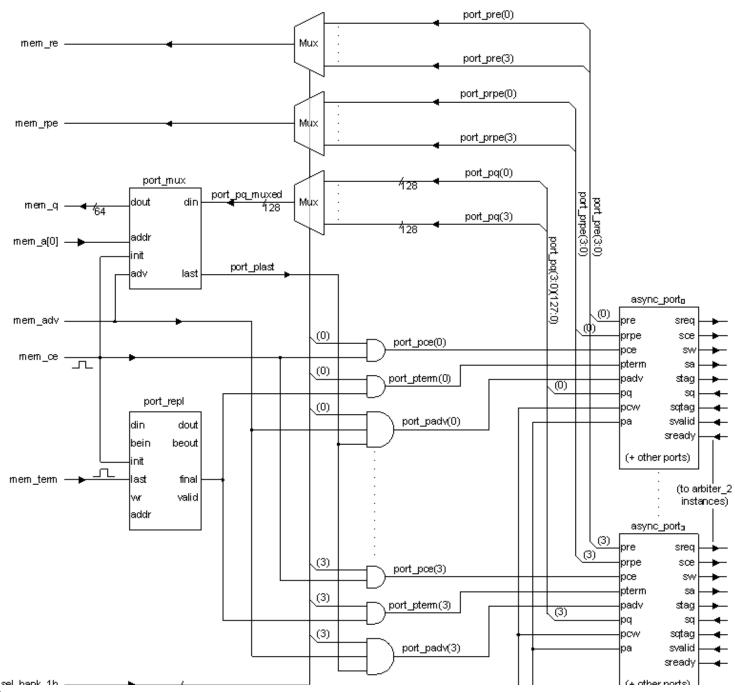

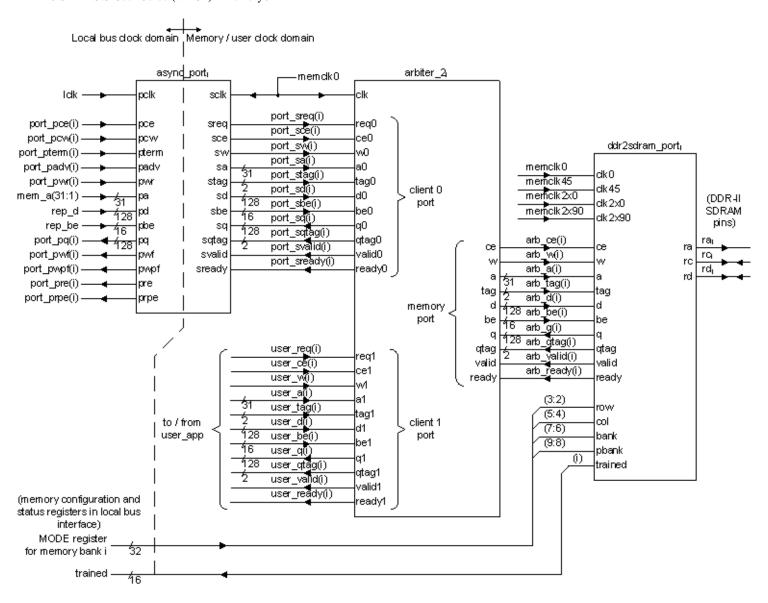

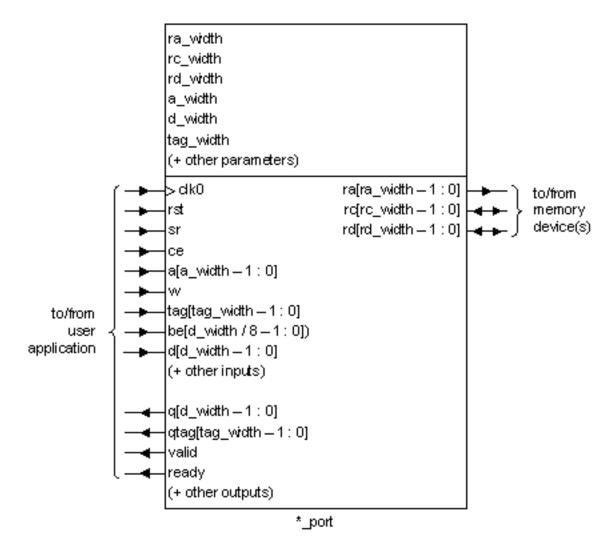

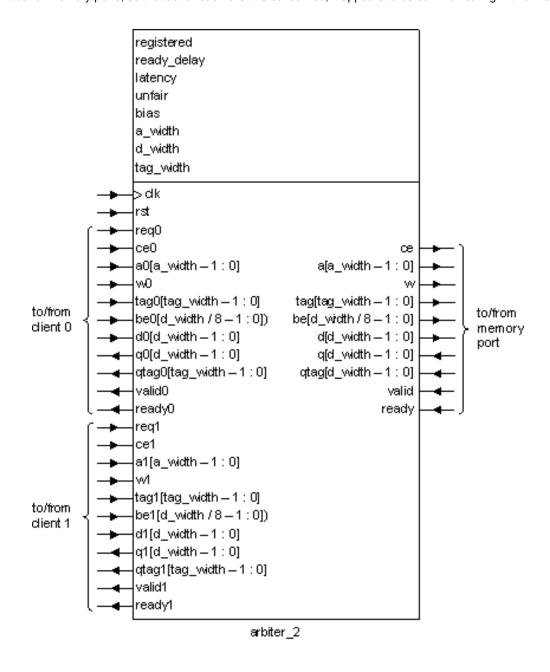

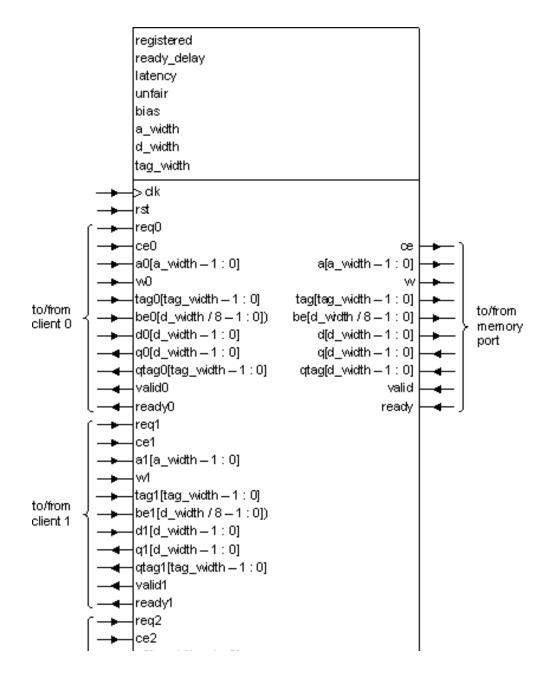

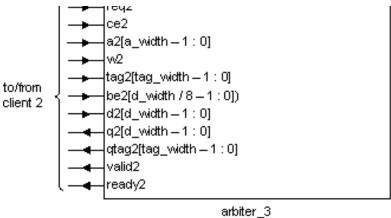

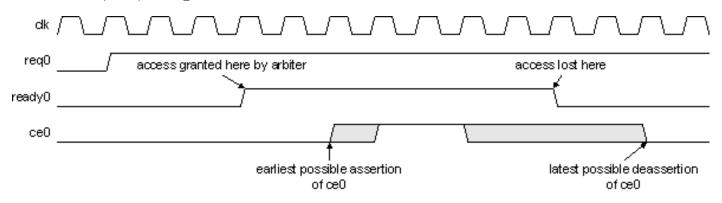

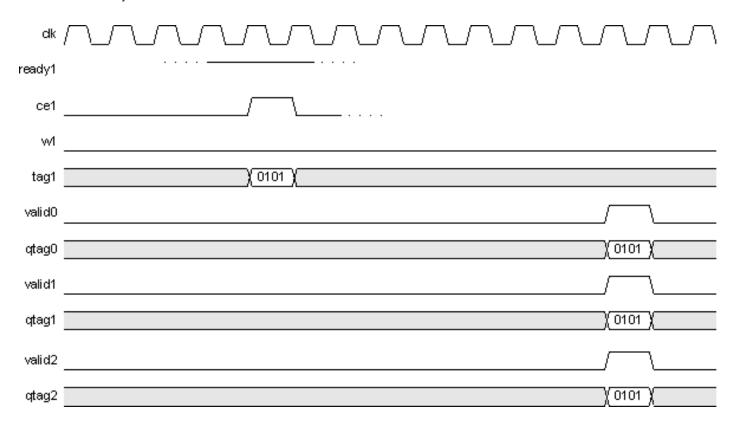

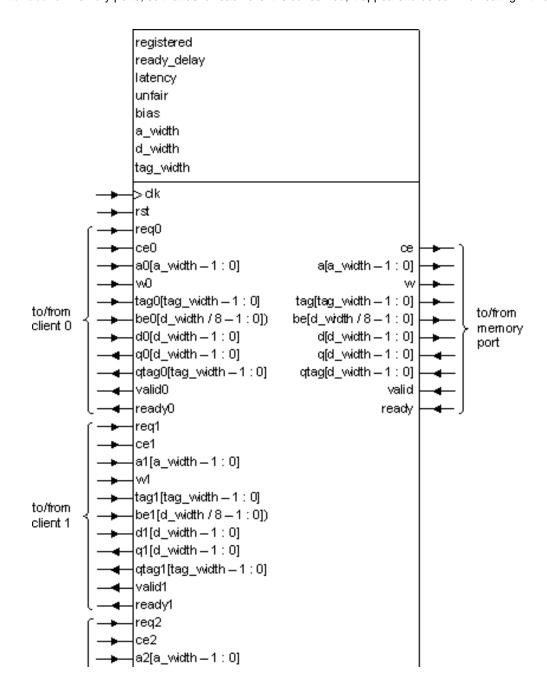

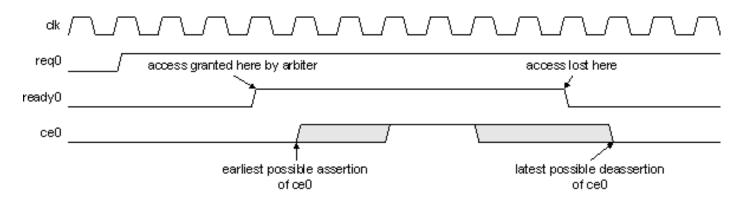

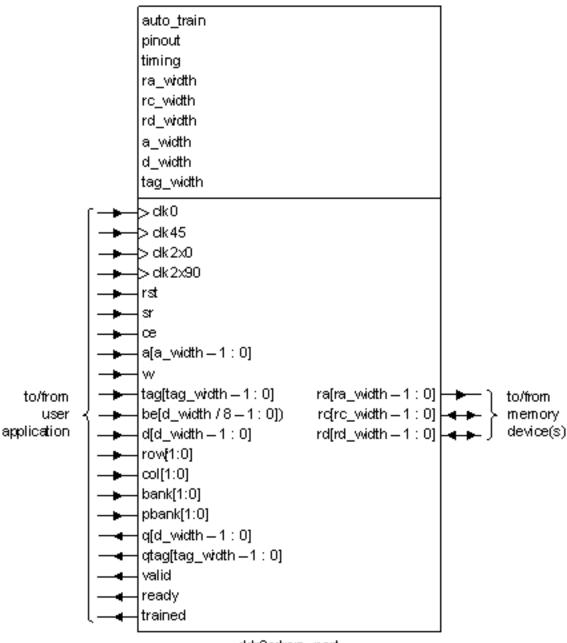

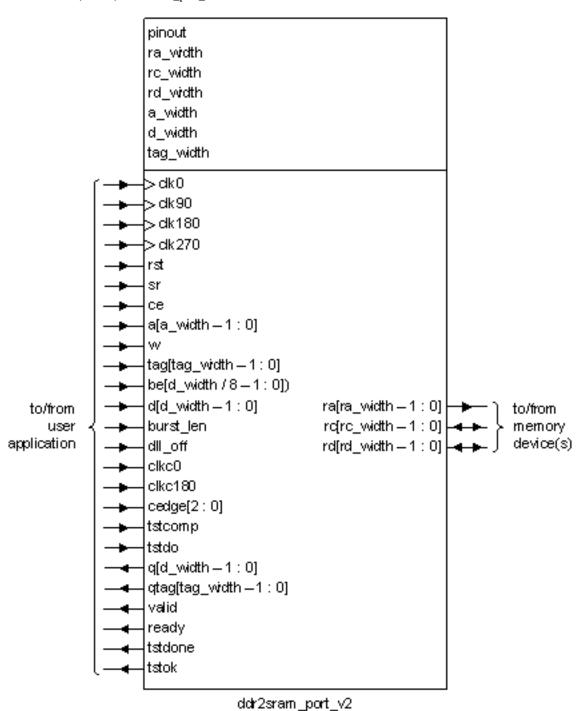

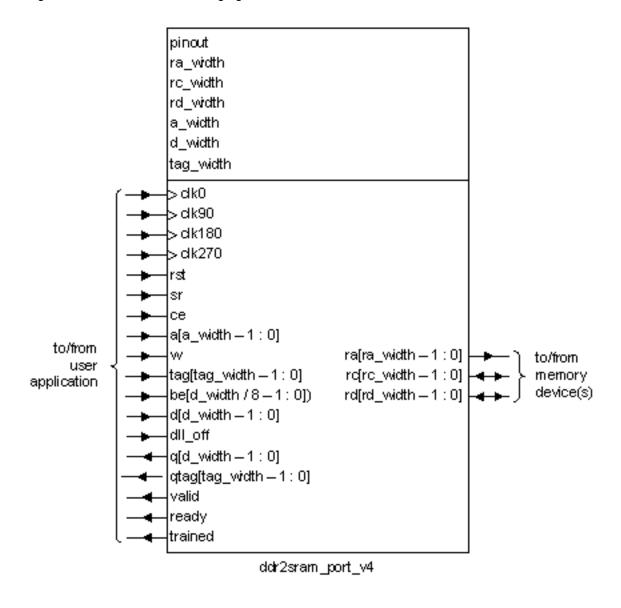

The ddr2sram\_port component is part of the memif package and implements an interface to a bank of DDR-II SSRAM memory. This component follows the generic user interface for memory ports, but also has a few additional parameters and sideband signals, as shown in the following figure:

#### **HDL** source code

Projects making use of this component must include all of the following source files (relative to root of SDK installation):

fpga/vhdl/chipscope/src/ilap\_pkg.vhd

fpga/vhdl/chipscope/src/ilacombo\_sim.vhd

fpga/vhdl/common/memif/memif\_pkg.vhd

fpga/vhdl/common/memif/memif\_int\_pkg.vhd

fpga/vhdl/common/memif/memif\_def\_synth.vhd OR fpga/vhdl/common/memif/memif\_def\_sim.vhd

fpga/vhdl/common/memif/cmd\_fifo.vhd

fpga/vhdl/common/memif/ddr2sram/ddr2sram\_port.vhd

If synthesizing, the file **fpga/vhdl/common/memif/memif\_def\_synth.vhd** must be included. If simulating, the file **fpga/vhdl/common/memif/memif\_def\_sim.vhd** must be included instead.

#### **Parameters**

| Name      | Туре              | Function                                                                                                                                                   | Note |

|-----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| a_width   | natural           | Width in bits of the port logical address, a.                                                                                                              | 4    |

| d_width   | natural           | Width in bits of the port data in and out, <b>d</b> and <b>q</b> respectively.                                                                             | 3    |

| pinout    | ddr2sram_pinout_t | This value specifies the physical configuration of the memory port. For convenience, an application may map it to one of the <b>predefined constants</b> . |      |

| ra_width  | natural           | Width in bits of the memory device address bus, ra.                                                                                                        | 1    |

| rc_width  | natural           | Width in bits of the memory device control bus, rc.                                                                                                        | 2    |

| rd_width  | natural           | Width in bits of the memory device data bus, rd.                                                                                                           | 3    |

| tag_width | natural           | Width in bits of the tag in and out, tag and qtag respectively.                                                                                            |      |

#### Notes:

- 1. The **ra\_width** parameter is a property of the printed circuit board, indicating how many wires are physically present, rather than indicating how many of the **ra** lines are used by a particular DDR-II SSRAM device.

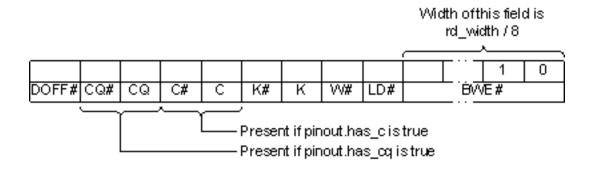

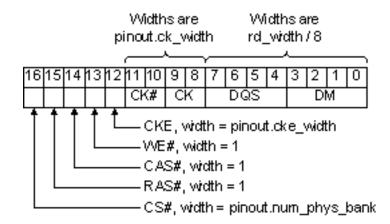

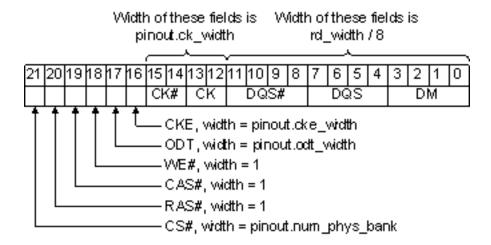

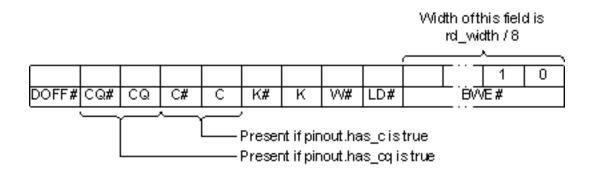

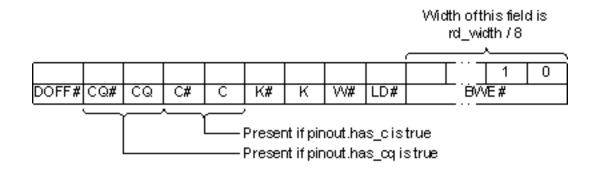

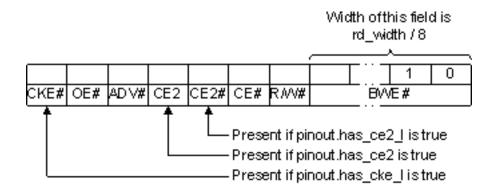

- 2. The memory device control bus, **rc**, is composed of various fields in this memory port, with the widths of certain fields specified by the **pinout** and **rd\_width** parameters. The following figure illustrates the fields that comprise the **rc** bus:

The order of the fields within rc is always the same, but some models may lack certain fields.

- 3. The rd\_width parameter is the number of physical DQ wires making up the data bus of the DDR-II SSRAM bank. This memory port transfers two words of data on the DQ wires for each command entered via the ce signal. Accordingly, the d\_width parameter, which is the width of d and q, is typically specified by the user application as being two times rd\_width. However, other values can be passed for d\_width:

- If d\_width > (2 \* rd\_width), then the memory port simply truncates d internally so that its width is (2 \* rd\_width). Data read from the memory devices is zero-extended so that its width is d\_width before being returned on q.

- d\_width = (2 \* rd\_width) is the optimal usage case.

- If d\_width < (2 \* rd\_width), then the memory port zero-extends d internally so that its width is (2 \* rd\_width).</li>

- 4. The a\_width parameter is the width of the logical address bus, a. Generally, it must be sufficiently wide to be able to address all of the memory in a DDR-II SSRAM bank. Hence, the required value of a\_width depends on what memory devices are actually in use. As an example, consider a DDR-II SSRAM device with 20 address bits. Since "logical" memory locations are two times as wide as the physical memory locations, one must subtract 1, giving a value of 19 for the minimum value of a\_width. When a\_width is larger than actually required, the top few unused bits of a are ignored by the memory port. In practice, one should determine the value of a\_width assuming that the largest possible memory devices are in use.

#### **Signals**

The signals of this interface to and from the user application are as follows:

| Signal    | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Note |

|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| a         | in   | Logical address  User code must place a valid address on <b>a</b> when it asserts <b>ce</b> .  Since a memory port effectively represents a memory device as a linear array of words of width <b>d_width</b> , this address is a logical address, rather than anything resembling what one might see on the <b>ra</b> bus.                                                                                                                                                                                                                                                       |      |

| be        | in   | Byte enables to memory  User code must place valid byte enables on <b>be</b> whenever a write command is entered ( <b>ce</b> and <b>w</b> both asserted). A logic 1 in a given bit of <b>be</b> means that the corresponding byte within <b>be</b> will be written to memory, while a zero means that the corresponding byte will not be written to memory.                                                                                                                                                                                                                      |      |

| burst_len | in   | Burst length select (sideband signal)  This input selects whether the DDR-II SSRAM devices are burst length 2 (BL2) or burst length 4 (BL4) devices:  0 => BL2  1 => BL2/BL4  If BL2/BL4 is selected, the memory port will be compatible with BL2 and BL4 devices, although a performance penalty may apply depending on how the user application uses the memiry port. If BL2 is selected, the memory will not be compatible with BL4 devices. If the burst length is unknown at build time, one should select BL4. Refer to the section below for a discussion of performance. | 6    |

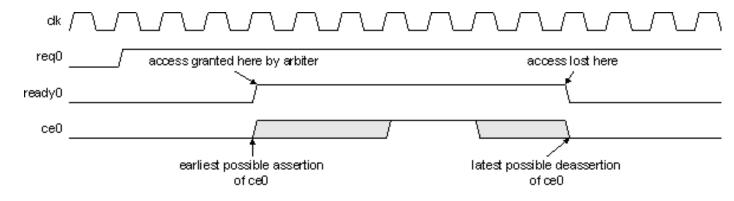

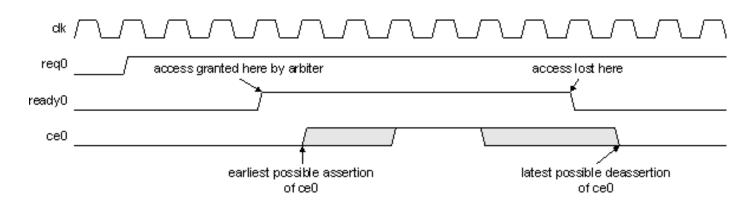

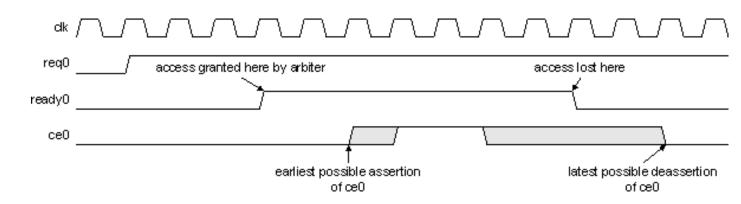

| ce      | in  | Command entry                                                                                                                                                                                                                                                        |   |

|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|         |     | User code asserts this signal to enter a new read or write command into the memory port. When asserted, <b>a</b> and <b>w</b> must be valid. When asserted along with <b>w</b> , <b>tag</b> must also be valid.                                                      |   |

|         |     | User code must not assert ce when ready is deasserted.                                                                                                                                                                                                               |   |

|         |     | Other than that, there are no restrictions on how few or how many clock cycles <b>ce</b> can remain asserted. It can be pulsed for single <b>clk0</b> cycles, or asserted for many <b>clk0</b> cycles ( <b>ready</b> permitting).                                    |   |

|         |     | The address, byte enables, tag etc. of a command need not bear any relationship to that of the previous command, but refer to the section below for a <b>discussion of performance</b> .                                                                             |   |

| clk0    | in  | Clock for user interface                                                                                                                                                                                                                                             | 5 |

|         |     | All other signals except <b>rst</b> are synchronous to <b>clk0</b> .                                                                                                                                                                                                 |   |

| clk90   | in  | High speed clock, phase 90                                                                                                                                                                                                                                           | 5 |

|         |     | This clock must be the same frequency as <b>clk0</b> but 90 degrees behind.                                                                                                                                                                                          |   |

| clk180  | in  | High speed clock, phase 180                                                                                                                                                                                                                                          | 5 |

|         |     | This clock must be the same frequency as <b>clk0</b> but 180 degrees behind.                                                                                                                                                                                         |   |

| clk270  | in  | High speed clock, phase 270                                                                                                                                                                                                                                          | 5 |

|         |     | This clock must be the same frequency as <b>clk0</b> but 270 degrees behind.                                                                                                                                                                                         |   |

| d       | in  | Data to memory                                                                                                                                                                                                                                                       |   |

|         |     | User code must place valid data on <b>d</b> whenever a write command is entered ( <b>ce</b> and <b>w</b> both asserted).                                                                                                                                             |   |

| dll_off | in  | DLL disable (sideband signal)                                                                                                                                                                                                                                        | 6 |

|         |     | User code should drive this input with 0 for normal operation, but driving it with 1 causes the DOFF# field within rc to be asserted.                                                                                                                                |   |

| q       | out | Data from memory                                                                                                                                                                                                                                                     |   |

|         |     | When <b>valid</b> is asserted by the memory port (as a result of a read command), <b>q</b> reflects the data read from memory.                                                                                                                                       |   |

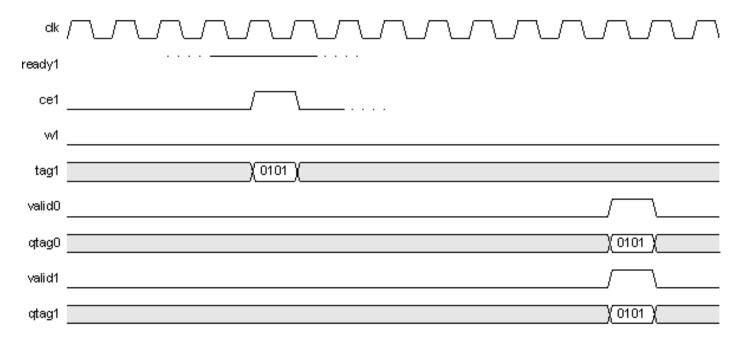

| qtag    | out | Tag out                                                                                                                                                                                                                                                              |   |

|         |     | When <b>valid</b> is asserted by the memory port (as a result of a read command), <b>qtag</b> reflects the tag value that was assocated with that read command.                                                                                                      |   |

| ready   | out | Port ready                                                                                                                                                                                                                                                           |   |

|         |     | When the memory port asserts <b>ready</b> , user code is permitted to assert <b>ce</b> . Certain types of memory port may unconditionally assert <b>ready</b> , whereas other types of memory port may sometimes deassert <b>ready</b> depending on several factors. |   |

|         |     | For example, a DDR-II SDRAM port is capable of buffering a certain number of commands internally, but if its command buffer is filled while it executes a refresh cycle, it will deassert <b>ready</b> .                                                             |   |

|         |     |                                                                                                                                                                                                                                                                      |   |

| rst   | in  | Asynchronous reset for memory port                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       |     | May be tied to logic 0 if not required.                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| sr    | in  | Synchronous reset for memory port  May be tied to logic 0 if not required.                                                                                                                                                                                                                                                                                                                                                                    |  |

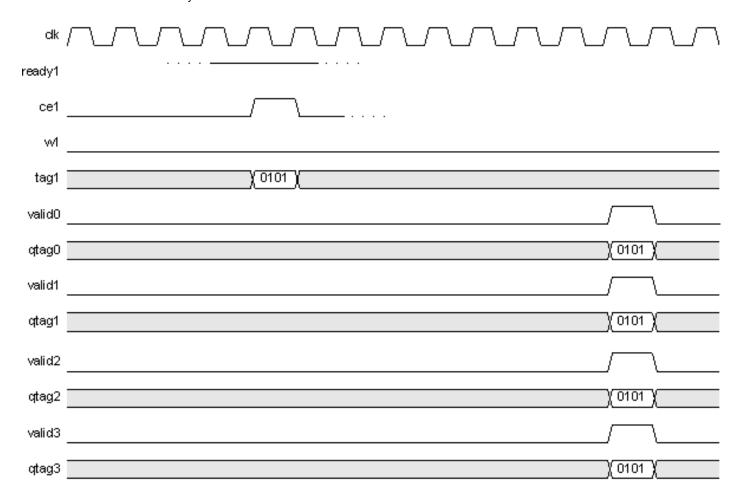

| tag   | in  | Tag in  When user code asserts <b>ce</b> with <b>w</b> deasserted, it must also place a valid tag on the <b>tag</b> signal. When, as a result of the read command, the memory port asserts <b>valid</b> , the <b>qtag</b> output reflects the tag value originally passed. This is intended to facilitate sharing of a memory port between several data sources or data sinks, where each source or sink recognizes a particular set of tags. |  |

| valid | out | Read data valid  When the memory port asserts <b>valid</b> , it does so as a result of a read command (user code asserted <b>ce</b> with <b>w</b> deasserted). When <b>valid</b> is asserted, both <b>q</b> and <b>qtag</b> are valid.                                                                                                                                                                                                        |  |

| W     | in  | Write select  When user code asserts <b>ce</b> , it must place either a logic 1 on the <b>w</b> signal in order to select a write command, or 0 in order to select a read command.                                                                                                                                                                                                                                                            |  |

#### Notes:

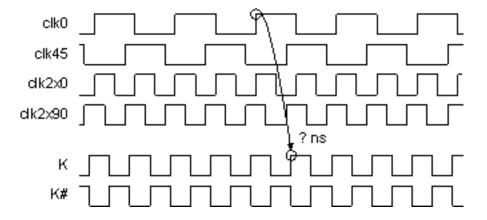

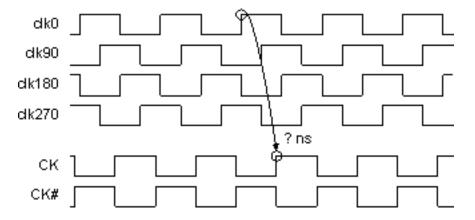

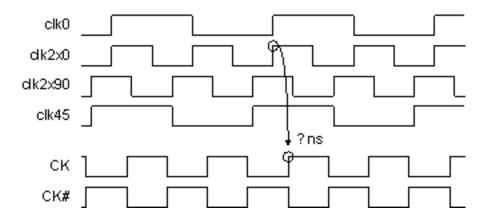

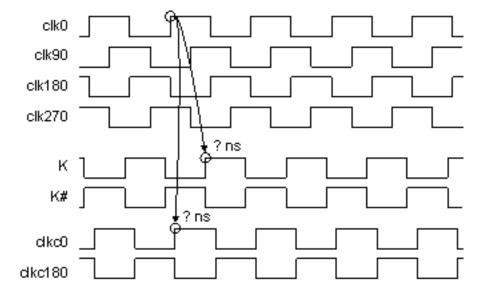

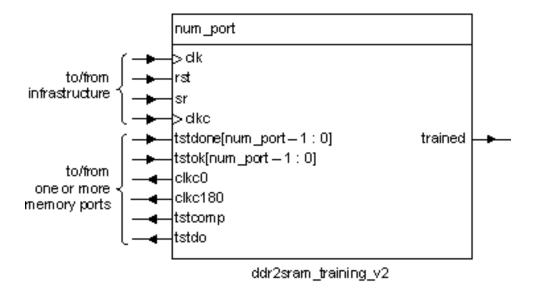

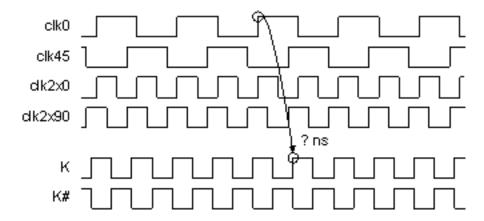

5. The phase and frequency relationships between the four clock phases are illustrated by the following figure:

Also shown is the DDR-II SSRAM clock, K. Its frequency is the same as **clk0**, but its phase is indeterminate.

6. For correction operation, all sideband inputs must be static while the memory port is not idle.

The signals of this interface to and from the memory device(s) are as follows:

| Signal | Туре | Function                                                                              |

|--------|------|---------------------------------------------------------------------------------------|

| ra     | in   | Memory device address bus                                                             |

|        |      | This bus carries address information to from the memory port to the memory device(s). |

| rc | inout | Memory device control bus  This bus carries control signals between the memory port and the memory device(s), and is composed of various fields.  These signals are bundled together into the rc bus so that, for the most part, the user application need not care what they are.  Refer to note 2 for the mapping of the rc bus to device pins. |

|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rd | inout | Memory device data bus  This bus carries data between the memory port and the memory device(s). For each command entered via ce, two words are transferred on rd, which determines the relationship between the rd_width and d_with parameters. Refer to note 3 for details.                                                                      |

#### **Performance**

This memory port features an internal command buffer capable of buffering about 10 commands before deasserting the **ready** signal. Most of the time, the rate of consumption of commands from the command buffer is at least as fast as production of new commands by the user application. Certain usage patterns, however, may result in a accumulated backlog in the command buffer.

A DDR-II SSRAM device has a burst length of two or four (i.e. two or four words on transferred on the **rd** bus). This component supports burst length four (BL4) devices, but is compatible with burst length 2 devices without modification (to see why this is so, one must understand the signalling protocol used by generic DDR-II SSRAM devices).

There are two potential performance penalties in this memory port:

- Every access to a BL4 DDR-II SSRAM device must transfer 4 physical words, whose addresses are "consecutive", on the rd bus. Because this takes two clk0 cycles, random accesses to unrelated addresses when burst\_len is driven with 1 (to select BL4) incur a one cycle performance penalty. However, when burst\_len is driven with 0 (to select BL2), this performance penalty does not apply.

- Turning the **rd** bus around when a read command and a write command are entered in consecutive clock cycles requires one **clk0** cycle. Thus it incurs a one cycle performance penalty. This penalty occurs *only* if a write command is entered in the one-cycle window following entry of a read command.

Latency for read commands is fairly deterministic, since the penalties described above are limited to one cycle (although these penalties may be accumulated by successive commands). The best-case latency from entry of a read command (ce asserted with w deasserted) to valid asserted is approximately 9 clk0 cycles. Worst case latencies may be computed by adding the above penalties to the best-case latency.

The optimal usage pattern for this memory port is blocks of accesses of the same type (read or write) with addresses that increment by one on each successive access. When used optimally, a 32-bit wide DDR-II SSRAM memory port operating at a **clk0** frequency of 133MHz) can sustain approximately 1GB/s.

© Copyright 2001-2009 Alpha Data

## The ddrsdram\_port component

**Overview**

**HDL** source code

**Parameters**

**Signals**

Row / column address selection

**Performance**

#### Overview

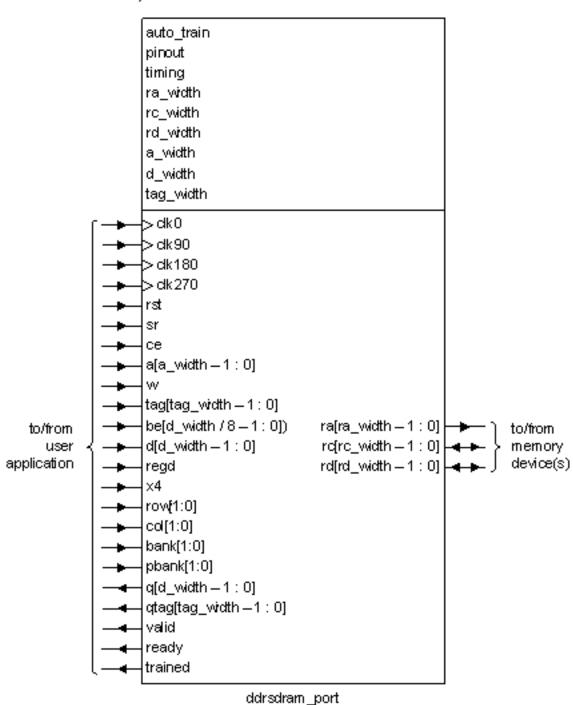

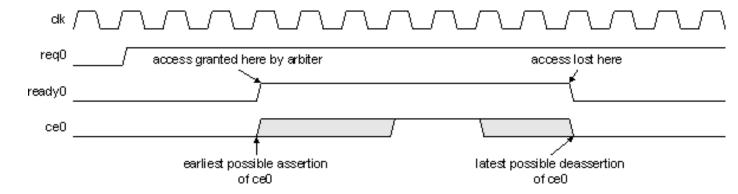

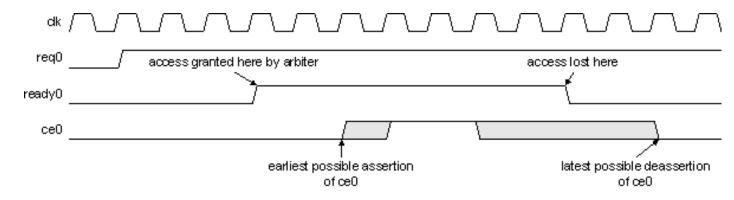

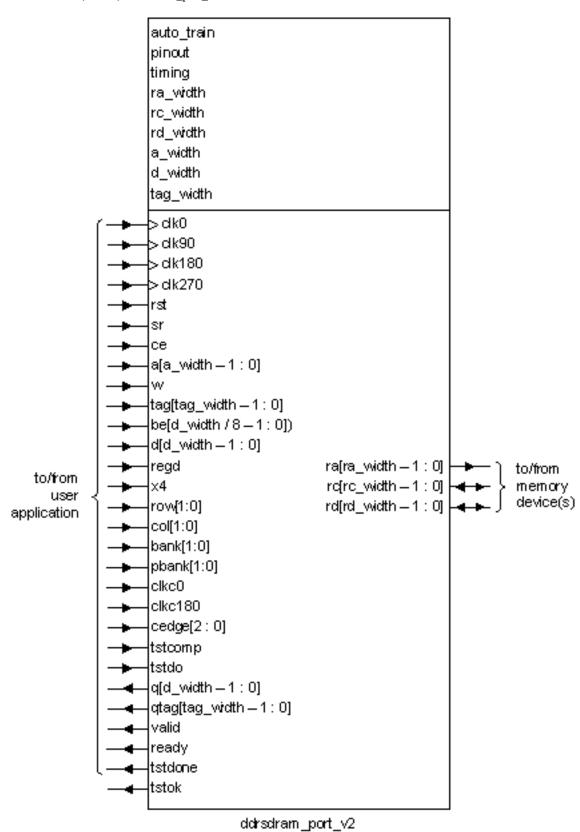

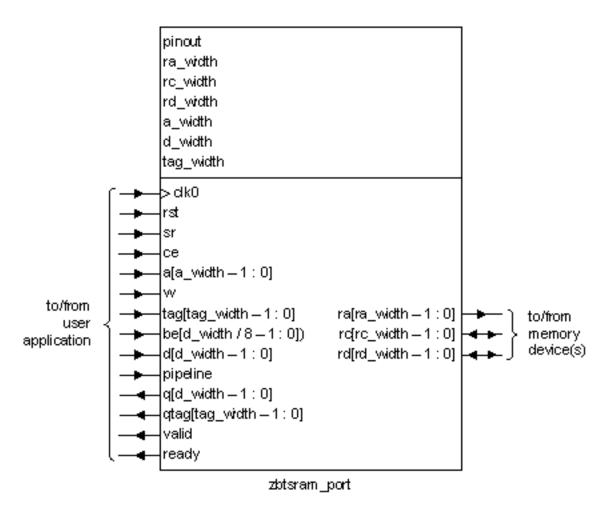

The ddrsdram\_port component is part of the memif package and implements an interface to a bank of DDR SDRAM memory. This component follows the generic user interface for memory ports, but also has a few additional parameters and sideband signals, as shown in the following figure:

#### **HDL** source code

fpga/vhdl/chipscope/src/ilap\_pkg.vhd

fpga/vhdl/common/memif/ddrsdram/ddrsdram\_dqs.vhd

Projects making use of this component must include all of the following source files (relative to root of SDK installation):

```

fpga/vhdl/chipscope/src/ilacombo_sim.vhd

fpga/vhdl/common/memif/memif_pkg.vhd

fpga/vhdl/common/memif/memif_int_pkg.vhd

fpga/vhdl/common/memif/memif_def_synth.vhd OR fpga/vhdl/common/memif/memif_def_sim.vhd

fpga/vhdl/common/memif/cmd_fifo.vhd

fpga/vhdl/common/memif/ddrsdram/ddrsdram_clkfw.vhd

fpga/vhdl/common/memif/ddrsdram/ddrsdram_ctrl.vhd

fpga/vhdl/common/memif/ddrsdram/ddrsdram_data.vhd

fpga/vhdl/common/memif/ddrsdram/ddrsdram_data_dqs.vhd

fpga/vhdl/common/memif/ddrsdram/ddrsdram_data_dqs.vhd

```

fpga/vhdl/common/memif/ddrsdram/ddrsdram\_dm.vhd fpga/vhdl/common/memif/ddrsdram/ddrsdram\_init.vhd fpga/vhdl/common/memif/ddrsdram/ddrsdram\_port.vhd

If synthesizing, the file **fpga/vhdl/common/memif/memif\_def\_synth.vhd** must be included. If simulating, the file **fpga/vhdl/common/memif/memif\_def\_sim.vhd** must be included instead.

#### **Parameters**

| Name       | Туре              | Function                                                                                                                                                                                                                                                                                  | Note |

|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| a_width    | natural           | Width in bits of the port logical address, a.                                                                                                                                                                                                                                             | 4    |

| auto_train | boolean           | If true, the memory port automatically trains itself after reset is deasserted. If false, the memory port does not train itself. This parameter has a default value of true, and in normal usage an application should rely on the default value, and not map it to any particular value. |      |

| d_width    | natural           | Width in bits of the port data in and out, <b>d</b> and <b>q</b> respectively.                                                                                                                                                                                                            | 3    |

| pinout     | ddrsdram_pinout_t | This value specifies the physical configuration of the memory port. For convenience, an application may map it to one of the <b>predefined constants</b> .                                                                                                                                |      |

| ra_width   | natural           | Width in bits of the memory device address bus, ra.                                                                                                                                                                                                                                       | 1    |

| rc_width   | natural           | Width in bits of the memory device control bus, rc.                                                                                                                                                                                                                                       | 2    |

| rd_width   | natural           | Width in bits of the memory device data bus, rd.                                                                                                                                                                                                                                          | 3    |

| tag_width  | natural           | Width in bits of the tag in and out, tag and qtag respectively.                                                                                                                                                                                                                           |      |

| timing     | ddrsdram_timing_t | This value specifies the timing of the memory port. For convenience, an application may map it to one of the <b>predefined constants</b> .                                                                                                                                                |      |

#### Notes:

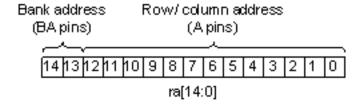

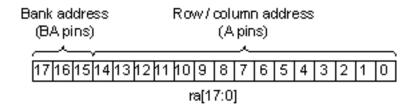

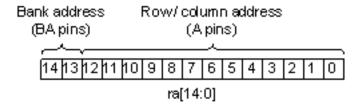

The memory device address bus, ra, is composed of two fields in this memory port, with the widths of each field specified by the num\_addr\_bits and num\_bank\_bits of the pinout parameter. Therefore, ra\_width is the sum of these two values. The following figure illustrates this for the case where num\_addr\_bits = 13 and num\_bank\_bits = 2:

Note that **ra\_width** and **pinout** are properties of the printed circuit board, indicating how many wires are physically present. On the other hand, the DDR SDRAM devices actually fitted to the printed circuit board may have less pins connected. The purpose of the **row**, **col**, **bank** and **pbank** signals is to specify at runtime the properties of the DDR SDRAM devices actually in use.

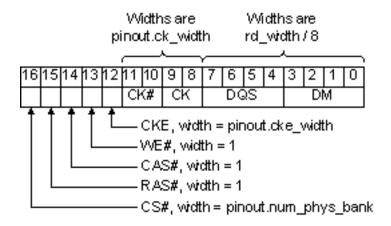

2. The memory device control bus, **rc**, is composed of various fields in this memory port, with the widths of certain fields specified by the **pinout** and **rd\_width** parameters. The following figure illustrates an example that puts **rc\_width** at 17:

The order of the fields within **rc** is always the same; only the field widths may differ from one model to another.

- 3. The rd\_width parameter is the number of physical DQ wires making up the data bus of the DDR SDRAM bank. This memory port transfers two words of data on the DQ wires for each command entered via the ce signal. Accordingly, the d\_width parameter, which is the width of d and q, is typically specified by the user application as being twice rd\_width. However, other values can be passed for d width:

- If d\_width > (2 \* rd\_width), then the memory port simply truncates d internally so that its width is (2 \* rd\_width). Data read from the memory devices is zero-extended so that its width is d\_width before being returned on q.

- o d width = (2 \* rd width) is the optimal usage case.

- If d\_width < (2 \* rd\_width), then the memory port zero-extends d internally so that its width is (2 \* rd\_width).</li>

- 4. The a\_width parameter is the width of the logical address bus, a. Generally, it must be sufficiently wide to be able to address all of the memory in a DDR SDRAM bank. Hence, the required value of a\_width depends on what memory devices are actually in use. As an example, consider two physical banks of DDR SDRAM devices that use 13 row bits, 10 column bits and 2 internal bank address bits. The number of address bits is:

```

13 (row address bits) +

10 (column address bits) +

2 (internal bank address bits) +

1 (2 physical banks / CS# pins) =

```

26

We must now subtract 1, because "logical" memory locations are twice as wide as the physical memory locations, due to transferring two words on the DQ pins for every command entered on **ce**. Hence **a\_width** for this configuration should be at least 25. When **a\_width** is larger than actually required, the top few unused bits of **a** are ignored by the memory port. In practice, one should determine the value of **a\_width** assuming that the largest possible memory devices are in use.

#### **Signals**

The signals of this interface to and from the user application are as follows:

| Signal | Type | Function | Note |  |

|--------|------|----------|------|--|

|        |      |          |      |  |

| а      | in | Logical address                                                                                                                                                                                                                                                                                                                     |      |

|--------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|        |    | User code must place a valid address on <b>a</b> when it asserts <b>ce</b> . Since a memory port effectively represents a memory device as a linear array of words of width <b>d_width</b> , this address is a logical address, rather than anything resembling what one might see on the <b>ra</b> bus.                            |      |

| bank   | in | Bank address width select (sideband signal)                                                                                                                                                                                                                                                                                         | 6, 8 |

|        |    | This input selects number of internal bank address bits for the DDR SDRAM devices in use:  00 => no internal bank address bits  01 => 1 internal bank address bits  10 => 2 internal bank address bits  11 => 3 internal bank address bits                                                                                          |      |

| be     | in | Byte enables to memory                                                                                                                                                                                                                                                                                                              |      |

|        |    | User code must place valid byte enables on <b>be</b> whenever a write command is entered ( <b>ce</b> and <b>w</b> both asserted). A logic 1 in a given bit of <b>be</b> means that the corresponding byte within <b>be</b> will be written to memory, while a zero means that the corresponding byte will not be written to memory. |      |

| се     | in | Command entry                                                                                                                                                                                                                                                                                                                       |      |

|        |    | User code asserts this signal to enter a new read or write command into the memory port. When asserted, <b>a</b> and <b>w</b> must be valid. When asserted along with <b>w</b> , <b>tag</b> must also be valid.                                                                                                                     |      |

|        |    | User code must not assert <b>ce</b> when <b>ready</b> is deasserted.                                                                                                                                                                                                                                                                |      |

|        |    | Other than that, there are no restrictions on how few or how many clock cycles <b>ce</b> can remain asserted. It can be pulsed for single <b>clk0</b> cycles, or asserted for many <b>clk0</b> cycles ( <b>ready</b> permitting).                                                                                                   |      |

|        |    | The address, byte enables, tag etc. of a command need not bear any relationship to that of the previous command, but refer to the section below for a <b>discussion of how to maximize performance</b> .                                                                                                                            |      |

| clk0   | in | Clock for user interface                                                                                                                                                                                                                                                                                                            | 7    |

|        |    | All other signals except <b>rst</b> are synchronous to <b>clk0</b> .                                                                                                                                                                                                                                                                |      |

| clk90  | in | High speed clock, phase 90                                                                                                                                                                                                                                                                                                          | 7    |

|        |    | This clock must be the same frequency as <b>clk0</b> but lagging by 90 degrees.                                                                                                                                                                                                                                                     |      |

| clk180 | in | High speed clock, phase 180                                                                                                                                                                                                                                                                                                         | 7    |

|        |    | This clock must be the same frequency as <b>clk0</b> but lagging by 180 degrees.                                                                                                                                                                                                                                                    |      |

| clk270 | in | High speed clock, phase 270                                                                                                                                                                                                                                                                                                         | 7    |

|        |    | This clock must be the same frequency as <b>clk0</b> but lagging by 270 degrees.                                                                                                                                                                                                                                                    |      |

| col    | in | Column address width select (sideband signal)                                                                                                                                                                                                                                                                                       | 6, 8 |

|        |    | This input selects the number of column address bits to use. Along with the <b>row</b> input, it specifies the row/column geometry of the DDR SDRAM device, as defined <b>here</b> .                                                                                                                                                |      |

|        |    |                                                                                                                                                                                                                                                                                                                                     |      |

| d     | in  | Data to memory                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|       |     | User code must place valid data on ${\bf d}$ whenever a write command is entered ( ${\bf ce}$ and ${\bf w}$ both asserted).                                                                                                                                                                                                                                                                                                           |      |

| pbank | in  | Physical bank select (sideband signal)                                                                                                                                                                                                                                                                                                                                                                                                | 6, 8 |

|       |     | This input selects the number of physical banks (chip-selects) in use for the DDR SDRAM devices:  00 => 1 physical bank / 1 CS#  01 => 2 physical bank / 2 CS#  10 => 4 physical bank / 4 CS#  11 => 8 physical bank / 8 CS#                                                                                                                                                                                                          |      |

| q     | out | Data from memory                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|       |     | When <b>valid</b> is asserted by the memory port (as a result of a read command), <b>q</b> reflects the data read from memory.                                                                                                                                                                                                                                                                                                        |      |

| qtag  | out | Tag out                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|       |     | When <b>valid</b> is asserted by the memory port (as a result of a read command), <b>qtag</b> reflects the tag value that was assocated with that read command.                                                                                                                                                                                                                                                                       |      |

| ready | out | Port ready                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|       |     | When the memory port asserts <b>ready</b> , user code is permitted to assert <b>ce</b> . Certain types of memory port may unconditionally assert <b>ready</b> , whereas other types of memory port may sometimes deassert <b>ready</b> depending on several factors.                                                                                                                                                                  |      |

|       |     | For example, a DDR SDRAM port is capable of buffering a certain number of commands internally, but if its command buffer is filled while it executes a refresh cycle, it will deassert <b>ready</b> .                                                                                                                                                                                                                                 |      |

| regd  | in  | Registered / unregistered select (sideband signal)                                                                                                                                                                                                                                                                                                                                                                                    | 6, 8 |

|       |     | This input selects whether the memory port expects registered DDR SDRAM memory or unregistered DDR SDRAM memory:  0 => unregistered                                                                                                                                                                                                                                                                                                   |      |

|       |     | 1 => registered                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| row   | in  | Row address width select (sideband signal)                                                                                                                                                                                                                                                                                                                                                                                            | 6, 8 |

|       |     | This input selects the number of row address bits to use. Along with the <b>col</b> input, it specifies the row/column geometry of the DDR SDRAM device, as defined <b>here</b> .                                                                                                                                                                                                                                                     |      |

| rst   | in  | Asynchronous reset for memory port                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|       |     | May be tied to logic 0 if not required.                                                                                                                                                                                                                                                                                                                                                                                               |      |

| sr    | in  | Synchronous reset for memory port                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|       |     | May be tied to logic 0 if not required.                                                                                                                                                                                                                                                                                                                                                                                               |      |

| tag   | in  | Tag in                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|       |     | When user code asserts <b>ce</b> with <b>w</b> deasserted, it must also place a valid tag on the <b>tag</b> signal. When, as a result of the read command, the memory port asserts <b>valid</b> , the <b>qtag</b> output reflects the tag value originally passed. This is intended to facilitate sharing of a memory port between several data sources or data sinks, where each source or sink recognizes a particular set of tags. |      |

|       |     |                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

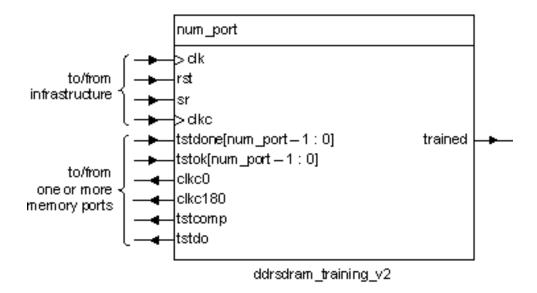

| trained<br>(sideband<br>signal) | out | Training success flag  When the memory port asserts <b>trained</b> , it indicates that training of the memory port was successful. When deasserted, either training is not yet complete or training was unsuccessful.                    |   |

|---------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| valid                           | out | Read data valid  When the memory port asserts <b>valid</b> , it does so as a result of a read command (user code asserted <b>ce</b> with <b>w</b> deasserted). When <b>valid</b> is asserted, both <b>q</b> and <b>qtag</b> are valid.   |   |

| W                               | in  | Write select  When user code asserts <b>ce</b> , it must place either a logic 1 on the <b>w</b> signal in order to select a write command, or 0 in order to select a read command.                                                       |   |

| x4                              | in  | X4 device select (sideband signal)  This input selects whether devices with 8- or 16-bit data or devices with 4-bit data are in use. Generally applicable to DIMM DDR SDRAM memory. In this version of the memory port, it must be zero. | 9 |

#### Notes:

- 5. The delay from deassertion of reset to completion of training (**trained** asserted) may be as long as 350ms. This is because a large post-reset delay is used in order to ensure that the memory port properly initializes the DDR SDRAM devices that it is controlling after power-on.

- For simulation, however, the memory port uses a much smaller post-reset delay, with the result that the delay from deassertion of reset to completion of training is dominated by the time spent training. This is in the order of 150 microseconds of simulation time at a **clk0** frequency of 133MHz.

- 6. Certain properties of a DDR SDRAM device, such as number of row and column address bits, might not be known at the time of building an FPGA design. Therefore, this memory port allows certain properties to be specified "at runtime". An application might interrogate some Vital Product Data in order to determine the proper values to drive on the row, col, bank, and pbank signals.

- Alternatively, if the designer can guarantee that the properties of the DDR SDRAM devices are known when building the FPGA design, these signals can be driven with constant values. This has the advantage of lower slice utilization.

- In any case, for reliable operation, these signals must not change unless the memory port is idle.

- The purpose of these signals should not be confused with that of the **pinout** parameter. The **pinout** parameter specifies properties of the circuit board on which the FPGA and DDR SDRAM devices are mounted. In general, the number of physical wires on the circuit board provided for addressing the DDR SDRAM devices can be greater than the number actually used by a particular DDR SDRAM device.

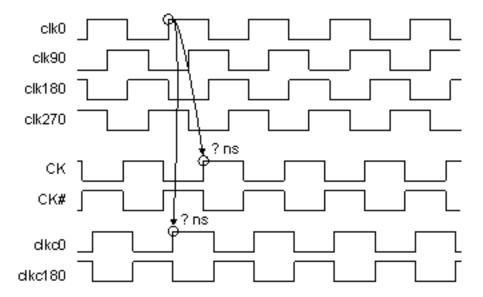

- 7. The phase and frequency relationships between the four clock phases are illustrated by the following figure:

Also shown is the DDR SDRAM clock, CK. Its frequency is the same as clk0, but its phase is indeterminate.

- 8. For correction operation, all sideband inputs must be static while the memory port is not idle.

- 9. In this version, the **x4** sideband input must be driven with a constant.

The signals of this interface to and from the memory device(s) are as follows:

| Signal | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ra     | in    | Memory device address bus  This bus carries address information to from the memory port to the memory device(s). For devices with a nontrivial addressing scheme, this address may be composed of various fields. These fields are bundled together into the ra bus so that, for the most part, the user application need not care what they are.  Refer to note 1 for the mapping of the ra bus to device pins. |

| rc     | inout | Memory device control bus  This bus carries control signals between the memory port and the memory device(s), and is composed of various fields.  These signals are bundled together into the rc bus so that, for the most part, the user application need not care what they are.  Refer to note 2 for the mapping of the rc bus to device pins.                                                                |

| rd     | inout | Memory device data bus  This bus carries data between the memory port and the memory device(s). For each command entered via ce, two words are transferred on rd, which determines the relationship between the rd_width and d_width parameters. Refer to note 3 for details.                                                                                                                                    |

#### Row / column address selection

The **row** and **col** sideband inputs together determine the number address bits used for row and column addresses, as in the following table:

| [4 0]    | 154 01   | All of a little and  | All of call and block and |

|----------|----------|----------------------|---------------------------|

| row[1:0] | col[1:0] | No. of row bits used | No. of column bits used   |

| 00 | 00 | 12 | 8  |

|----|----|----|----|

| 00 | 01 | 12 | 9  |

| 00 | 10 | 12 | 10 |

| 00 | 11 | 12 | 11 |

| 01 | 00 | 13 | 9  |

| 01 | 01 | 13 | 10 |

| 01 | 10 | 13 | 11 |

| 01 | 11 | 13 | 12 |

| 10 | 00 | 14 | 10 |

| 10 | 01 | 14 | 11 |

| 10 | 10 | 14 | 12 |

| 10 | 11 | 14 | 13 |

| 11 | 00 | 15 | 11 |

| 11 | 01 | 15 | 12 |

| 11 | 10 | 15 | 13 |

| 11 | 11 | 15 | 14 |

#### **Performance**

This memory port features an internal command buffer capable of buffering about 10 commands before deasserting the **ready** signal. Most of the time, the rate of consumption of commands from the command buffer is at least as fast as production of new commands by the user application. Periodically, however, the memory port must refresh the DDR SDRAM devices it is controlling, which may result in an accumulated backlog of buffered commands, and deassertion of the **ready** signal. Certain usage patterns, such as alternating between read and write commands, may also have the same effect.

The architecture of DDR SDRAM device consists of a number of internal banks which are in turn divided into a number of pages. At any moment, a given bank may be "closed", or may have a given page "open". Opening or closing a bank takes a finite number of clock cycles. In this memory port, the following performance penalties exist for memory accesses falling into the following patterns:

- Several clk0 cycles for changing from read to write or write to read within the same page and bank.

- In the order of 8 clk0 cycles for consecutive accesses that fall within different pages of the same bank, or within different banks.

- In the order of 8-20 clk0 cycles for an access that occurs while the memory port is performing a refresh.

Latency for read commands is nondeterministic due to the penalties described above, particularly because of the need to refresh, but the best-case latency from entry of a read command (ce asserted with w deasserted) to valid asserted is approximately 11 clk0 cycles. This can be modified somewhat by tightening or relaxing the timing as specified by the timing parameter. Worst case latencies may be computed by adding the above penalties to the best-case latency.

The optimal usage pattern for this memory port is blocks of accesses of the same type (read or write) to the same bank and page. A linearly incrementing address is an example of an optimal usage pattern. When used optimally, this memory port with 32 physical data bits (**rd** is 32) operating at a **clk0** frequency of 133MHz can sustain approximately 1GB/s.

# © Copyright 2001-2009 Alpha Data

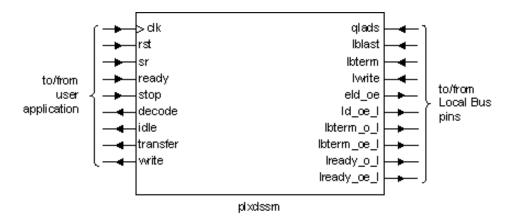

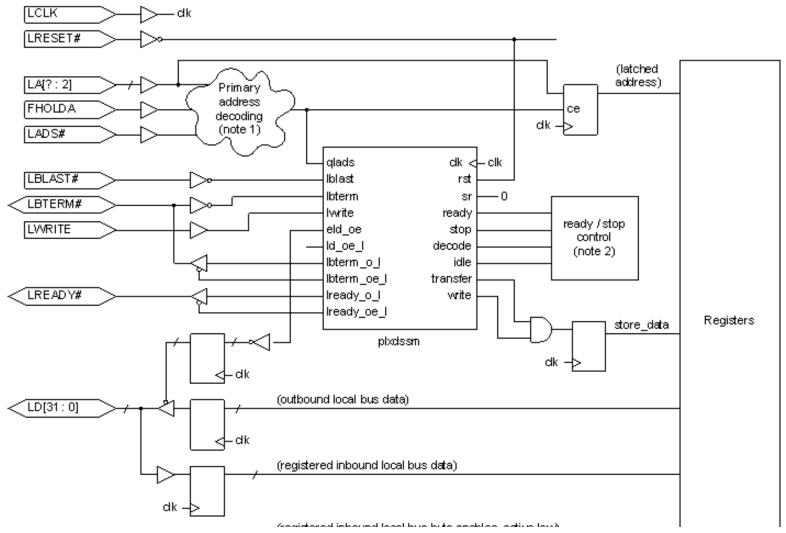

## **PLXSIM VHDL reference**

**Datatypes**

**Constants**

**Functions and procedures**

**Components**

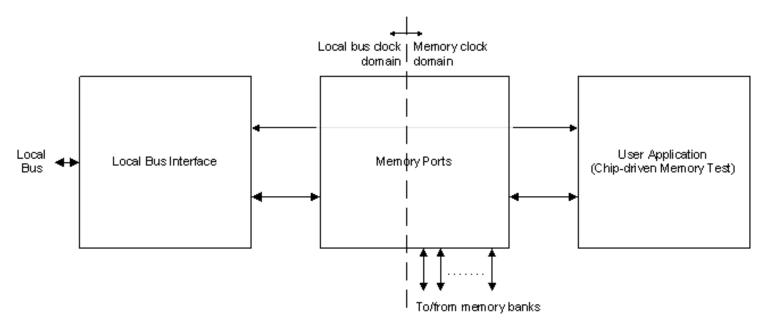

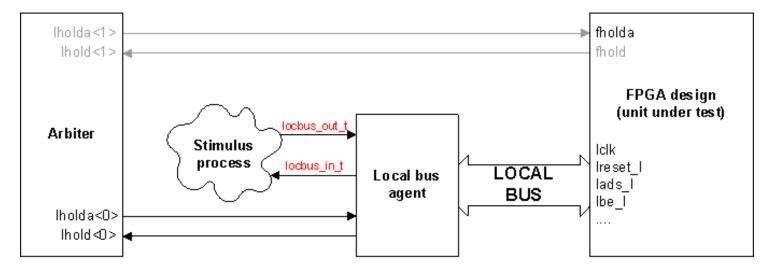

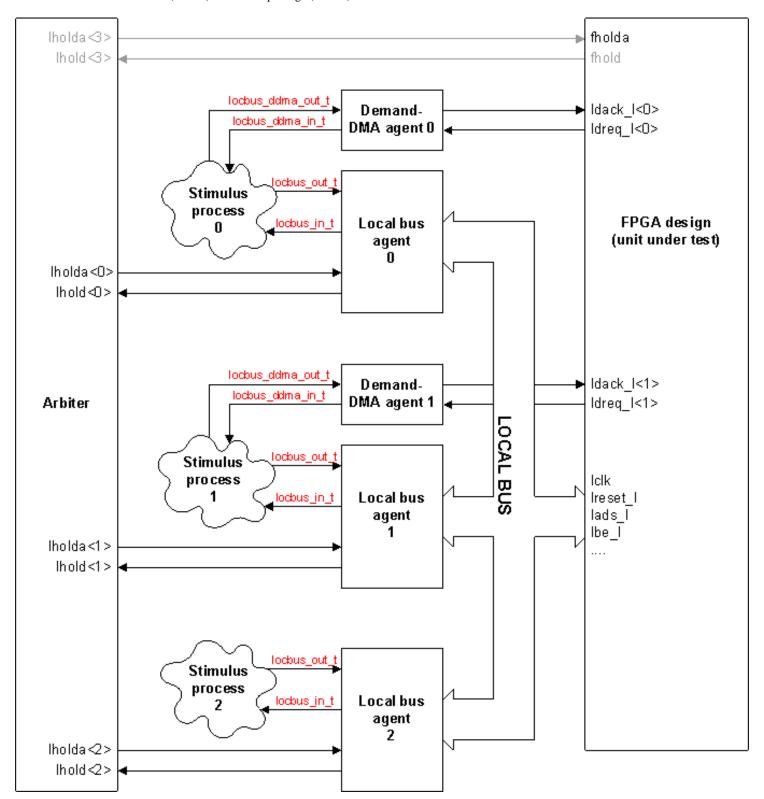

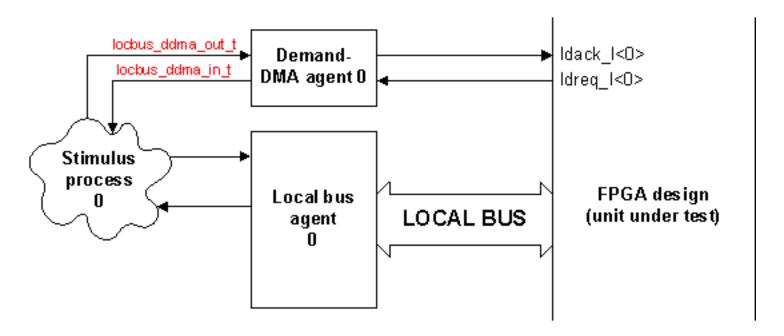

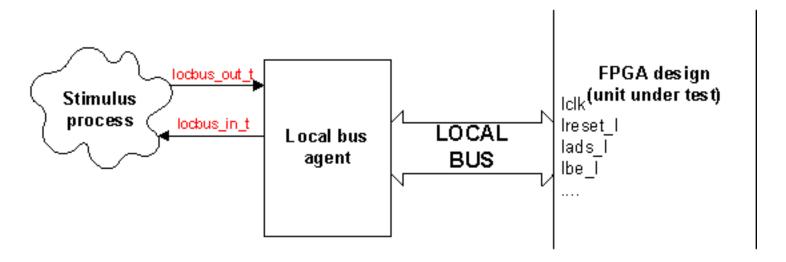

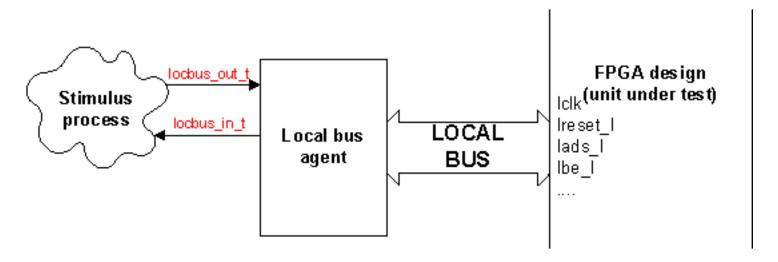

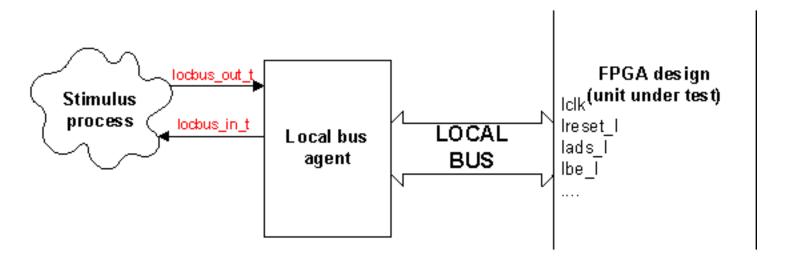

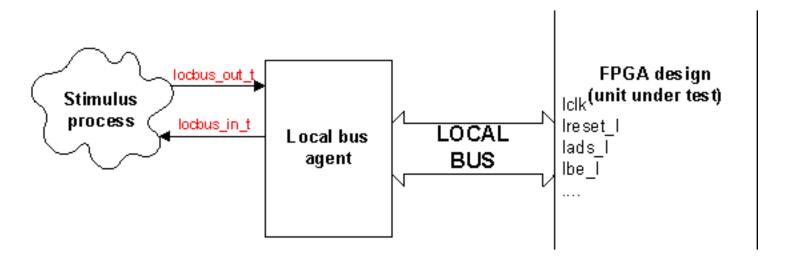

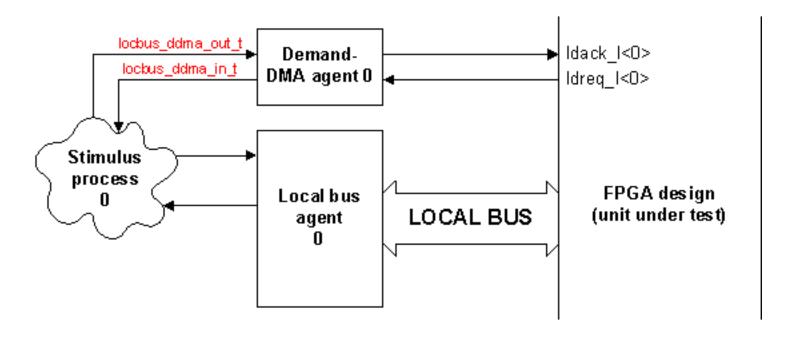

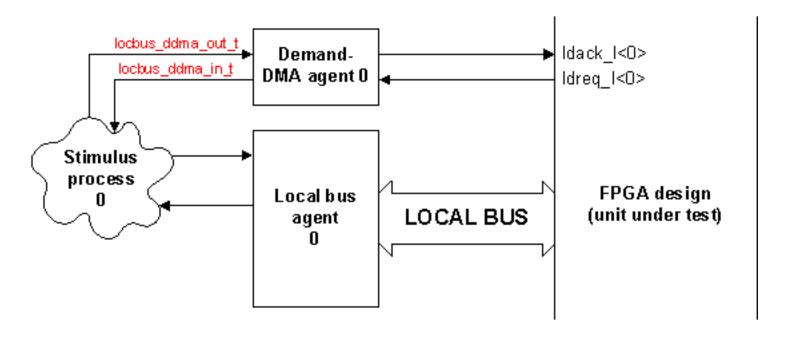

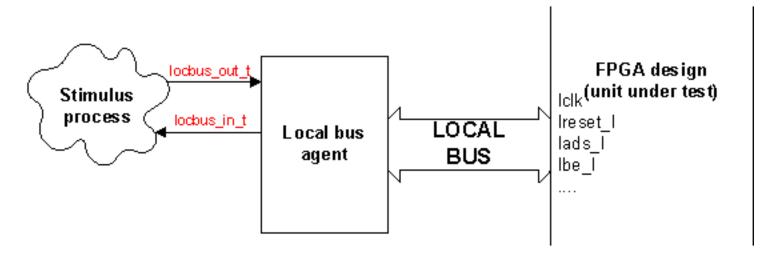

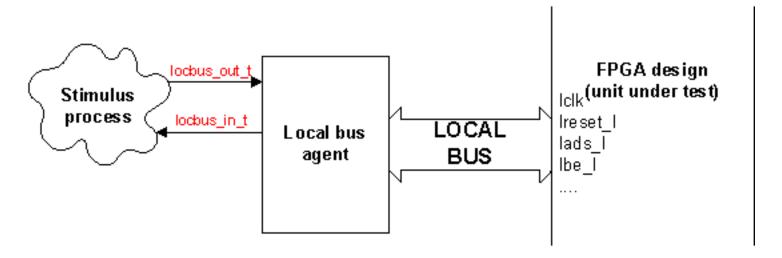

This section documents the VHDL implementation of the **PLXSIM** package. This package consists datatypes, constants, functions, procedures and components designed to speed up development of a VHDL testbench centered around the local bus interface of an FPGA design.

## **Datatypes**

| Name              | Purpose                                                                                                                               |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| byte_enable_t     | A vector type used to pass the byte enables for a local bus transfer                                                                  |

| byte_t            | A type that can hold a single byte of data                                                                                            |

| byte_vector_t     | A vector type used to hold the data for a local bus transfer                                                                          |

| integer_vector_t  | A vector type used to hold an array of integers                                                                                       |

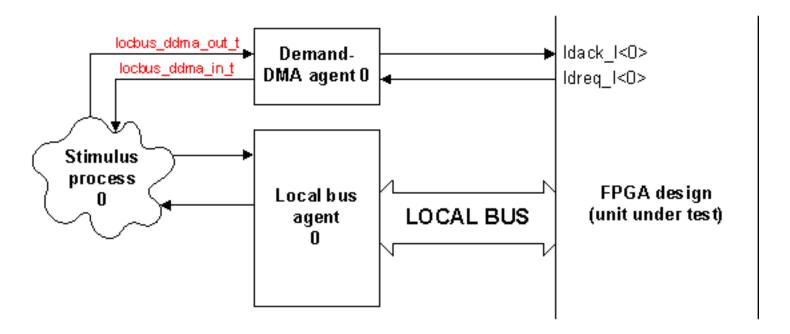

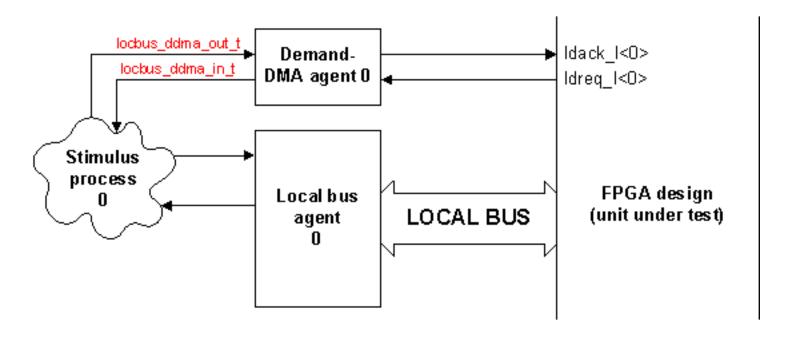

| locbus_ddma_in_t  | A record type used to make a bundle of the demand-mode DMA signals for a particular DMA channel that are input by a stimulus process  |

| locbus_ddma_out_t | A record type used to make a bundle of the demand-mode DMA signals for a particular DMA channel that are driven by a stimulus process |

| locbus_in_t       | A record type used to make a bundle of the local bus signals that are input by a stimulus process                                     |

| locbus_out_t      | A record type used to make a bundle of the local bus signals that are driven by a stimulus process                                    |

#### **Constants**

| Name                 | Purpose                                                                                                               |

|----------------------|-----------------------------------------------------------------------------------------------------------------------|

| init_locbus_ddma_out | A constant that can be used to initialize variables/signals of type <a href="locbus_ddma_out_t">locbus_ddma_out_t</a> |

| init_locbus_out      | A constant that can be used to initialize variables/signals of type <a href="locbus_out_t">locbus_out_t</a>           |

## **Functions and procedures**

| Name             | Purpose                                 |

|------------------|-----------------------------------------|

| conv_byte_vector | A function for converting values to the |

# Components

| Name                | Purpose                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

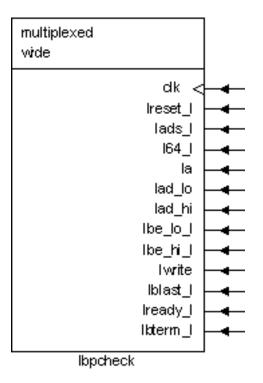

| Ibpcheck            | A component that can be instantiated in a testbench in order to flag local bus protocol violations                                      |

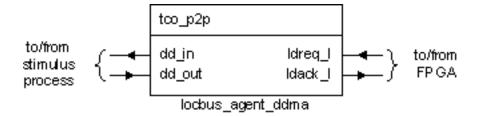

| locbus_agent_ddma   | A component that can be instantiated in order to connect a stimulus process to the demand-mode DMA signals for a particular DMA channel |

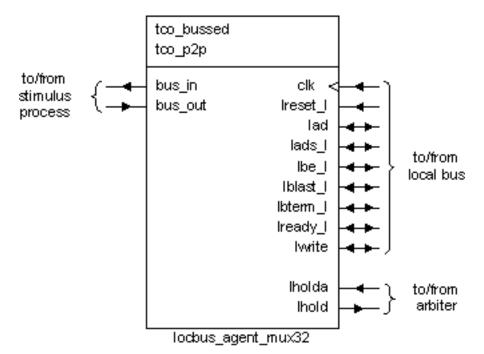

| locbus_agent_mux32  | A component that can be instantiated in order to connect a stimulus process to a 32-bit multiplexed address/data local bus              |

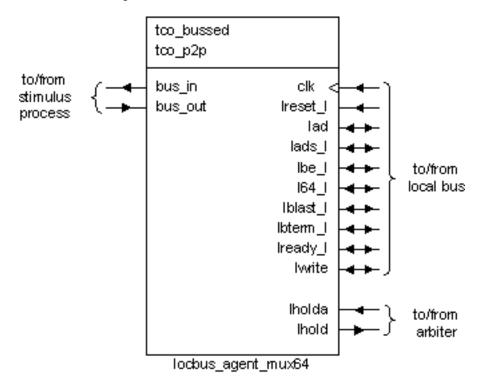

| locbus_agent_mux64  | A component that can be instantiated in order to connect a stimulus process to a 64-bit multiplexed address/data local bus              |

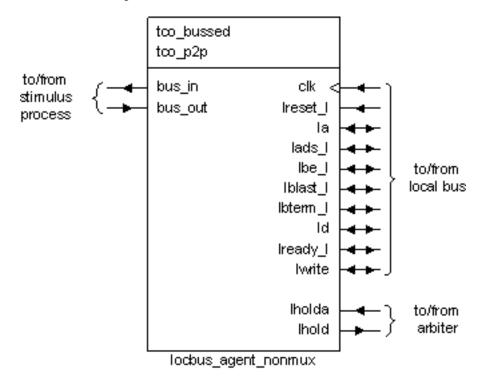

| locbus_agent_nonmux | A component that can be instantiated in order to connect a stimulus process to a 32-bit nonmultiplexed address/data local bus           |

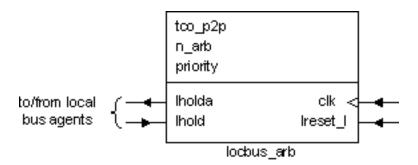

| locbus_arb | A component that can be instantiated in order to arbitrate |

|------------|------------------------------------------------------------|

|            | between stimulus processes for local bus access            |

Document version: 4.9.3.1

© Copyright 2001-2009 Alpha Data

© Copyright 2001-2009 Alpha Data

# Introduction

Please choose one of the following topics:

**About the ADM-XRC SDK**

**Hardware supported**

List of changes

**Upgrades to the SDK**

Sales and support

© Copyright 2001-2009 Alpha Data

#### About the ADM-XRC SDK

The ADM-XRC SDK is a set of resources including an **application-programming interface** (API) intended to assist the user in creating an application using one of Alpha Data's range of reconfigurable computing cards. The API is a thin layer in user space that makes the necessary open, close and device I/O control calls to a kernel-mode device driver provided by Alpha Data as a **related package**.

The ADM-XRC SDK consists of the following components:

- ADM-XRC SDK documentation (this document).

- Documentation for PLX Technology's PCI9080 and PCI9656.

- Sample applications in source and binary form.

- Sample FPGA designs in source and bitstream form.

- A primer on the local bus used by Alpha Data's reconfigurable computing cards.

- FPGA pinouts in the form of constraints (UCF) files.

- API header files.

- API import libraries.

## © Copyright 2001-2009 Alpha Data

# Hardware supported in this version of the SDK

This version of the SDK supports the following models in Alpha Data's reconfigurable computing range:

- ADM-XRC

- ADM-XRC-P

- ADM-XRC-II-Lite

- ADM-XRC-II

- ADM-XPL

- ADM-XP

- ADP-WRC-II

- ADP-DRC-II

- ADP-XPI

- ADM-XRC-4LX

- ADM-XRC-4SX

- ADM-XRC-4FX (and ADM-XMC-4FX)

- ADPE-XRC-4FX

- ADM-XRC-5LX

- ADM-XRC-5T1

- ADM-XRC-5T2

- ADM-XRC-5T2-ADV

- ADM-XRC-5TZ

- ADM-XRC-5T-DA1

This version of the SDK supports the above cards fitted with any of the following FPGAs:

- Virtex family:

- o XCV400BG560

- o XCV600BG560

- o XCV800BG560

- o XCV1000BG560

- · Virtex-E family:

- XCV1000EBG560

- o XCV1600EBG560

- o XCV2000EBG560

- · Virtex-EM family:

- o XCV405EBG560

- XCV812EBG560

- · Virtex-II family:

- o XC2V1000FG456

- o XCV2V3000FF1152

- o XCV2V4000FF1152

- o XCV2V6000FF1152

- o XCV2V8000FF1152

- o XCV2V6000FF1517

- o XCV2V8000FF1517

- Virtex-II Pro family:

- o XC2VP7FF896

- XC2VP20FF896

- o XC2VP30FF896

- o XC2VP70FF1704

- o XC2VP100FF1704

- Virtex-4 family:

- XC4VLX60FF1148

- o XC4VLX80FF1148

- o XC4VLX100FF1148

- o XC4VLX160FF1148

- XC4VSX55FF1148

- XC4VFX100FF1517

- o XC4VFX140FF1517

- · Virtex-5 family:

- o XC5VLX110FF1153

- XC5VFX70TFF1136

- XC5VFX100TFF1136

- XC5VFX100TFF1738

- XC5VFX130TFF1738

- o XC5VFX200TFF1738

- o XC5VLX110TFF1136

- o XC5VLX110TFF1738

- XC5VLX155TFF1136

- XC5VLX155TFF1738

- o XC5VLX220TFF1738

- o XC5VLX330TFF1738

- o XC5VSX95TFF1136

- o XC5VSX240TFF1738

© Copyright 2001-2009 Alpha Data

# List of changes

For a detailed list of changes, please refer to the file changes.txt in the base directory of the SDK.

© Copyright 2001-2009 Alpha Data

# **Upgrades to the ADM-XRC SDK**

From time to time, newer versions of the SDK will become available on the Alpha Data FTP site at **ftp://ftp.alpha-data.com**, in the **pub/admxrc/windows** directory.

Backwards source and binary compatibility will be maintained in the API whenever possible. Alpha Data reserves the right to change the sample applications and FPGA designs as part of a policy of continual improvement.

# © Copyright 2001-2009 Alpha Data

# How to get support

Alpha Data's FTP site, containing resources for customers, is **ftp.alpha-data.com**.

Alpha Data technical personnel may be contacted by phone, fax or e-mail:

|         | us                     | Rest of World          |

|---------|------------------------|------------------------|

| Phone:  | (408) 916 5713         | +44 131 558 2600       |

| Fax:    | (408) 436 5524         | +44 131 558 2700       |

| E-mail: | support@alpha-data.com | support@alpha-data.com |

| Web:    | www.alpha-data.com     | www.alpha-data.com     |

© Copyright 2001-2009 Alpha Data

# Installation

Please choose one of the following topics:

**Before installation**

**After installation**

© Copyright 2001-2009 Alpha Data

#### Before installation

Beginning with release 4.5.1, the ADM-XRC SDK for Windows package installs by default to a folder that contains the release number. The default installation folder for this release is:

%SystemDrive%\ADMXRC\_SDK4.9.3

In many cases, **SystemDrive** simply equates to **C**:. Since the SDK release number forms a part of the name of the installation folder, it is possible to keep several versions of the SDK on one system. A folder at the root of the system drive is chosen rather than a folder such as **"Program Files"** because, as of writing, some of the Xilinx ISE tools do not permit spaces in filenames.

It is not necessary to install the ADM-XRC driver before installing the SDK, although it will not be possible to run any applications until you have done so. The recommended ADM-XRC driver version for this version of the SDK is 3.16 or later.

**After installation**

© Copyright 2001-2009 Alpha Data

## After installation tasks

After installation of the ADM-XRC SDK, in order to start developing applications, you will need to configure your C compiler to use the API header files and libraries:

**Configuring the MSVC IDE**

**Configuring the Borland C++ command line tools**

This release of the SDK does not provide Xilinx Project Navigator files, because as of ISE 7.1i, Xilinx adopted a binary file format that stores absolute pathnames. However, a script is provided that creates project files for all sample FPGA designs, and this can be executed after installing the SDK. For further information, see:

**Generating ISE Project Navigator files for sample FPGA designs**

© Copyright 2001-2009 Alpha Data

# **Configuring the MSVC IDE**

In order to build applications using the ADM-XRC SDK, the compiler must be able to locate the API header file, and the linker must be able to locate the appropriate version of the API library. There are two ways to accomplish this with the Microsoft Visual C++ Integrated Development Environment (MSVC IDE):

**MSVC IDE global options**

**MSCV IDE per-project options**

#### © Copyright 2001-2009 Alpha Data

# Configuring the MSVC IDE, global options

This section assumes that that the ADM-XRC SDK has been installed in the default location, namely

C:\ADMXRC\_SDK4.9.3

The search paths that are applied when building **any** application in MSVC can be changed. If you decide to use this method of configuring MSVC, bear in mind that the ADM-XRC header files and import libraries will become visible for inclusion to **all applications** that you subsequently build using the IDE.

- 1. Select Tools->Options from the menu within the MSVC IDE.

- 2. In the Options dialogue box, select the C/C++ tab, and then select Include files from the Show directories for list. Add this path:

C:\ADMXRC\_SDK4.9.3\include

3. Select Library files from the Show directories for list. Add this path:

C:\ADMXRC SDK4.9.3\lib\msvc

4. Click **OK** to apply the changes.

The new include and library search paths will apply to any project subsequently built with the MSVC++ IDE. Note that you will need to specify the API library to the linker on a per-project basis. To do this, follow these steps:

- 1. Select **Project->Settings** from the menu. Ensure that the correct project is highlighted on the left hand side of the **Project Settings** dialog box.

- 2. Select the configuration(s) you want to change Win32 Debug, Win32 Release or All Configurations from the Settings for list.

- 3. Select the Link tab and add the API library to the list of .lib files in the Object/Library modules field.

- 4. Add either admxrc.lib (Release version) or admxrcd.lib (Debug version).

- 5. Click **OK** to apply the changes.

#### © Copyright 2001-2009 Alpha Data

# Configuring the MSVC IDE, per-project options

This section assumes that that the ADM-XRC SDK has been installed in the default location, namely

C:\ADMXRC\_SDK4.9.3

Altering the global MSVC options may not desirable. In this case, the ADM-XRC API header and library files may be added to the search paths on a per-project basis. To do this, follow these steps:

- Select Project->Settings from the menu. Ensure that the correct project is highlighted on the left hand side of the Project Settings dialog box.

- Select the configuration(s) you want to change Win32 Debug, Win32 Release or All Configurations from the Settings for list.

- 3. Select the C/C++ tab and then select Preprocessor from the Category list.

- 4. Add the path

C:\ADMXRC\_SDK4.9.3\include

to the Additional include directories field.

- 5. Select the Link tab and then select Input from the Category list.

- 6. Add the path

C:\ADMXRC\_SDK4.9.3\lib\msvc

to the Additional library path field.

- 7. Add the API library to the list of .lib files in the **Object/Library modules** field. This must be **admxrc.lib** (to use the Release version) or **admxrcd.lib** (to use the Debug version).

- 8. Click OK to apply the changes, which will require the project to be completely rebuilt in order to take effect.

© Copyright 2001-2009 Alpha Data

## Configuring the Borland C++ command line tools

This section assumes that that the ADM-XRC SDK has been installed in the default location, namely:

```

C:\ADMXRC_SDK4.9.3

```

In order to build applications using the ADM-XRC SDK, the compiler must be able to locate the API header file, and the linker must be able to locate the appropriate version of the API library. The Borland C++ command line tools allow the library and include file search paths to be customized via the **BCC32.CFG** and **ILINK32.CFG** files, which are usually located in the bin\ directory of the Borland C++ tools installation.

Add this line to BCC32.CFG:

```

-I"C:\ADMXRC_SDK4.9.3\include"

```

Add this line to ILINK32.CFG:

```

-L"C:\ADMXRC_SDK4.9.3\lib\Borland"

```

**Important note:** there appears to be a bug in the Borland C++ command line tools, manifested when specifying a quoted paths with spaces in configuration files such as **BCC32.CFG**. In order for the tools to correctly pick up these paths, there must be at least one space at the end of such lines in the configuration file. To illustrate this, let + denote a space character. A **BCC32.CFG** file including this workaround would look like:

```

-IC:\borland\bcc55\include

```

-j10

<sup>-</sup>I"C:\some+path\include"+

© Copyright 2001-2009 Alpha Data

# Installable packages

In order to develop applications for an Alpha Data reconfigurable computing card on a Windows platform, the package <a href="admxrc-sdk-win32-4.9.3">admxrc-sdk-win32-4.9.3</a> should be installed:

| Package                | Platforms supported                                                              |

|------------------------|----------------------------------------------------------------------------------|

| admxrc-sdk-win32-4.9.3 | Windows 98 Windows ME Windows NT 4.0 Windows 2000 Windows XP Windows Server 2003 |

In order to run applications on an Alpha Data reconfigurable computing card on a Windows platform, the appropriate driver package should be installed:

| Package                   | Platforms supported                                                                                      |

|---------------------------|----------------------------------------------------------------------------------------------------------|

| admxrc-driver-win2k-3.16  | Windows 2000 Windows XP (x86) Windows XP (x86_64) Windows Server 2003 (x86) Windows Server 2003 (x86_64) |

| admxrc-driver-winnt4-3.16 | Windows NT 4.0 + Service Pack 6                                                                          |

It is recommended that the most up to date driver version currently available be installed. At the time of writing, this is version 3.16.

© Copyright 2001-2009 Alpha Data

# Sample applications

A number of sample applications, written in C, are included with the SDK. Some of these use the **sample FPGA designs** included with the SDK.

Running the sample applications

Rebuilding the sample applications

Sample application list

© Copyright 2001-2009 Alpha Data

## Running the sample applications

### ADMXRC\_SDK4 environment variable

Some of the sample applications, for example **memtest**, require bitstreams from the sample FPGA designs in order to run. In order that these applications can locate any required bitstreams, the environment variable **ADMXRC\_SDK4** must be correctly set to point to the base directory of where the SDK has been installed. For example:

```

set ADMXRC_SDK4=C:\ADMXRC_SDK4.9.3

```

Normally, this variable is set automatically during installation of the SDK, but users may wish to set it manually (if, for example, it is desirable to have more than one version of the SDK installed).

#### **Command line invocation**

Binaries for the sample applications are provided prebuilt in the **bin\** directory of the SDK, and can be invoked from the command line. For example:

```

C:

cd C:\ADMXRC_SDK4.9.3\bin

memtest

```

© Copyright 2001-2009 Alpha Data

# Rebuilding the sample applications

The sample applications are supplied in source code form in the **apps\** directory of the SDK. They may be compiled using the MSVC command line tools, the MSVC IDE or the Borland C++ command line tools.

Building the sample applications using MSVC

Building the sample applications using Borland C++ command line tools

© Copyright 2001-2009 Alpha Data

## **Building the sample applications with MSVC**

The workspace apps\apps.dsw contains all of the sample applications. In order to build all of the applications, follow these steps:

- 1. Open the workspace apps\apps.dsw.