# ON THE IMPLEMENTATION OF AN ANALOG ATPG

· ·

.

· · · ·

• .•

by

CHIN-LONG WEY, B.S., M.S.

# A DISSERTATION

IN

# ELECTRICAL ENGINEERING

Submitted to the Graduate Faculty of Texas Tech University in Partial Fulfillment of the Requirements for the Degree of

DOCTOR OF PHILOSOPHY

•

### ACKNOWLEDGEMENTS

I would like to express my sincere thanks to Paul Whitfield Horn Professor Richard E. Saeks for his expert guidance of this dissertation, Professors Kwong Shu Chao, John F. Walkup, Erich E. Kunhardt and Kazuo Nakajima for serving on my committee.

Thanks also to Mrs. Pansy Burtis for her fine work in typing this dissertation, and Mr. Henry Ford and Dr. Ashok Iyer for their suggestions. It is a pleasure acknowledging their help.

Finally a special thanks to my wife, Lih-Er, my parents, brothers, sisters and friends for their encouragement and support during my entire education.

# TABLE OF CONTENTS

.

·•

| ** 、 •           |                                           |    |  |

|------------------|-------------------------------------------|----|--|

| ACKNOWLEDGEMENTS |                                           |    |  |

| LIST OF T        | ABLES                                     | iv |  |

| LIST OF F        | IGURES                                    | ν  |  |

| Ι.               | Introduction                              | 1  |  |

|                  | The Self-Testing Algorithm                | 4  |  |

|                  | Overview of Automatic Testing Programming | 6  |  |

|                  | Organization                              | 9  |  |

| II.              | The Simulation Model                      | 11 |  |

|                  | Linear Case                               | 11 |  |

| •                | Nonlinear Case                            | 14 |  |

| III.             | Software Development                      | 17 |  |

|                  | Linear Case                               | 18 |  |

|                  | Nonlinear Case                            | 26 |  |

| IV.              | Algorithms                                | 39 |  |

|                  | Supporting Algorithms                     | 39 |  |

|                  | Decision Algorithms                       | 52 |  |

| ۷.               | Examples                                  | 71 |  |

|                  | Linear Case                               | 71 |  |

|                  | Nonlinear Case                            | 83 |  |

| VI.              | Conclusions                               | 99 |  |

| REFERENCES       |                                           |    |  |

| APPENDIX         |                                           |    |  |

# LIST OF TABLES

.

•

| Table 4.1. | Coupling Table with the Test Result | 59 |

|------------|-------------------------------------|----|

| •          | Data Sheet - Linear Circuit         | 72 |

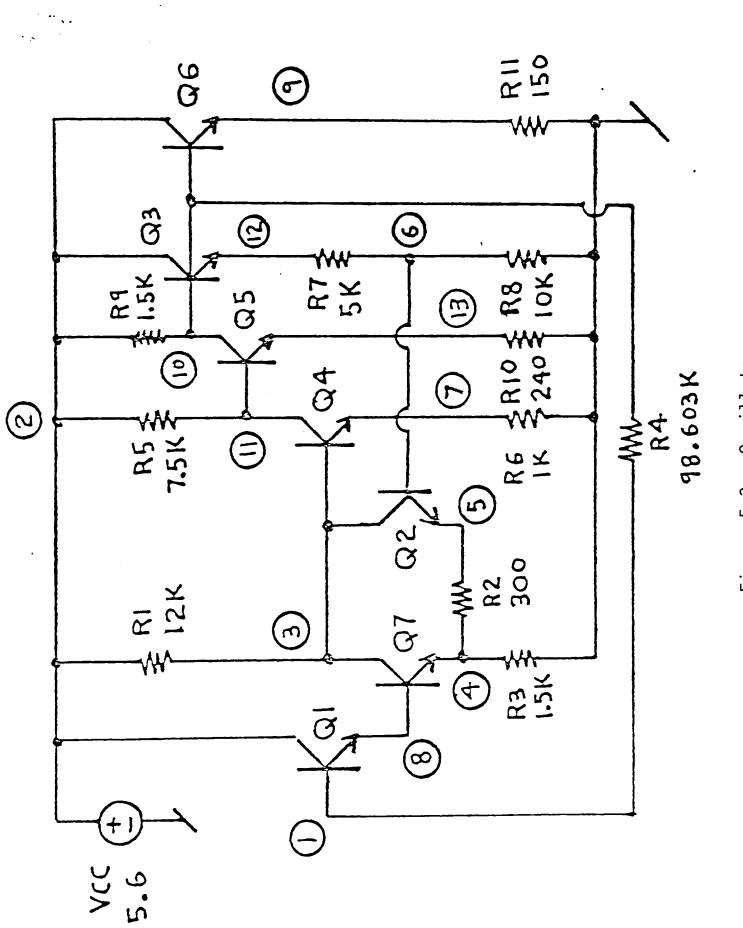

| Table 5.2. | Data Sheet - Nonlinear Circuit      | 84 |

| Table 5.3. | Test Results - Nonlinear Circuits   | 98 |

•

•

۰

-

.

# LIST OF FIGURES

•

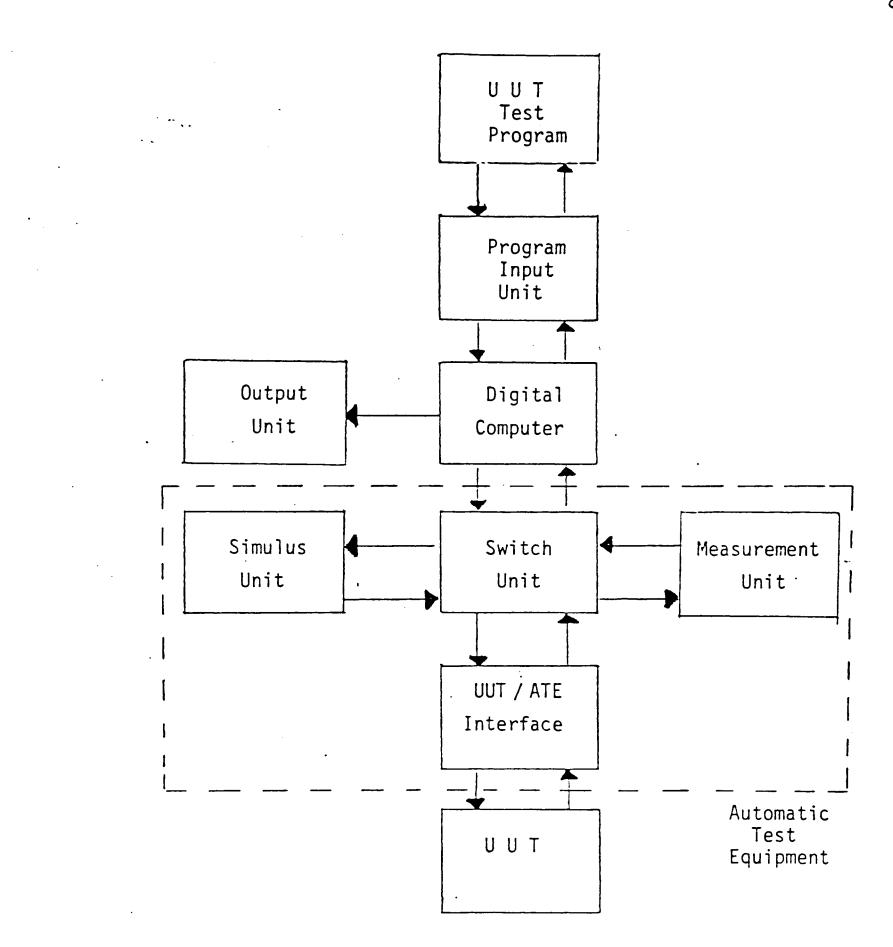

| Figure | 1.1. | Simplified Block Diagram of Typical ATE    | 8  |

|--------|------|--------------------------------------------|----|

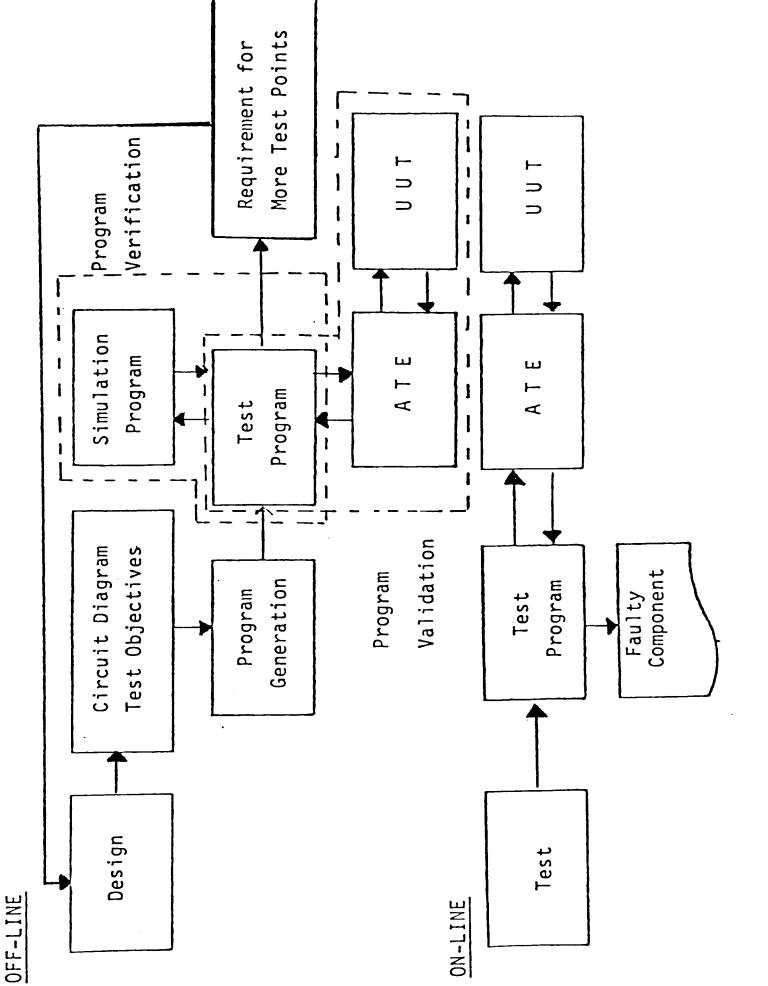

| Figure | 3.1. | Design and Test of a Unit Under Test (UUT) | 18 |

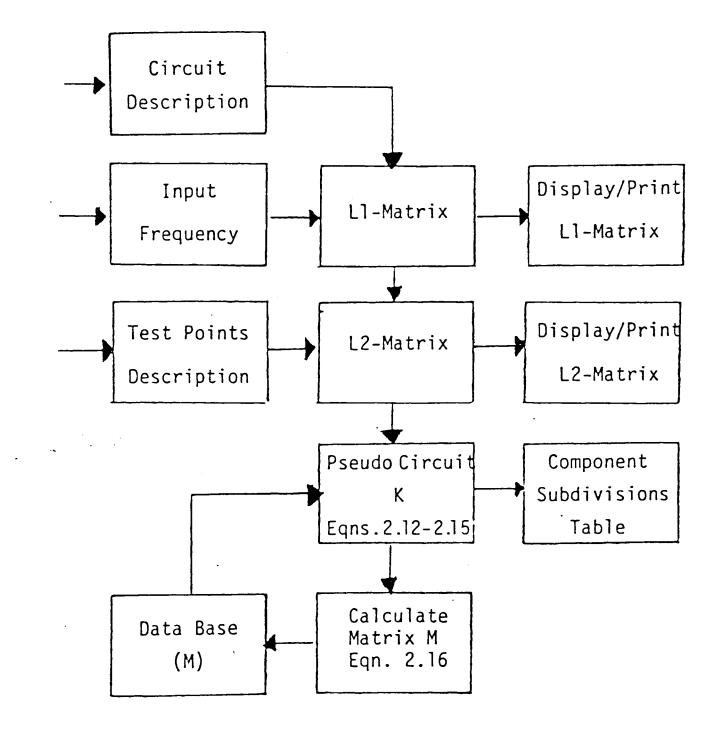

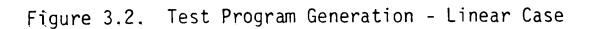

| Figure | 3.2. | Test Program Generation - Linear Case      | 20 |

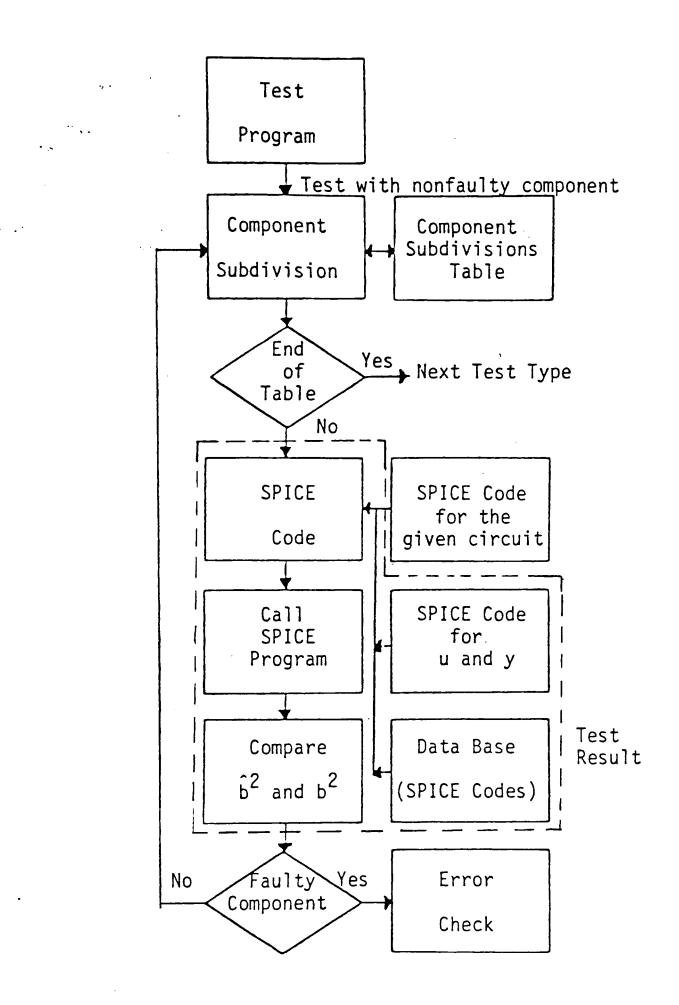

| Figure | 3.3. | Program Verification - Linear Case         | 23 |

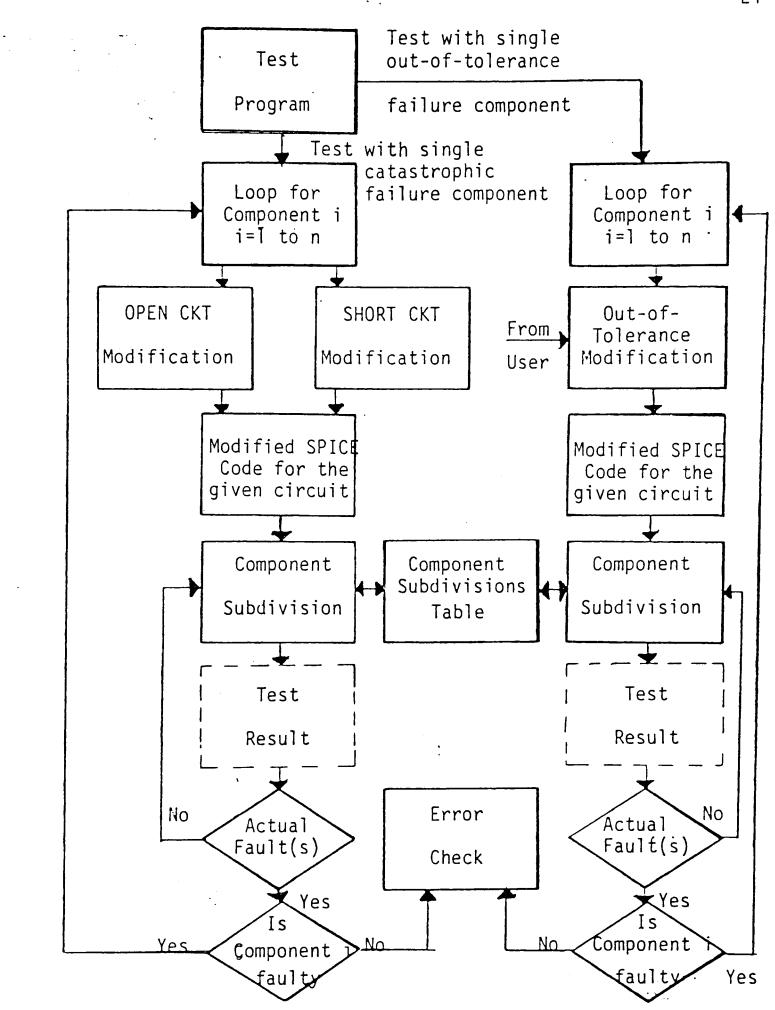

| Figure | 3.4. | Program Validation - Linear Case           | 27 |

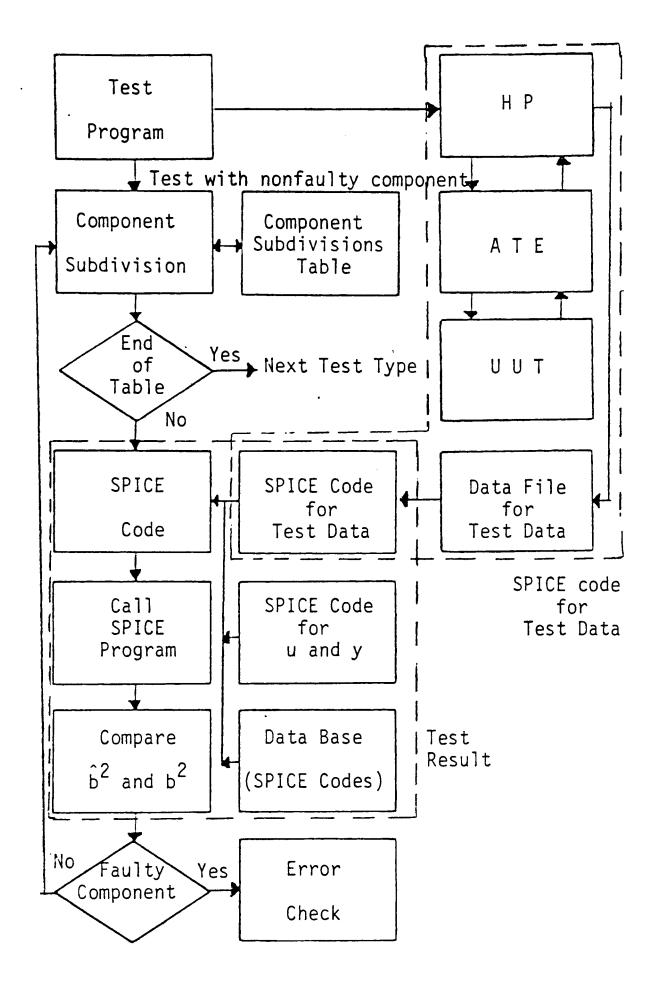

| Figure | 3.5. | On-Line Component - Linear Case            | 29 |

| Figure | 3.6. | Test Program Generation - Nonlinear Case   | 31 |

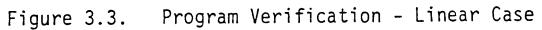

| Figure | 3.7. | Program Verification - Nonlinear Case      | 33 |

| Figure | 3.8. | Program Validation - Nonlinear Case        | 36 |

| Figure | 3.9. | On-Line Component - Nonlinear Case         | 38 |

| Figure | 4.1. | Controlled Sources                         | 47 |

| Figure | 4.2. | Controlled Sources With Component          | 48 |

| Figure | 5.1. | Power Supply Circuit                       | 86 |

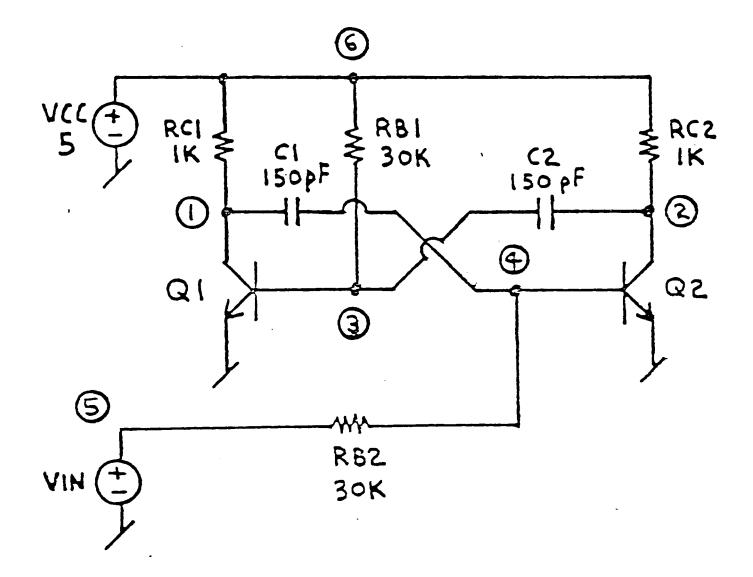

| Figure | 5.2. | Astable Multivibrator                      | 95 |

| Figure | 5.3. | Oscillator                                 | 96 |

| Figure | 5.4. | SPICE codes for ASTABLE and OSC CKTs       | 97 |

V

•••

.

#### CHAPTER 1

## INTRODUCTION

Electronics design has become very sophisticated during the past quarter century. Graphical algorithms have been replaced by CAD (Computer-Aided Design), and features of design implementation can be studied by simulation, rather than requiring extensive breadboarding. Electronics maintenance, however, has changed very little during the same period. In fact, many industries have found that the life cycle maintenance costs for their electronics equipment exceed their capital investment. Consequently, it is becoming apparent that the new maintenance process, like the design process, must be automated.

Several formidable problems are faced in the maintenance of military electronics; the avionics and missiles are becoming far too complex for the typical military technician to maintain; the time required to test systems is becoming excessively large; system designs are changing too fast to keep maintenance documents current. Hence a more economical approach to maintenance is an actual necessity. Therefore, a multipurpose automatic test equipment (ATE) which promises testing at computer speeds, fully automatic operation by low-skill operators, the virtual elimination of maintenance documents, and universal designs adaptable to any test problem through the flexibility of programming, has been investigated by several research groups.

Efforts at producing algorithms for automatic test program generation systems has concentrated mainly on digital circuits for which satisfactory solutions have been found. Several digital automatic test

· ]

program generation systems have been developed and widely used by both military and industrial communities. D-LASAR by Digitest, ATVG by General Electric, TGAS by the U. S. Navy, FAS/SDAP by Honeywell, LOGOS by Grumman, GLASH by Micro, SALT by IBM,<sup>12</sup> TESTAID-III by Hewlett-Packard,<sup>36</sup> etc., are some of the well known systems.

Several books<sup>5,6,11,19,27,33</sup> and articles<sup>34,35</sup> have discussed the fault detection and diagnosis in digital circuits. Typically, in the digital circuit, one assumes that all permanent component failures are either "stuck-at-zero," (s-a-0), or "stuck-at-one" (s-a-1).<sup>17</sup> Under this assumption, one hypothesizes some limit on the number of simultaneous faults and then simulates the responses of UUT (Unit Under Test) to a family of test vectors for each allowed combination of faults. The simulated responses are used to set up a fault dictionary which is stored in some bulk storage media such as disks and magnetic tapes. When the test is conducted the actual responses of UUT are compared with the responses in the fault dictionary to locate the failure. Of course, this approach is a kind of "brute force" search which requires one to simulate all possible responses to the various combinations of hypothesized faults. However, all these simulations need only be done once at the factory of a maintenance depot. The cost of simulation is therefore relatively cheap. Clearly, this approach is ideally suited for the maintenance environment. With the aid of some sophisticated software engineering, this apparently "brute force" approach to the fault diagnosis problem has slowly evolved into a workable concept.

program generation systems have been developed and widely used by both military and industrial communities. D-LASAR by Digitest, ATVG by General Electric, TGAS by the U. S. Navy, FAS/SDAP by Honeywell, LOGOS by Grumman, GLASH by Micro, SALT by IBM,<sup>12</sup> TESTAID-III by Hewlett-Packard,<sup>36</sup> etc., are some of the well known systems.

Several books<sup>5,6,11,19,27,33</sup> and articles<sup>34,35</sup> have discussed the fault detection and diagnosis in digital circuits. Typically, in the digital circuit, one assumes that all permanent component failures are either "stuck-at-zero," (s-a-0), or "stuck-at-one" (s-a-1).<sup>17</sup> Under this assumption, one hypothesizes some limit on the number of simultaneous faults and then simulates the responses of UUT (Unit Under Test) to a family of test vectors for each allowed combination of faults. The simulated responses are used to set up a fault dictionary which is stored in some bulk storage media such as disks and magnetic tapes. When the test is conducted the actual responses of UUT are compared with the responses in the fault dictionary to locate the failure. Of course, this approach is a kind of "brute force" search which requires one to simulate all possible responses to the various combinations of hypothesized faults. However, all these simulations need only be done once at the factory of a maintenance depot. The cost of simulation is therefore relatively cheap. Clearly, this approach is ideally suited for the maintenance environment. With the aid of some sophisticated software engineering, this apparently "brute force" approach to the fault diagnosis problem has slowly evolved into a workable concept.

Unfortunately, the above described success in the digital world has not been paralleled by progress in the analog world. The difficulty arises from a number of characteristics of the analog problem which are not encountered in digital circuits, namely,

- Analog systems have a continuum of possible failures. These failures may range from short circuit to open circuit,

- (2) A good component may be "in tolerance" but not nominal,

- (3) Complex feedback structures are encountered,

- (4) Simulation is slow and costly because analog systems are frequently nonlinear,

- (5) Post-fault component characteristics may not be known, and

- (6) A fault in one component may induce an apparent fault in another.

Items (5) and (6) imply that the kind of "brute force" fault simulation algorithm associated with the digital problem will not be applicable to the analog or hybrid case.

A number of academic researchers have proposed a variety of analog fault diagnosis algorithms.<sup>8,28,29</sup> Conceptually, these algorithms can be subdivided into three classes;<sup>31</sup>

- (i) simulation-before test,

- (ii) simulation-after-test with a single test vector, and

- (iii) simulation-after-test with multiple test vectors.

The first is commonly employed in digital testing and is characterized by minimal on-line computational requirements, but the high cost of analog circuit simulation coupled with the large number of potential fault modes limits the applicability of this algorithm. Typically, the simulation-after-test technique attempts to model the analog fault diagnosis problem as a nonlinear equation in which the internal variables or component parameters are computed in terms of the test data. In this case, where sufficiently many test points are available, only a single test vector is required and the problem reduces to the solution of a linear equation.<sup>32,38</sup> Therefore, the on-line computational requirements are moderate. However, the test point requirements grow linearly with circuit complexity. To reduce the test point requirements one may consider using multiple test vectors to increase the number of equations obtained from a given set of test points. However, the on-line computation required to solve these complex sets of nonlinear equations (even for linear systems) is extremely expensive.

Comparing the above three techniques, the simulation-after-test, with single test vector, seems to be the closest to the "ideal" algorithm.<sup>31</sup> The remaining question is how to reduce the number of test points so that this algorithm can be made more applicable. An algorithm based on the simulation-after-test, with single test vector, was presented to reduce the number of test points.<sup>41,42</sup>

## The Self-Testing Algorithm

A bound on the maximum number of simultaneous failures is used to reduce the test point requirements while still retaining the computational simplicity inherent in a single test vector algorithm. It is reasonable to assume that, at most, two or three components have failed simultaneously in a given circuit with several hundred IC's and/or discrete components. In fact, rather than solving a set of simultaneous

equations in n-space, the solution to our fault diagnosis problem actually lies in a two- or three-dimensional submanifold which should yield a considerable reduction in test point requirements. Unfortunately, we do not know which two or three have failed and a further search is still required. Fortunately, with the aid of an appropriate decision algorithm the required search can be implemented quite simply.

Conceptually, the components (individual chips, discrete components or subsystems) are subdivided into two groups at each step of the test algorithm. At each step we assume that one group is composed of good components and we use the known characteristics of these components, together with the test data, to determine whether or not the remaining components are good. In effect the first group of components is testing the second, hence the "self-test" algorithm. Of course, if the testers are actually good, then the resultant test results for the remaining components will be reliable. On the other hand, if any one of the testers is faulty the test data on the remaining components will be unreliable. Consequently, we repeat the process at the next step of the test algorithm with a different subdivision of components.

Of course, the number of components which may be tested at any one step is dependent on the number of test points available, while the number of steps required is determined by the number of components which may be tested at any one step and the bounds on the maximum number of simultaneous failures. Therefore, this procedure yields a natural set of tradeoffs between the number of test points, simultaneous failures and steps required by the algorithm.

## Overview of Automatic Testing Programming

The Purpose of this overview is to introduce the Automatic Test Equipment (ATE) which provides test data to our test program. A collection of papers relating to hardware, software, and management aspects of automatic test equipment was edited by Liguori.<sup>20</sup> In Knowles' book<sup>18</sup> he introduced the automatic test systems and its applications. He gave a review of the elements which comprise automatic test systems, a survey of those factors which affect the choice of test systems, and a discussion on the planning studies which should precede any decision to adopt ATE. Another book written by Healy<sup>16</sup> concentrates on the automatic testing of the digital integrated circuits. Several articles published in IEEE Sprectrum also survey the ATE systems.<sup>9,13,24,37</sup>

A test is a process which is not only performed to obtain information about the performance of a component or device, it is also allowed to detect, locate, or identify faults. The electronic component or device which is to be tested is called a unit under test (UUT). Fault detection is a procedure for evidencing the presence of faults in a system, which is performed either during quality control or during maintenance. Fault Location determines the faulty element after detection of a fault. Fault Diagnosis or identification determines the causes of a fault.

There are essentially two purposes for testing: First, to determine whether or not the UUT is bad (functional testing), and then to find out which element is faulty and needs to be repaired (fault isolation). Testing may be performed manually or automatically.<sup>24</sup> Manual testing is usually performed by connecting individual pieces of test equipment, including measurement devices, special-purpose signal generators, power supplies, decade boxes, and a collection of clip leads. The technician must plug in, set up, and connect all of this equipment to the UUT to make the tests he feels are pertinent by the help of some sort of manual or set of instructions.

Automatic testing is a test procedure which is performed with the aid of a computer. There are power supplies, stimuli, measurement devices, and a switching system to allow the equipment to be arranged in desirable configurations. The instruction manual is replaced by a program file which instructs the computer to carry out test instructions in the proper sequence, judge test results, and/or perform calculations. The test results are either written by a line printer or displayed on a CRT terminal.

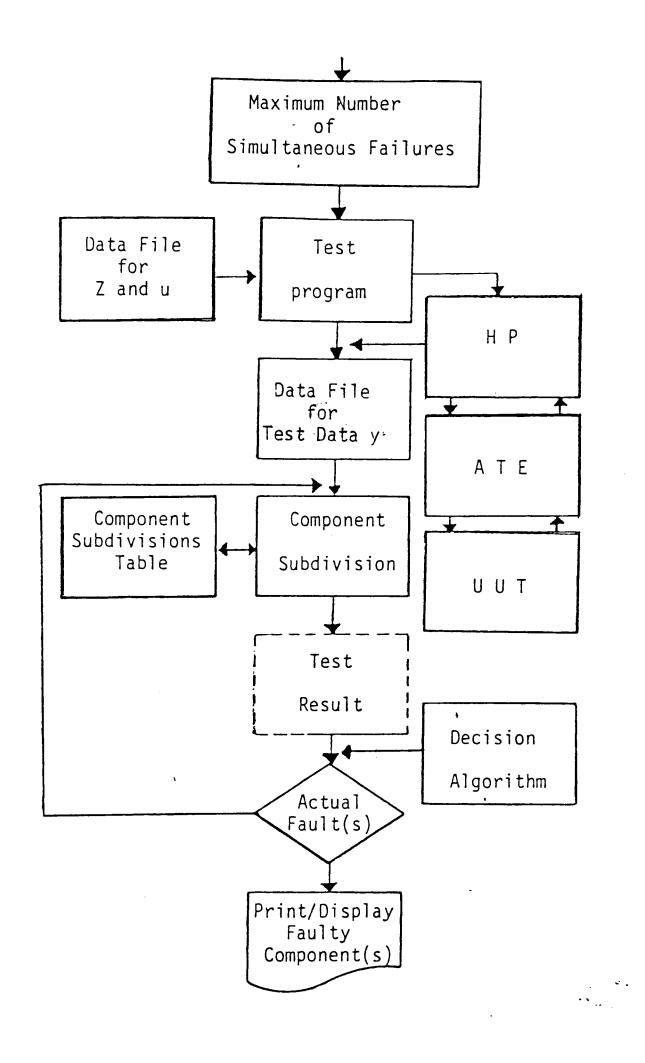

A block diagram of a typical ATE system is shown in Figure 1.1. The switch unit is an equipment which is used to connect the device UUT/ATE interface to the test system and to vary the connections of the device terminals. Examples are multiplexers, relay trees, scanner, and so forth. The stinulus unit is a device which generates stimuli, such as power supplies, oscillators, synthesizes, function generators, waveform generators, and D/A converters, among others. For use in automatic test such sources are often required to be programmable; that is, all of their functions should be controllable by electric signals instead of manual control.<sup>24</sup> The measurement unit is an instrument which quantifies the response of a UUT to stimuli. The response of a UUT may be a

Figure 1.1. Simplified Block Diagram of Typical ATE

directly measurable quantity such as a voltage, or it may be a derived quantity from physical measurements such as a resistance. Therefore, these units include voltmeters, current meters, phase meters, impedance bridges, frequency counters, A/D converters, etc. UUT/ATE interface provides the connection of the UUT to the ATE which has the incompatible connecting points. Usually, an adapter is used to define items that interface the UUT to the switch unit. It may be test boards, fixtures, or sockets that contact the leads or terminals of a component. Output unit is a device which is used to display the test results. It may be a CRT terminal or line printer, or may transfer this test data to the host computer which provides a fault diagnosis.

The testing starts after connecting the UUT to the test equipment through an interface. The computer output, a synthesis of an electrical signal, is converted by means of a digital-to-analog (D/A) converter into voltage or current levels. These signals are applied to the UUT via a switching unit and interfaces. The test results are routed via the switching unit to a sampling instrument. The measured quantity is converted to digital representation, and this time series is analyzed by the computer. The computer output of the results can be presented in any form most suitable to the users' display or print-out requirements.

#### Organization

The purpose of this dissertation is to present an Analog Automatic Test Program Generation, AATPG, for both linear and nonlinear circuits based on the self-testing algorithm. In Chapter 2 a Component Connection

Model, CCM, is described. This model is used to formulate our test algorithm for both linear and nonlinear circuits. The simulation model is used to test one set of components under the assumption that the remaining components are good. Based on this model the software development of AATPGs for both linear and nonlinear circuits are discussed in Chapter 3. Each code is subdivided into off-line and on-line components. The off-line component is used by the test system designer to input nominal system specification to generate the test program and data base which is used by an on-line component. To verify the software's ability to locate and detect the faulty component(s), Program Verification is Similarly, the test program is validated by the measurement of the used. actual UUT. The on-line component is used in the implementation of the actual test. In order to run the actual test in a fully automatic mode, several supporting algorithms and decision algorithms are discussed in Examples for both linear and nonlinear circuits are present-Chapter 4. ed in Chapter 5. The conclusions follow in Chapter 6.

#### CHAPTER 2

#### THE SIMULATION MODEL

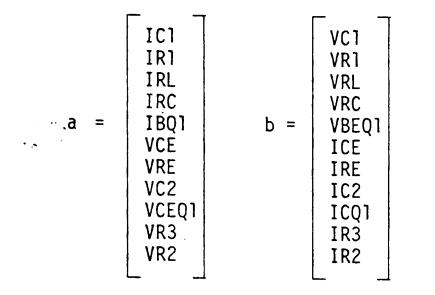

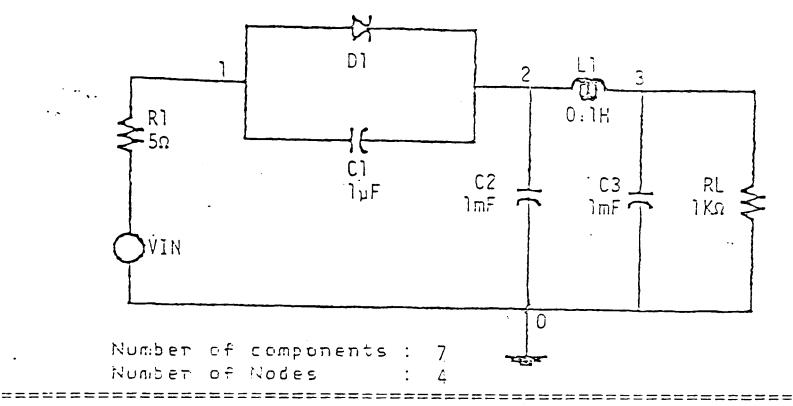

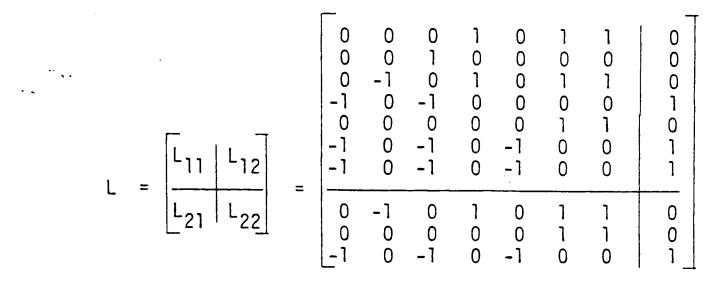

Although our test algorithm can be formulated in terms of any of the standard circuit or system models, for the purpose of this exposition we will assume a component connection for the circuit or system under test.<sup>7</sup> The component connection model naturally divides the system into two sets of equations: Component equations characterized by (block) composite component model (for linear case) or by decoupled state model (for nonlinear case), and the Connection equations characterized by coupled linear algebraic equations. Equations (2.1) and (2.20) are the component equations of linear and nonlinear systems, respectively, while the equations (2.2) and (2.3) are the connection equations. The connection matrix L, equations (2.2) and (2.3), characterizes the connection of components in the system. At each step of the algorithm, a "pseudo circuit" is generated and formulated by the equations (2.9) through (2.15) with a new connection matrix K. The data base which is used by the on-line component is computed by equation (2.16), matrix M for linear case while a SPICE code, based on the equations (2.23) through (2.26), is generated for the nonlinear case.

### Linear Case

In the linear case the UUT is represented by a composite component model characterizing its components and/or subsystems together with an algebraic connection equation as follows:

b = Za (2.1)

and

$$b^2 = Z^2 a^2$$

(2.5)

Here,  $Z^1$ ,  $a^1$  and  $b^1$  are the vectors of group "1" transfer functions, component input and output variables; and similarly for  $Z^2$ ,  $a^2$  and  $b^2$ . To retain notational compatibility with equations (2.4) and (2.5) we reorder and partition the connection equations of (2.2) and (2.3) to be conformable with (2.4) and (2.5) as follows:

$$a^{1} = L_{11}^{11} b^{1} + L_{11}^{12} b^{2} + L_{12}^{1} u$$

(2.6)

$$a^{2} = L^{21} b^{1} + L^{22} b^{2} + L^{2} u$$

(2.7)

$$y = L_{21}^{1} b^{1} + L_{21}^{2} b^{2} + L_{22} u$$

(2.8)

Unlike the commonly encountered circuit analysis problem, in which one desires to simulate the output responses y of a given circuit, in our application the vector y is obtained by the test engineer measuring the responses at various test points. The test responses y are, therefore, known for the purpose of our application. Given equations (2.4) through (2.8), our goal is to compute the group "2" component variables,  $a^2$  and  $b^2$ . To this end we assume that  $L_{21}^2$  admits a left inverse, which, in turn, determines the allowable component subdivisions. Under this assumption one may then formulate a component connection model for . a "pseudo circuit" composed of the group "1" components with external input vector  $u^p = col(u,y)$  and external vector  $y^p = col(a^2,b^2)$  in the form,

$$b^{\dagger} = Z^{\dagger} a^{\dagger}$$

(2.9)

and

$$a^{1} = K_{11} b^{1} + K_{12} u^{p}$$

(2.10)

$$y^{p} = K_{21} b^{1} + K_{22} u^{p}$$

(2.11)

where K is the connection matrix of the pseudo circuit. Some algebraic manipulation of equations (2.6) through (2.8), together with the assumption that  $[L_{21}^2]^{-L}$  exists, will yield

$$K_{11} = [L_{11}^{11} - L_{11}^{12} [L_{21}^{2}]^{-L} L_{21}^{1}]$$

(2.12)

$$K_{12} = [L_{12}^{1} - L_{11}^{12} [L_{21}^{2}]^{-L} L_{22} | L_{11}^{12} [L_{21}^{2'}]^{-L}]$$

(2.13)

$$K_{21} = \begin{bmatrix} L_{11}^{21} - L_{11}^{22} [L_{21}^{2}]^{-L} L_{21}^{1} \\ - [L_{21}^{2}]^{-L} L_{21}^{1} \end{bmatrix}$$

(2.14)

$$K_{22} = \begin{bmatrix} L_{12}^2 - L_{11}^{22} & [L_{21}^2]^{-L} \\ - [L_{21}^$$

For each pseudo circuit, substituting equation (2.9) into equations (2.10) and (2.11), the equations with the transfer function matrix M are shown as follows:

$$a^{1} = (K_{11} Z^{1}) b^{1} + K_{12} u^{p}$$

$y^{p} = (K_{21} Z^{1}) b^{1} + K_{22} u^{p}$

and

$y^p = M u^p$

where

$$M = K_{21} Z^{1} (I - K_{11} Z^{1})^{-1} K_{12} + K_{22} . \qquad (2.16)$$

Specifically,

$$a^2 = M_{11} u + M_{12} y$$

(2.17)

$$b^2 = M_{21} u + M_{22} y$$

(2.18)

Since the matrix M is independent of the test data and computed in terms of the nominal values of the group "1" components, it may be computed off-line and stored in a data base to be retrieved at the time a test is conducted. Furthermore, since only a single test vector is required, single frequency testing can be employed. In this case M need only be computed at a single frequency. The only on-line computation required for the fault diagnosis of a linear system is the matrix/vector multiplication indicated by equations (2.17) and (2.18) together with the computation of

$$\hat{b}^2 = Z^2 a^2$$

(2.19)

to determine which, if any, of the group "2" components are bad.

# Nonlinear Case

For the nonlinear case one may formulate an identical algorithm in which the component characteristics are represented by a set of decoupled state models, together with an algebraic equation as follows:

$$x_{i} = f_{i}(x_{i}, a_{i}) b_{i} = g_{i}(x_{i}, a_{i}) ; x_{i}(0) = 0 ; i = 1,2,..n$$

(2.20)

and

$$a = L_{11} b + L_{12} u$$

(2.2)

$$y = L_{21} b + L_{22} u$$

(2.3)

Here,  $x_i$ 's are the component state variables. The component equation (2.20) is modeled in the time domain.

Similarly, as in the linear case, the components are subdivided into two groups. The variables in (2.20) are then partitioned as

$$\dot{x}^{1} = f^{1}(x^{1}, a^{1})$$

;  $x^{1}(0) = 0$  (2.21)

$b^{1} = g^{1}(x^{1}, a^{1})$

and

$$\dot{x}^{2} = f^{2}(x^{2}, a^{2}) ; x^{2}(0) = 0$$

$$b^{2} = g^{2}(x^{2}, a^{2})$$

(2.22)

The connection equations (2.2) and (2.3) are partitioned as the equations (2.5) through (2.7).

For each component subdivision, a pseudo circuit is generated in the form,

$$\dot{x}^{1} = f^{1}(x^{1}, a^{1})$$

;  $x^{1}(0) = 0$  (2.23)

$b^{1} = g^{1}(x^{1}, a^{1})$

$$a^{1} = K_{11} b^{1} + K_{12} u^{p}$$

(2.24)

$$y^{p} = K_{21} b^{1} + K_{22} u^{p}$$

(2.25)

where the connection matrix K of the pseudo circuit is derived in the equations (2.12) through (2.15). Since in our test algorithm both u and y are known, the above equations can be solved via any standard circuit analysis code, SPICE,  $^{25}$  NAP2,  $^{26}$  etc., to compute  $y^{p} = Col(a^{2},b^{2})$ . Once the values  $a^{2}$  and  $b^{2}$  are computed, with the computation of

$$\dot{x}^2 = f^2(x^2, a^2)$$

;  $x^2(0) = 0$  (2.26)

$\dot{b}^2 = g^2(x^2, a^2)$

to determine which, if any, of the groups two components are faulty.

However, the above test results are dependent on our assumption that the group "1" components are not faulty, they are not immediately applicable. A decision algorithm is required to cope with this ambiguity problem so that the actual fault(s) can be precisely identified. Following the philosophy initiated by Preparata, Metze, and Chein<sup>2,14,30</sup> in their study of self-testing computer networks, if one assumes a bound on the maximum number of components, it is possible to determine the actual fault(s) from an analysis of the test results obtained at the various steps of the algorithm. To this end we have derived the complete theory required to locate a single fault, together with Boolean algebraic and heuristic methods, which is applicable to the multiple fault case. <sup>39,40,42</sup>

#### CHAPTER 3

## SOFTWARE DEVELOPMENT

The AATPG code for both linear and nonlinear circuits is subdivided into off-line and on-line components. The former, corresponding to the test system design stage, is used by test system designer to input nominal system specifications to generate a data base which is used by the on-line component. To implement the actual test, the field engineer invokes the on-line component input data describing the UUT: the assumed maximum number of simultaneous failures, the type of decision algorithm to be employed, and the source of the test data. The actual test can then be run in a fully automatic mode or interactively.

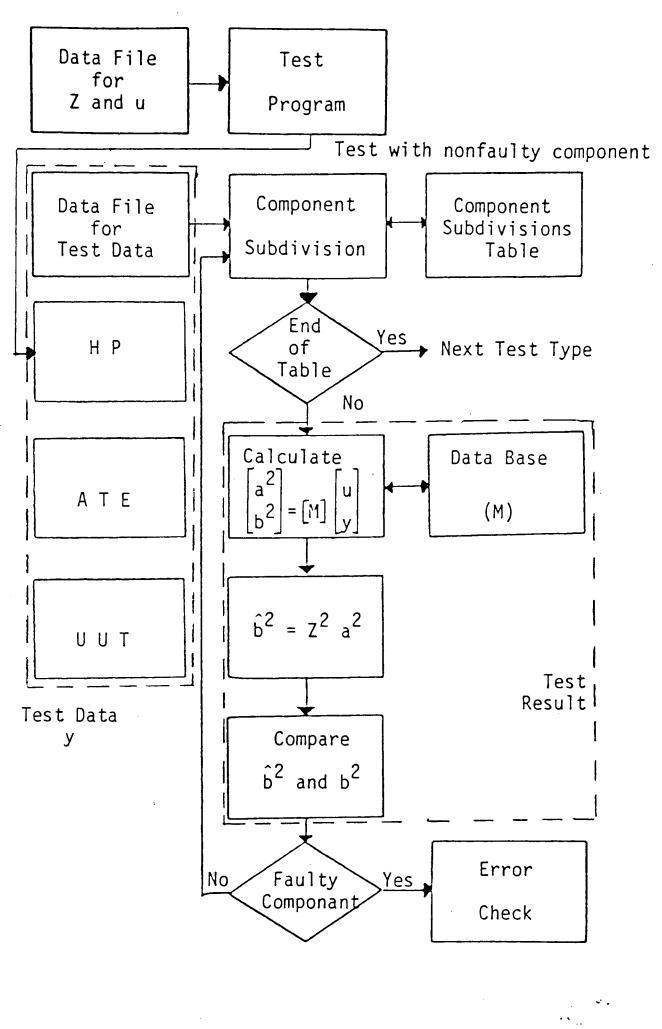

As illustrated in Figure 3.1, a circuit description and test objectives are given to the off-line component to generate the test program. Necessary changes are indicated if the resultant test does not satisfy all of the requirements. If the design is satisfactory, the off-line component will generate the necessary data for the on-line test program and the data base. In the test package, the greatest part of the required computation is carried out by the off-line component with the "pseudo-internal test data" being obtained from the test measurements via a simple on-line matrix/vector multiplication of equations (2.17) and (2.18). To the contrary, in the nonlinear code SPICE is used to evaluate the "pseudo-internal test data" via the on-line simulation of an appropriate pseudo circuit.

In our implementation, to use the actual measured test data with these AATPGs, a HP 9825A is used to control special purpose ATE

Figure 3.1. Design and Test of a Unit Under Test (UUT)

(Automatic Test Equipment) which generates test signals, and stores the measured test results. After some necessary calculations, the data is transferred to the host (VAX 11/780) where the on-line component of the ATPG takes over.

Both the off-line and on-line components have user-oriented interfaces to simplify the process of generating a new test program. The AATPG has been implemented on a VAX 11/780 in FORTRAN 77 and DCL (Dec Command Language).<sup>39,40</sup> In the linear code the user specifies the circuit in terms of certain standard elements, while in the nonlinear code standard SPICE circuit models are employed. The input syntax is a free-format style.

# Linear Case 👘

Off-line Component: Design Stage

The objective of the off-line component is to generate the test program and the appropriate data for the test program, verify and validate the test program so that the faulty components can be actually detected and located.

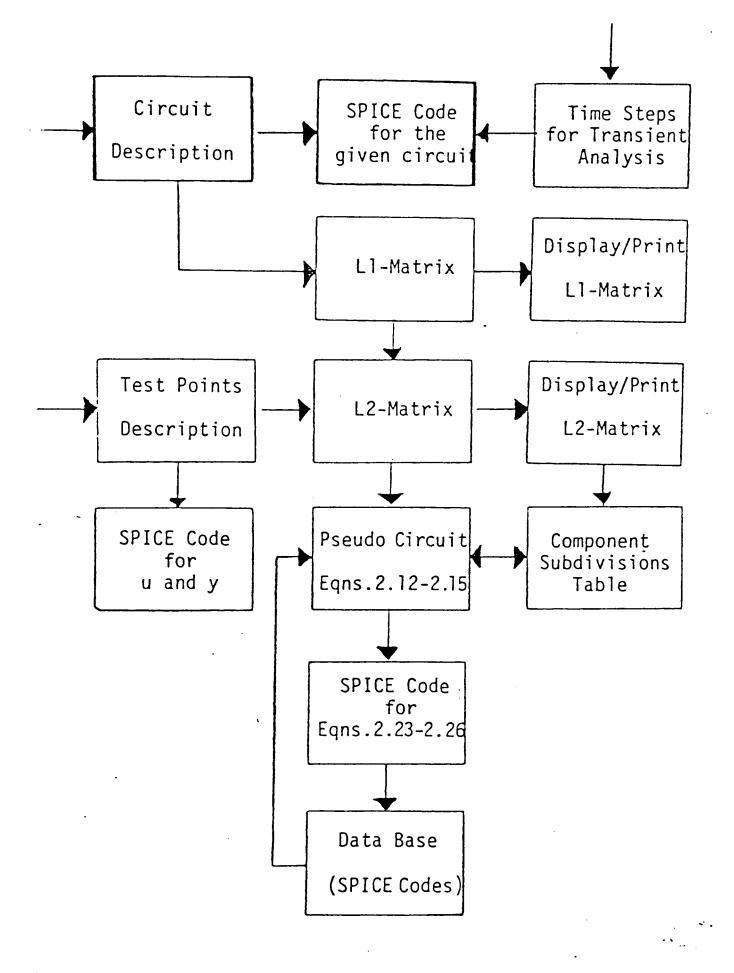

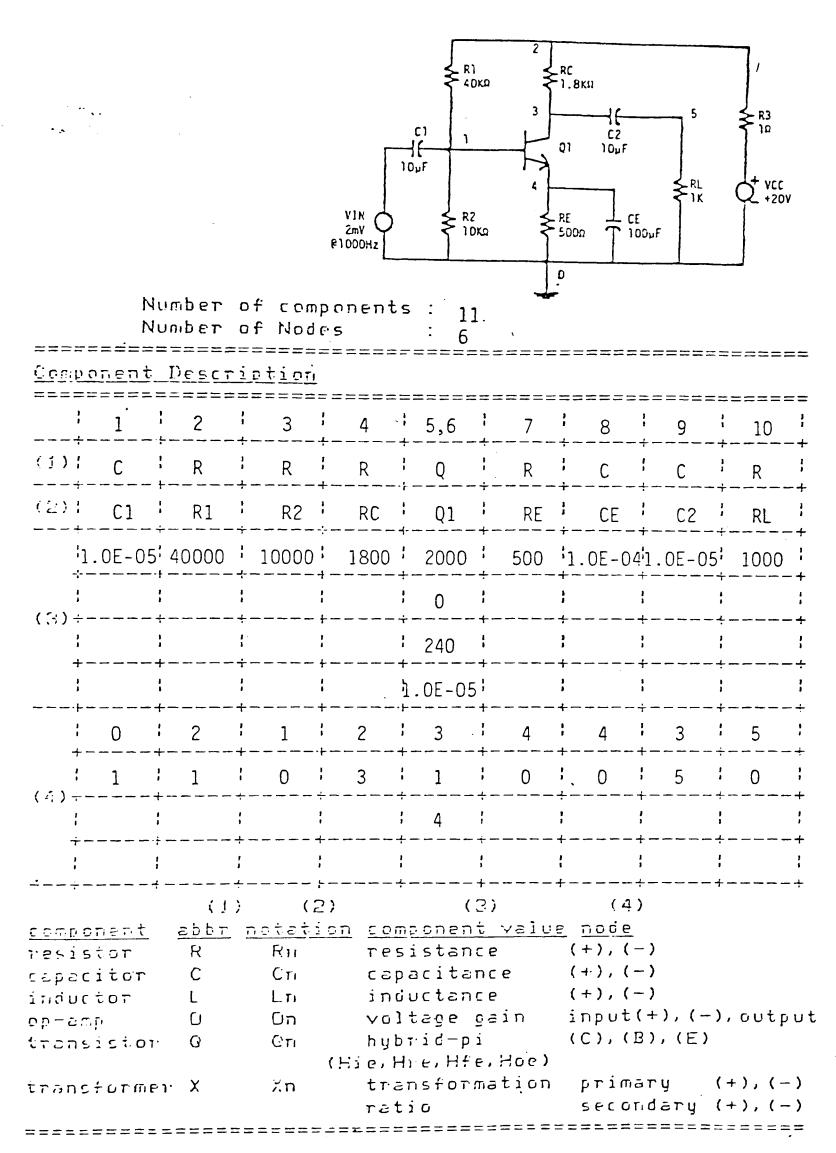

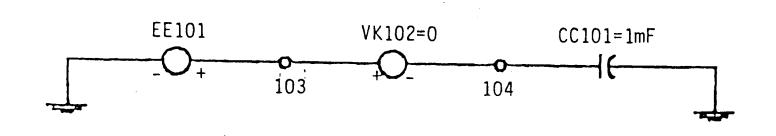

<u>Test Program Generation</u>: As illustrated in Figure 3.2, the input requirements in the test program generation are Circuit Description, Input Frequency, and Accessible Test Terminals.

<u>Circuit Description</u>: The Component Connection Model is used to simulate the UUT under nominal and faulty conditions. In the case of a linear circuit, the UUT components are characterized by a composite component model and the component equations are modeled in frequency domain. The circuit description consists of two steps, namely:

÷.

••

- (1) Component Description,

- (2) Source Description.

In the former, the user is required to input the component type (the component types currently available in this package are resistors, inductors, capacitors, transistors, op-amps, and transformers), give a unique name to each component (where the first letter identifies the component type), define the value of the appropriate elements by the input of a numerical constant, and indicate the current flow direction by specifying the nodes. Nodes must be nonnegative integers, but need not be numbered sequentially. The ground node must be numbered zero. In the source description, the independent sources are assumed to be located in series/parallel with a component, therefore, the branch which contains the source will be specified as well as the orientation of this branch.

<u>Input Frequency</u>: The component equations for our linear circuits are modeled in the frequency domain. Since a single test vector is required, single frequency testing can be employed. With this single frequency, the component transfer matrix Z is generated by computing the impedance or admittance for each one port component, such as a resistor, capacitor, or inductor. The square matrix Z contains all zeros everywhere except the diagonal blocks (where the block size depends on the number of ports of each component). For the two-port components, such as transistor, the hybrid pi parameters are used to characterize the component, and the dimension of the diagonal block is two rows by two columns with the h-parameters or the transformed parameters depending upon the entries selected in the vector a. Together with the data generated in the above description, the first part of the connection is generated as shown in equation (2.2).

<u>Accessible Test Terminals</u>: The accessible Test Terminals are used to generate the second part of the connection matrix. In our test package the user is required to input manually the test point locations where the test points may be current measurements through components or voltage measurements across any two nodes. However, the test points may not be an entry of the vector a. With the assumption that the matrix  $[L_{21}^2]^{-L}$  exists, a component subdivisions table is generated, where the elements in each subdivision are the group "2" components. As discussed in the previous section, given a subdivision, a "pseudo circuit" with the connection matrix K is created by computing equations (2.12) through (2.15), and the data base, M-matrix, is derived by using equation (2.16).

At the end of the test program generation process, the following data files are created; the connection matrix L, the component transfer matrix Z and the external input vector u, the component subdivisions table, the data base (M-matrix), and the test program.

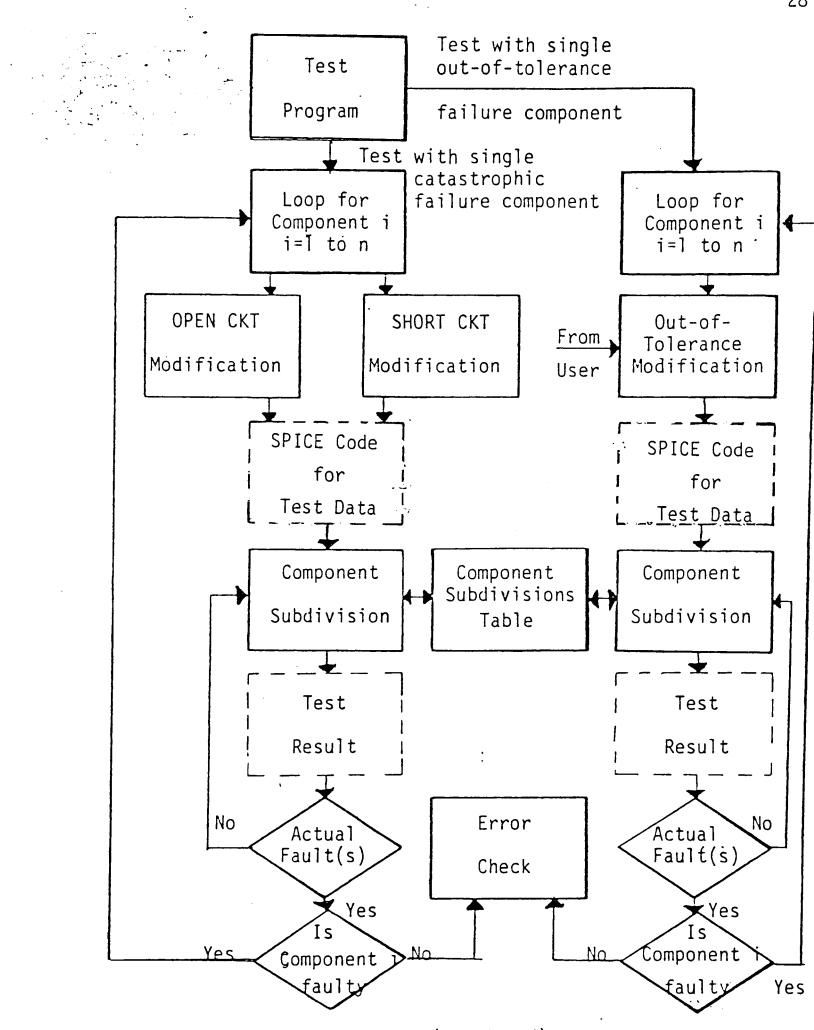

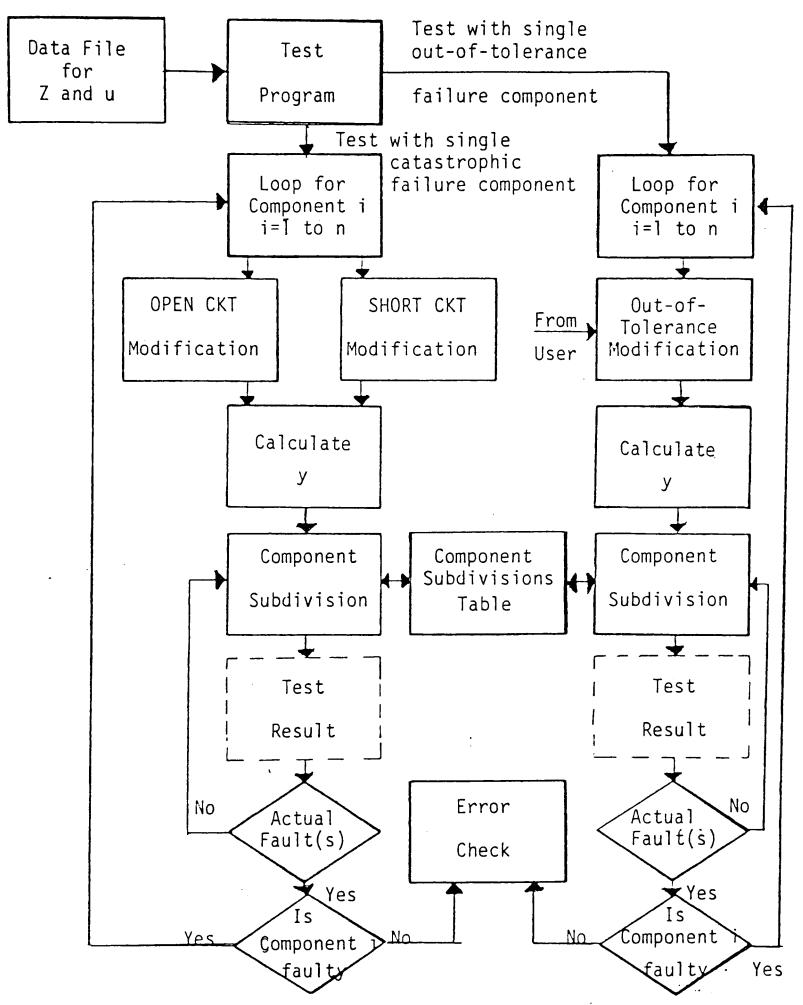

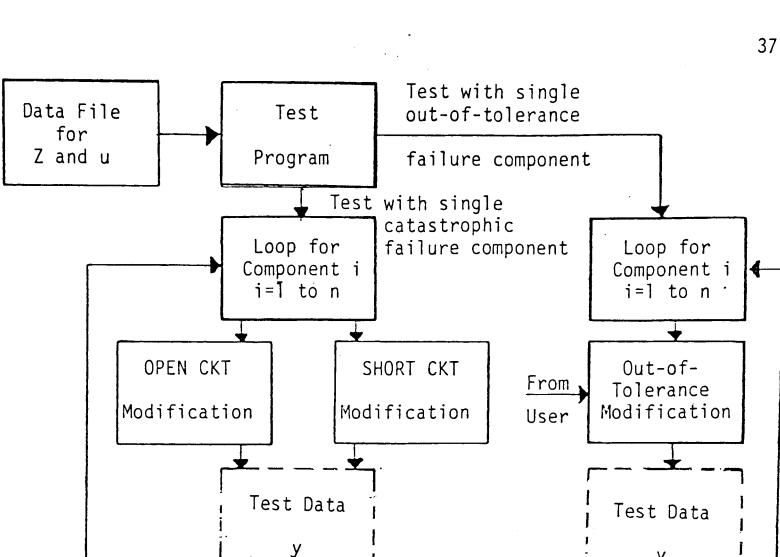

<u>Program Verification</u>: The generated test program is tested in software, as shown in Figure 3.3, to verify its ability to detect and locate faults. To verify the test program, three tests are performed on each circuit, namely:

Figure 3.3. (Continued)

(1) A test with nonfaulty components,

(2) Tests with single catastrophic (open and short circuits) failures, and

(3) Tests with a single out-of-tolerance failure.

The first test verifies the correctness of the test program, while the remaining tests are performed to check whether or not the selected test points can actually locate and detect the faults. If the test is not satisfactory, the design engineer may change the test points and repeat the process of program generation. The source of test data for program verification is a simulation program in which the test data, y, is calculated by the following equation.

$$y = [L_{21} Z (I - L_{11} Z)^{-1} L_{12} + L_{22}] u_{\pm}^{-1}$$

(3.1)

· ----

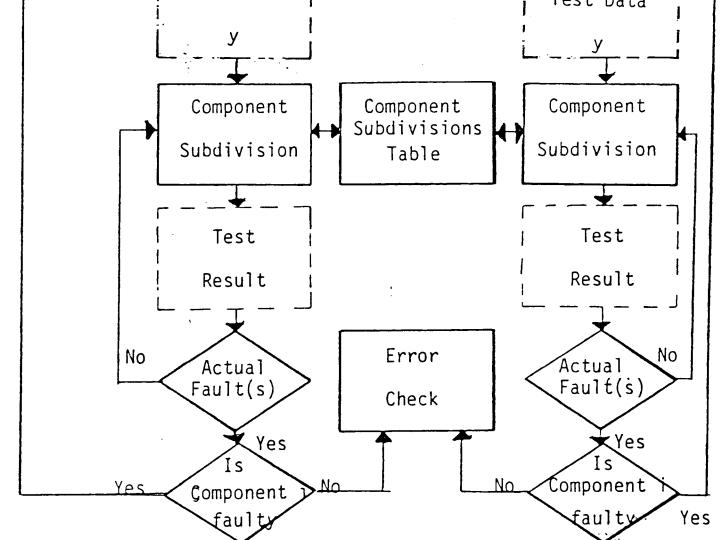

In the first test, since no faulty component is assumed, all the group "1" components are good so that the test results should be reliable. If one of the test results is found to be bad in an arbitrary subdivision, which contradicts our nonfaulty component assumption, the process will be terminated with an error message. An error check routine is then loaded to check for correctness of the Circuit and Test Point Descriptions. If no error is detected, the program generation process is repeated with new test points. If no faulty component is detected in all possible subdivisions, the catastrophic failure test will be executed. In this test, components, taken one at a time, are modeled as open circuits. Using the calculated y of equation (3.1), the test results are obtained, and the actual faulty component will be located by the exact single fault algorithm. The details of the decision algorithms will be discussed later.

After the test with the open circuits for each component is executed successfully, a similar test where the components are short circuited is performed. If either one of the above tests fails the error check routine will be loaded. If all the above tests are processed successfully, similar tests for out-of-tolerance failures are executed. Once all tests are completed successfully, the test program is assumed correct.

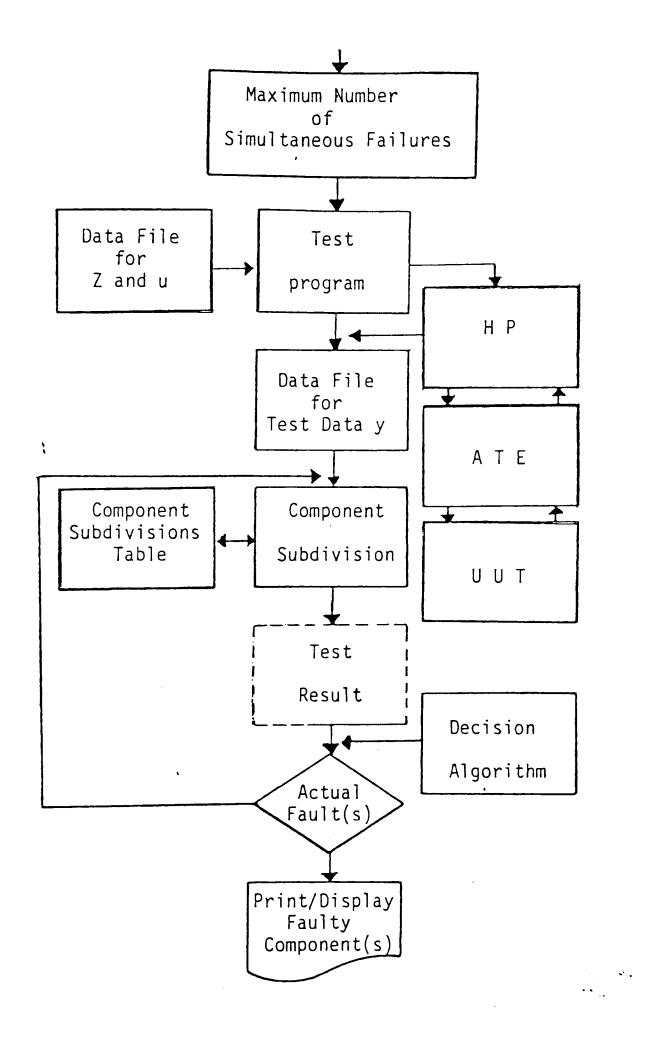

Following the successful test program verification, the test program is validated by the measurement of the actual UUT, as shown in Figure 3.4. On-line Component: Test Stage

The implementation of the actual test on a UUT is as illustrated in Figure 3.5. The maximum number of simultaneous failures allowed is specified by the user; the data files (matrix Z and vector u) and the test program are loaded and the host computer will send an instruction to the HP 9825A controller to conduct the test measurement. After the ATE is instructed to generate stimuli for the UUT, the measured test data will be stored and transferred to the host computer. When the data transfer is completed, the test program will compute the test result and identify the faulty component(s) with the aid of the decision algorithm.

### Nonlinear Case

# Off-line Component: Design Stage

In the nonlinear case, the objective of the off-line component is to generate the test program, test data for test program use, and SPICE codes. These SPICE codes are generated for the given circuit, test inputs u and test data y, and pseudo circuits with equations (2.23) through

۰.

Figure 3.4. Program Validation - Linear Case

(Continued) Figure 3.4.

.

Figure 3.5. On-Line Component - Linear Case

(2.26). Similar ways to verify and validate the test program in the linear case are also employed here.

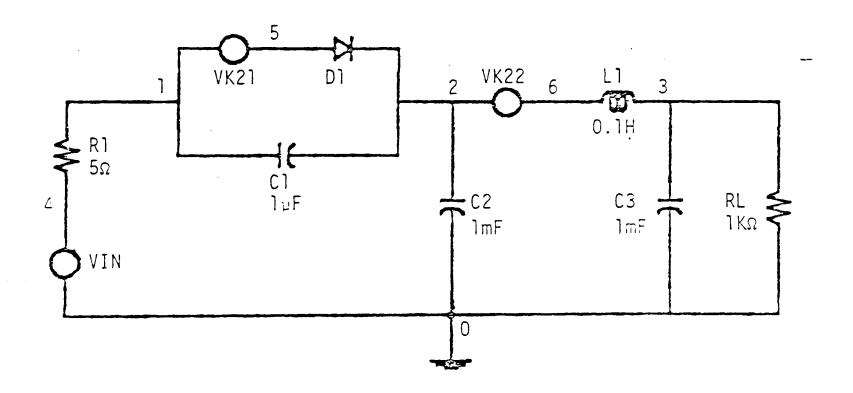

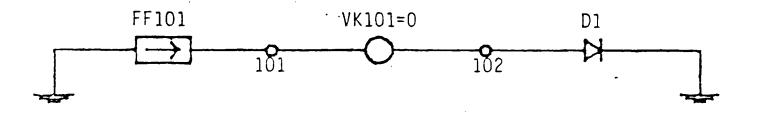

As illustrated in Figure 3.6, the input requirements in the test program generation are Circuit Description, Time Steps for Transient Analysis, and Accessible Test Terminals.

Circuit Description: In the SPICE program, each component in the circuit is specified by a component card that contains the component name, the circuit nodes to which the component is connected, and the values of the parameters that determine the electrical characteristics of the component. The first letter of the component name specifies the component type. Nodes must be nonnegative integers but need not be numbered sequentially. The ground node must be numbered zero. To describe the circuit analysis to SPICE, which is the same as the component description discussed in the linear case, the user is required to input the component type (any SPICE accepted component type) with a unique name, define the component value by any number field accepted by SPICE, and specify the nodes. For the semiconductor components, such as diodes, BJTs, JFETs, and MOSFETs, user needs to specify only the pertinent model parameter values. The model for the BJT is based on the integral charge model of Gummel and Poon; however, if Gummel-Poon parameters are not specified, the model reduces to the simpler Ebers-Moll model. In either case, charge storage effects, ohmic resistances, and a currentdependent output conductance may be included. The diode model can be used for either junction diodes or schottky barrier diodes. The JFET model is based on the FET model of Shichman and Hodges. The model for

Figure 3.6. Test Program Generation - Nonlinear Case

MOSFET is based on the Frohman-Grove model; however, channel-length modulation, subthreshold condition, and some short-channel effects are included.<sup>25</sup> In the source description, any independent source in SPICE can be assigned a time-dependent value for transient analysis, and the source value can be a constant or independent source function (Pulse, Exponential, Sinusoidal, or Piecewise Linear). Therefore, the user may input the source value by a constant, or any above function.

<u>Time Steps for Transient Analysis</u>: The transient analysis portion of SPICE computes the transient output variables as a function of time over a user-specified time interval.

Accessible Test Terminals: When the accessible test terminals are specified, the L2-matrix, a table consisting of all possible component subdivisions, and a SPICE code for the test inputs u and test data y are generated. As discussed in the linear case, the connection matrix K of a pseudo circuit is created by computing the equations (2.12) through (2.15). For each subdivision, based on this generated K-matrix and equations (2.23) through (2.26), a SPICE code is generated and stored in a data base which will be used by the on-line component.

At the end of the program generation process, the following data files are generated: SPICE code for the given circuit, SPICE code for u and y, and data base (SPICE codes for the equations (2.23) through (2.26)).

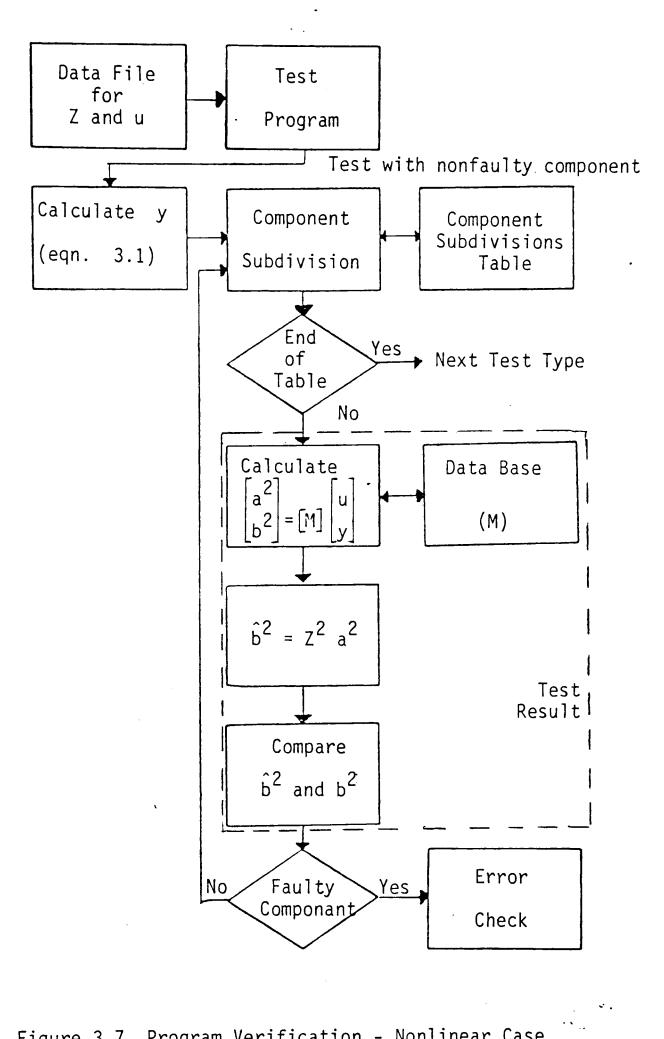

<u>Program Verification</u>: In the linear case, three tests are used to verify the software's ability to locate the faulty component. Instead of using the test data y by computing equation (3.1) in the linear case, here, as indicated in Figure 3.7, we will modify the SPICE code for the

Figure 3.7. Program Verification - Nonlinear Case

Figure 3.7. (Continued)

given circuit by assigning a simulated faulty value. Concatenating this code, the code for u and y, and the code for any subdivision, as an input file of the SPICE program, the output file stores the values of  $b^2$  and  $\hat{b}^2$ . The test results are then obtained by comparing these two values.

Following the successful test program verification, the test program is validated as shown in Figure 3.8, by measurement of the actual UUT.

On-line Component: Test Stage

To implement the actual test on a UUT, as illustrated in Figure 3.9, the user inputs the maximum number of simultaneous failures allowed. The host computer loads the test program and sends instructions to command the HP 9825A controller conducting the test measurement. A data file is created to store the test data which is transferred from controller. A SPICE code for these test data is generated to replace the code for the given circuit when the SPICE program is run for the test results.

Figure 3.8. Program Validation - Nonlinear Case

Figure 3.8. (Continued)

•

Figure 3.9. On-Line Component - Nonlinear Case

•

# CHAPTER 4

# ALGORITHMS

Along with the software developed in the previous chapter, it is desirable that the AATPG be run in a fully automatic mode, or interactively, in order to simplify the process of generating new test programs for both linear and nonlinear circuits. To this cause some supporting algorithms are discussed in the first section. In the second section, three decision algorithms are presented to make the decision for the choice of the component subdivision.

# Supporting Algorithms

As described in the previous section, given a circuit, one can generate a data base by computing the matrix K together with some known parameters. The measured data and the stimuli will be used as the inputs to the test program while a test is conducted, and then a number of online simulations will be carried out. In this section, the following problems with algorithms are discussed:

- The generation of the connection matrix L with the users' inputs,

- (2) The kind of subdivisions to be chosen, under the assumption that  $[L_{21}^2]^{-L}$  exists,

- (3) Based on the above subdivisions, how to set up the data base off-line so that the executing time of the on-line can be minimized, and

- (4) How to decide a "good" component from the computed data.

<u>L-Matrix</u>: This commonly encountered geometric connection model is the linear graph used for electric networks and other bilateral components.<sup>23</sup> The linear graph, like the signal flow graph, is a directed graph composed of vertices and edges. Here each edge represents a single bilateral component or a part thereof. Associated with each edge is a pair of variables,  $V_i$  and  $I_i$ . For an electrical network  $V_i$  depicts the port voltage and  $I_i$  the port current.  $V_i$  is often generically termed an across variable and  $I_i$  a through variable. They are not a priori identified as the component input and output. For most components either may serve as the input with the other taken as the-output. The usual conservation laws constrain the variables  $V_i$  and  $I_i$ . In particular, the Kirchhoff voltage law constrains  $V_i$ , the Kirchhoff currant law constrains  $I_i$ .

Let a graph have a specified tree containing r edges and the complementary co-tree containing (p-r) edges. (Here p is the number of edges in the graph.) The number r always equals "n-l" where n is the number of vertices in the graph.<sup>7</sup> Let  $B_f$  be the fundamental circuit matrix and  $S_f$  be the fundamental cut-set matrix, then

$$B_{f} = [X | I_{p-r}]$$

$$(4.1)$$

$$S_{f} = [I_{p} \mid D]$$

$$(4.2)$$

where, X is a (p-r)xp matrix,  $I_{p-r}$  and  $I_p$  are identity matrices, and D is a px(p-r) matrix. It can be easily verified that

$$X = -D^{t}$$

therefore, the equation (4.1) can be written as

$$B_{f} = [-D^{t} | I_{p-r}]$$

Let I =  $col(I_t, I_c)$  and V =  $col(V_t, V_c)$  be the current and voltage vectors of the circuit respectively, where  $I_t(V_t)$  and  $I_c(V_c)$  are denoted as the currents (voltage) in the tree and co-tree edges, respectively. According to the Kirchhoff's current law and Kirchhoff's voltage law, we obtain the equations

$$0 = S_f I = I_t + D I_c$$

and

$$0 = B_f V = -D^t V_t + V_c$$

therefore

$$\begin{bmatrix} I_{t} \\ V_{c} \end{bmatrix} = \begin{bmatrix} 0 & -D \\ D^{t} & 0 \end{bmatrix} \begin{bmatrix} V_{t} \\ I_{c} \end{bmatrix}$$

(4.4)

To obtain the matrix D, an incidence matrix A can be transformed into the form  $\begin{bmatrix} I & D \\ 0 & 0 \end{bmatrix}$  by using a Gaussian elimination process.

In order to derive the L-matrix, equations (2.2) and (2.3), we will specify a tree in a linear graph modeling the topology of an electric network. Let a =  $col(I_t, V_c)$  and b =  $col(V_t, I_c)$  be our composite component input and output vectors. Inherently, tree edges correspond to components having the impedence models and co-tree edges correspond to components with admittance models. Usually, the choice of a tree depends on the choice of a model for the various components. Assuming that there is no intra-component coupling between component model for the linear circuit becomes

(4.3)

$$\begin{bmatrix} V_{t} \\ I_{c} \end{bmatrix} = \begin{bmatrix} \frac{Z_{t} & 0}{0} \\ 0 & Y_{c} \end{bmatrix} \begin{bmatrix} I_{t} \\ V_{c} \end{bmatrix}$$

(4.5)

where  $Z_t$  and  $Y_c$  are block diagonal matrices, the size of the diagonal block depends on the number of ports of the component. For one-port components: resistors, capacitors, and inductors;  $Z_t$  is the composite component impedance matrix for components identified with tree edges and  $Y_c$  is the composite component admittance matrix for components identified with co-tree edges. For two-port components such as the transistors, a two by two block is used to describe this component, the values are defined by the hybrid-pi parameters or appropriately transferred parameters, depending upon the elements of the transistor model employed.

With the choice of "a" and "b" the connection matrices follow directly from the equation (4.4) taking the form

$$L_{11} = \begin{bmatrix} 0 & -D \\ D^{t} & 0 \end{bmatrix}$$

(4.6)

However, for the network sources, the following assumptions will be made: each voltage source is connected inseries with an element which is not a source, and each current source is connected in parallel with an element which is not a source. Under these assumptions, the matrix  $L_{12}$  will be derived from the location of sources.

Suppose a voltage source E<sub>s</sub> is located in the tree edge i,

$V_{ti} = V'_{ti} + \omega E_s$

• ---

where  $\omega$  is defined as follows:

$$\omega = \begin{cases} 1 & \text{if the orientation of the source} \\ & \text{coincides with that of the edge,} \\ -1 & \text{otherwise.} \end{cases}$$

From the equations (4.3), (4.4), and (4.6) we obtain

$$V_{ck} = \sum_{\substack{j=1 \ j=1}}^{n} L_{ll}^{kj} V_{tj} \quad k = n+1, N+2,.., b$$

=

$$\sum_{\substack{j=1 \ j\neq i}}^{n} L_{ll}^{kj} V_{tj} + L_{ll}^{ki} V_{ti}' + \omega L_{ll}^{ki} E_{s} \qquad (4.7)$$

Hence, the (k,s)-entry of the matrix  $L_{12}$  equals to  $\omega L_{11}^{ki}$ . Similarly, if a current source J<sub>s</sub> is located in the co-tree edge i, the (k,s)-entry of  $L_{12}$  is also  $\omega L_{11}^{ki}$ .

Suppose a voltage source  $E_s$  is located in the co-tree edge i,

$$V_{ci} = V'_{ci} + \omega E_s$$

and

$$V_{ck} = \sum_{j=1}^{n} L_{11}^{kj} V_{tj}$$

$k = n+1, n+2,...b$

which implies

$$V_{ck} = \sum_{j=1}^{n} L_{11}^{kj} V_{tj} - \omega E_{s}$$

(4.8)

therefore, the (k,s)-entry of  $L_{12}$  equals  $-\omega$ . Similarly, the (k,s)-entry of  $L_{12}$  for a current source  $J_s$  located in the tree edge i is also  $-\omega$ .

Since the vector y is the system responses measured at the various test points, the matrices  $L_{21}$  and  $L_{22}$  in the equation (2.3), therefore, depend on the selection of the test points. The test points can be selected to measure the current or voltage of any edge or the voltage across any two nodes. In the former case, i.e., the current flow through k-th co-tree edge or the voltage across the k-th tree edge, the response  $y_{j}$  is then an element of vector a. Therefore, the jth rows of the

matrices  $L_{21}$  and  $L_{22}$  are just the k-th rows of  $L_{11}$  and  $L_{12}$ , respectively. In the latter case the responses  $y_j$  will be written in terms of vectors b and y, and the coefficients form the jth rows of  $L_{11}$  and  $L_{22}$ , respectively.

•

ALGORITHM I: (L-Matrix)

Step 1. Generate the incidence matrix A. Obtain matrix D from matrix A by Gaussian Step 2. elimination process. Generate  $L_{1}$ -matrix from the equation (4.5). Step 3. Let e be the number of voltage sources and Step 4. j be the number of current sources  $L_{12}(*,*) = 0.$ IF e = 0 THEN go to step 6 (no voltage source) Step 5. DO i=1 TO e IF the voltage source is in the tree edge (assume they are k-th edge and jth source) THEN DO m=p-r TO p IF L<sub>ll</sub>(m,k)≠O THEN L<sub>l</sub>2(m,j)=ω\*L<sub>ll</sub>(m,k) End of loop ELSE (in the co-tree edge) L<sub>l</sub>2(k,j)= -ω End If End of Loop IF j = o THEN go to step 7 (no current source) Step 6. DO i=1 TO j IF the current source is in the tree edge THEN DO m=1 TO r IF Ljj(m,k)≠0 THEN Lj2(m,j)=ω\*Ljj(m,k) End of loop ELSE  $L_{12}(k,j) = -\omega$ End If End of Loop (Generate matrices L21 and L22) Step 7. (assume the number of test points is m) DO i=1 TO m (assume y<sub>i</sub> is the i-th system response) IF  $y_i$  is selected from the entry of "a" (let it be the k-th entry of vector "a") THEN  $L_{21}(i,*)=L_{11}(k,*)$  and  $L_{22}(i,*)=L_{12}(k,*)$

•

|   | ELSE (y; is specified by user)                    |

|---|---------------------------------------------------|

|   | (let P(t) be the specified value corresponding to |

|   | the nonzero column t)                             |

|   | L2 (i,t)=P(t) for all nonzero t                   |

|   | End If                                            |

| s | End of Loop                                       |

۰.

<u>Component Subdivisions Table</u>: The component subdivisions table is derived from the allowable component subdivisions which satisfy the assumption that  $[L_{21}^2]^{-L}$  exists. Consider an n components circuit with m test points. The  $L_{21}$  matrix is then a m by n matrix. For the software implementation, m x m matrices are constructed by selecting all possible combinations of m columns from the n columns in the matrix  $L_{21}$ , and checking whether or not the matrices are invertible. The subdivisions are recorded into the following table if and only if the matrices are invertible.

| Subdivision<br>number | Group l<br>Component | Group 2<br>Component | Group m<br>Component |  |  |

|-----------------------|----------------------|----------------------|----------------------|--|--|

| (1)                   | *                    | *                    | *                    |  |  |

| (2)                   | *                    | *                    | *                    |  |  |

| :                     | •                    | • • • •              | •                    |  |  |

| :                     | •                    | • • • •              | •                    |  |  |

| (C)                   | *                    | *                    | *                    |  |  |

ALGORITHM II: (Component Subdivisions Table)

Step 1. (Matrix L21 is an m by b matrix)

pick any m columns of matrix L21 to form a matrix

Step 2. IF matrix is invertible

THEN

record the number of these m's column.

ELSE

pick next m columns to form a matrix.

Step 3. Repeat 2 until all combinations have been chosen.

<u>Data Base</u>: Given any component subdivision, a pseudo circuit with connection matrix K is created by computing the equations (2.12) through

(2.15). The data base for the linear case is generated by computing matrix M, equation (2.16), and stored in the data files.

In the nonlinear case, the data base is SPICE codes for equations (2.23) through (2.26). The SPICE code is generated as follows:

Consider the equations (2.23) through (2.26),

$$\dot{x}^{1} = f^{1}(x^{1},a^{1})$$

$$b^{1} = g^{1}(x^{1}, a^{1})$$

;  $x^{1}(0) = 0$  (2.23)

$$a^{1} = K_{11} b^{1} + K_{12} u^{p}$$

(2.24)

$$y^{p} = K_{21} b^{1} + K_{22} u^{p}$$

(2.25)

$$\dot{x}^2 = f^2 (x^2, a^2)$$

;  $x^2(0) = 0$  (2.26)

$\dot{b}^2 = g^2 (x^2, a^2)$

where  $u^{p} = col(u,y)$  and  $y^{p} = col(a^{2},b^{2})$ . Our goal is to compute the values of  $b^{2}$  and  $\hat{b}^{2}$  from the above equations. Solving the values  $b^{1}$  from equations (2.23) and (2.24), plugging  $b^{1}$  into equation (2.25) for  $y^{p}$ , i.e.,  $a^{2}$  and  $b^{2}$ , and substituting the values  $a^{2}$  into (2.26) to solve  $\hat{b}^{2}$ .

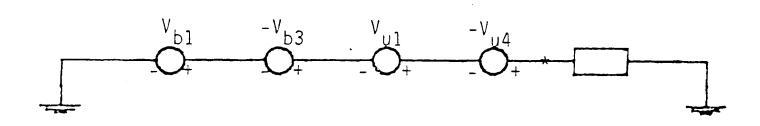

Mathematically, the equation (2.24) shows that the element  $a_i$ , i-th element of  $a^1$ , is the sum of the products of the i-th row of  $K_{11}$  and  $b^1$ , and the products of the i-th row of  $K_{12}$  and  $u^p$ . Physically, suppose that  $a_i$  is a one-port component, if the element  $a_i$  is a voltage measurement, the  $b_i$  is then a current measurement. Therefore, the voltage  $a_i$  is the sum of the measured voltages of  $b^1$  and  $u^p$  where the corresponding terms of the i-th rows of  $K_{11}$  and  $K_{12}$  are not zero. For example, if

$$b^{1} = col [V_{b1}, I_{b2}, V_{b3}, I_{b4}, V_{b5}]$$

$u^{p} = col [V_{u1}, V_{u2}, I_{u3}, V_{u4}],$

i-th row of  $K_{11} = [1, 0, -1, 0, 0]$  and

i-th row of

$$K_{12} = [1, 0, 0, -1]$$

then

$$V_{ai} = V_{bl} - V_{b3} + V_{ul} - V_{u4}$$

(4.9)

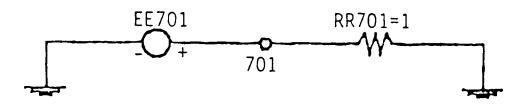

i.e., the voltage measurement at component  $a_i$  is the sum of the measured voltages,  $V_{bl}$ ,  $-V_{b3}$ ,  $V_{ul}$ , and  $-V_{u4}$ . In order to solve the equation (4.9) with SPICE program, a circuit type of description is used to generate the SPICE code. Here, the voltage controlled sources connected in series are used to indicate the sum of measured voltages,

Figure 4.1. Controlled Sources

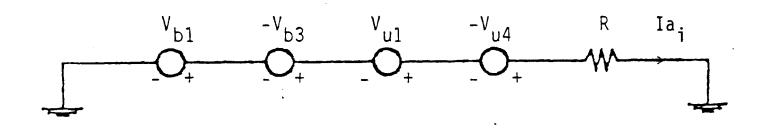

and the voltage measured at node \* is then the value of  $V_{ai}$ . Obviously, once the values  $a^{1}$  are known, the component equation (2.23) will give the values  $b^{1}$ . In circuit specification, the above box will be filled by the component. Given the values  $a^{1}$ , evidently the values  $b^{1}$  may be

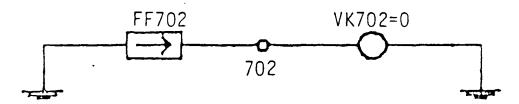

derived from their characteristics. For example, if the component is a resistor, connecting the resistor in series with the above sources as shown in Figure 4.2. Since a<sub>i</sub> is a voltage measurement, the current Ia<sub>i</sub> is the current that flows through the resistor.

Figure 4.2. Controlled Sources with Component

Similarly, the current controlled sources connected in parallel are used to describe the current measurement case.

After the SPICE code for equation (2.24) is generated properly, consider the equation (2.25) with the partitioned matrices,

$$a^2 = K_{21}^1 b^1 + K_{22}^1 u^p$$

(4.10)

$$b^{2} = \kappa_{21}^{2} b^{1} + \kappa_{22}^{2} u^{p}$$

(4.11)

The SPICE code for equation (4.11) is generated the same as that for equation (2.24), except that the box in Figure 4.1 is replaced by a zerovalued voltage source if the element of  $b^2$  is a current measurement, or by a resistor with resistance 1 for a voltage measurement. Similarly, the SPICE code for equation (4.11) can be generated in the same way, however, what we are interested in is the values  $\hat{b}^2$ . Therefore, the box in Figure 4.1 is filled by the component with equation (2.26) to compute the value  $\hat{b}^2$ . • .• ALGORITHM III: (Data Base) Step 1. (Linear Case) (Let C be the number of all possible subdivisions) DO i=1 TO C Compute K-matrix (Equations (2.12) through (2.15)). Compute M-matrix (Equation (2.16)). Store M to a data file named TEOO\*\*.DT, \*\*=i. End of Loop. Step 1. (Nonlinear Case) Let N be the number of components M be the number of test points, NM=N-M (For equations (2.23) and (2.24)) Step 2. DO i=1 TO NM IF ai is a voltage measurement THEN Connecting the controlled sources, which have nonzero elements in K<sub>12</sub>, in series. ELSE Connecting the controlled sources, which have nonzero elements in Kij and Ki2 in parallel. Connecting a zero-valued voltage source in series. (Remark: In SPICE, a zero-valued voltage source is used to measure the current) End if Connecting the group "1" component i in series. End of Loop (For equations (4.10) and (2.26)) Step 3. DO i=1 to M 2 If a; is a voltage measurement THEN Connecting the controlled sources, which have nonzero elements in  $K_{12}$ , and  $K_{12}$ , in series.

ELSE Connecting the controlled sources, which have nonzero elements in K11 and K12, in parallel. Connecting a zero-valued voltage source in series. End if Connecting the group "2" component i in the series. End of Loop Step 4. (For equation (4.11)) DO i=1 TO M 2 IF b<sub>i</sub> is a voltage measurement THEN Connecting the controlled sources, which have nonzero elements in K<sub>11</sub> and K<sub>12</sub>, in the series. Connecting a resistor with resistance 1. ELSE Connecting the controlled sources, which have nonzero elements in K<sub>12</sub>, and K<sub>12</sub>, in parallel. Connecting a zero-valued voltage source in series End If End of Loop

<u>Test Results</u>: In the linear case, only matrix-vector multiplications, equations (2.17) through (2.19), are required to evaluate  $b^2$ and  $\hat{b}^2$  while the SPICE program is executed for the nonlinear case. Use of this computed data to determine test outcome (either "good" or "bad" for each group "2" component) may be obtained by comparing  $b^2$  and  $\hat{b}^2$ . If  $b_i^2$  is equal to  $\hat{b}_i^2$ , then we say that the test outcome for the group "2" component i is "good"; otherwise, the component is "bad". In a more realistic environment, instead of requiring that  $b_i^2$ and  $\hat{b}_i^2$  be equal one may say that a component is "good" if  $b_i^2$  is sufficiently close to  $\hat{b}_i^2$  in some reasonable sense. In this way one may compensate for numerical errors and tolerance.<sup>10</sup> Moreover,  $b_i^2$  and  $\hat{b}_i^2$  are not necessarily scalars, they may be vectors, depending upon the component type with which one deals. For instance, a two-port component may require a two-tuple vector to represent its input/output characteristics.

ALGORITHM IV: (Test Results)

| Step 1.  | (Linear Case)<br>Let Z2 be the transfer function matrix for group "2"<br>UY=col(u,y)<br>M be the matrix for the data base. |

|----------|----------------------------------------------------------------------------------------------------------------------------|

| Sten 2   | Choose a component subdivision.                                                                                            |

|          | Retrieve the matrix M for this subdivision from                                                                            |

| 0000 0.  | the data base.                                                                                                             |

| Step 4.  | (Compute $a^2$ and $b^2$ )                                                                                                 |

| toop     | DO i=1 TO m                                                                                                                |

|          | DO $j=1$ TO s (s is the dimension of UY)                                                                                   |

|          | $A^{2}(i) = A^{2}(i) + M(i,j) + UY(j)$                                                                                     |

|          | B2(i) = B2(i) + M(m+i,j) + UY(j)                                                                                           |

|          | End of Loop j                                                                                                              |

|          | End of Loop i                                                                                                              |

| Step 5.  | (Compute b <sup>2</sup> )                                                                                                  |

|          | DO $i=1$ TO m                                                                                                              |

|          | B2W(i) = A2(i) * Z2(i,i)                                                                                                   |

|          | End of Loop $(Compare b^2 with b^2)$                                                                                       |

| Step 6.  | (Let $\varepsilon$ be the tolerance)                                                                                       |

|          | DO i=1 TO m                                                                                                                |

|          | VALUE =  B2W(i)-B2(i) / B2(i)                                                                                              |

|          | IF VALUE < = $\varepsilon$ THEN                                                                                            |

|          | RESULT(i) = 0                                                                                                              |

|          | ELSE                                                                                                                       |

|          | RESULT(i) = 1                                                                                                              |

|          | End If                                                                                                                     |

|          | End of Loop                                                                                                                |

| <u>.</u> | (New Jimeson (Jaco)                                                                                                        |

| Step I.  | (Nonlinear Case)<br>Let SOURCE.DT be a data file which contains the                                                        |

|          | SPICE code for test inputs and test data.                                                                                  |

|          | Let SPICE.DT be a data file which contains either                                                                          |

|          | (1) Modified SPICE code for the given circuit, or                                                                          |

|          | (2) SPICE code for test data.                                                                                              |

| Step 2.  |                                                                                                                            |

| 1        | used                                                                                                                       |

| Step 3.  | Concatenating the file SPICE.DT, SOURCE.DT and TEOO*.DT                                                                    |

|          | (where $*=i$ ) as an input file of SPICE program.<br>The output values $b^2$ and $\hat{b}^2$ are stored in a data file.    |

| Step 4.  | The output values of and of are stored in a data file.                                                                     |

|          |                                                                                                                            |

•

.

Once the test outcomes have been obtained, the algorithm reduces to a combinatorial "self-testing problem" in which one locates the actual failure. In other words, one may complete the test algorithm by implementing an appropriate decision algorithm.

## Decision Algorithms

Three decision algorithms, with their software implementation are presented:

- (1) Exact Algorithm,

- (2) Heuristic Algorithm, and

- (3) Boolean Expression Algorithm.

The first algorithm is employed to locate single failures, while the remaining two algorithms are used to identify multiple failures.

Exact Algorithm: In the single failure case, we assume that at most one component is faulty. As discussed in 42, we summarize all possible test results obtained from a given step of the algorithm, together with the conclusions as follows:

| <u>Test Résult</u><br>(1 2 3 m)                      | Conclusions                                                                                                                 |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | <pre>all group "2" components are good<br/>all group "2" except 1 are good<br/>all group "2" components are good<br/></pre> |

In the first case we conclude that all group "2" components are good. If a group two component were actually faulty then our test results are incorrect, which would only happen if one of the group "1" components was faulty. This would imply that the system has two faulty components, contradicting our assumption that, at most, one component is faulty. In case two, the same argument we used above will guarantee that the components which test good, say 2 through m, are good, and we have no information about x. It may be faulty or, alternatively, the test results may be due to a faulty group "1" component. In the remaining cases we have the same conclusion as in the first case. Since, under our assumption of a single failure, it is impossible for two or more group "2" components to be faulty, these test results imply that at least one of the group "1" component, and the group "1" component is the only faulty component, then the group "2" components are all good.

Consistent with the above arguments, at each step of the test algorithm, either all, or all but one, of the group "2" components are found to be good. If we choose our subdivision so that good components are included in group "1" the test results obtained at that step will be reliable, thereby, allowing us to accurately determine the faulty components in group "2."

From the above algorithm, one may be interested in the problem of how many steps are required to locate the faulty component(s): For . . single failure case, in each step of the algorithm, one concludes that all, or all but one, group "2" components are good. Thus, one may select a minimum collection of subdivisions which covers all components, i.e.,

Let  $N = \{1, 2, ..., n\}$  be a set of n components,

$S = \{\#1, \#2, ... \#C\}$  be a collection of all possible subdivisions,

where C is the number of subdivisions,

. then

$B = \min \{T \subset S \mid N \subset T\}$  (4.12)

is the minimum subcollection of S which covers N. The subcollection B is not unique. If  $B = \{B_1, B_2, ..., B_t\}$ , where  $B_i$  is in S, then, t is the minimum steps needed to locate the faulty component.

Recall that all, or all but one, components are known to be good at each step of the algorithm. After completing the test simulations with the above indicated subdivisions, a component which is the only one with test results "1" in a subdivision, may be faulty. If there exists only one such component, eventually, the component is located as faulty. However, if more than than one such components exist more steps are needed to identify the faulty components.

Let  $P = \{P_1, P_2, \dots, P_s\} \subset B$ , where  $P_i$  is the subdivision with the pattern that contains all "0" but one "1",

$R = \{R_1, R_2, ..., R_s\}, R_i \in P_i$ , where  $R_i$  is the component with test results "1", all  $R_i$  may not be distinct, and

Let  $R' = \{r_1, r_2, \dots, r_{s'}\} = R$ , where all  $r_i$  are distinct.

In the next steps, a subdivision with more than two components of R' is selected to simulate the test results, and the components which are known to be good will be excluded from R'. Therefore, the set R' is getting smaller. Repeating the above process until no such subdivision can be chosen, the algorithm is then terminated. Here, the number of times of the above processes plus t, the minimum steps needed in equation (4.12), is the maximum steps needed to locate the faulty component, and the components remaining in the set R' is the ambiguity set.

... ALGORITHM V: (Exact Algorithm for single failure case)

| Step 1. | (Off-line job)<br>Select the minimum subcollection of the subdivisions<br>which covers all components. B = {B <sub>1</sub> ,B <sub>2</sub> ,,B <sub>t</sub> }.                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 2. | (On-line)                                                                                                                                                                                                 |

| Step 3. | Simulate each subdivision B <sub>i</sub> , i = 1,2,t.<br>Let P = {P <sub>1</sub> ,P <sub>2</sub> ,,P <sub>S</sub> } ⊂ B, where P <sub>i</sub> are the subdivisions<br>with pattern (all "O" but one "l"). |

| Step 4. | Let $R = \{R_1, R_2, \dots, R_s\}, R_i \in P_i$ , are the components with test result "1"                                                                                                                 |

|         | IF s'=1 THen STOP [the component rj is faulty].                                                                                                                                                           |

| Step 6. | (More than one subdivisions with the above pattern)<br>Find a subdivision that contains more than one component<br>in R'.                                                                                 |

| Step 7. | IF no such subdivision THEN GOTO Step 8.<br>ELSE<br>Simulate the test result                                                                                                                              |

|         | R' < R' excludes the simulated good components.<br>GOTO Step 6.                                                                                                                                           |

| Step 8. | R' is the ambiguity set, and the components in R' are all possible faulty components.                                                                                                                     |

From the above algorithm, the step 1,  $B = \{B_1, B_2, \dots, B_t\}$ , can be derived off-line, and each  $B_i$  subdivision is simulated independently. Therefore, they can be computed by multiple processors, i.e., the parallel processors can be used to reduce the executing time. Thus the number t is the maximum number of processors needed.

To handle the multiple failure, following Liu, the problem can be greatly simplified if an "analog heuristic" is adopted. The effect will be that two independent analog failures will never cancel.<sup>20</sup> Needless to say, this is an inherently analog heuristic, since two binary failures have a fifty-fifty chance of canceling one another. In the analog case, however, two independent failures are highly unlikely to cancel one another (as long as one works with reasonably small tolerances). Based on the above argument, we may assume that a component is definitely good if the test result shows "0." Therefore, if a t-diagnosable system is assumed, that is, the number of faulty components does not exceed t, all possible test results with the conclusions are shown as follows:

### Test Result

### Conclusions

| 0<br>1<br>: | 0<br>0<br>: | 0<br>0<br>: | · · | 0<br>0<br>:<br>: | • | • | • •<br>• •<br>• • | 0<br>0<br>:<br>: | all group "2" components are good<br>components 2 thru m are good<br>:<br>:          |

|-------------|-------------|-------------|-----|------------------|---|---|-------------------|------------------|--------------------------------------------------------------------------------------|

| 1           | 1           | 1           | • • | 1                | 0 | 0 | • •               | 0                | components t+l thru m are good                                                       |

|             |             |             | ••  |                  |   |   |                   |                  | components t+2 thru m are good, and<br>at least one faulty component in<br>group "l" |

| :           | :           | :           | ::  | :                | : | : | ::                | :                | •                                                                                    |

| 1           | ٦           | 1           | ••  | •                | • | • | ••                | 1                | at least one faulty component in group<br>"]"                                        |

In the first t+l cases the results show that the component with test result "0" will be good. In the (t+2)-th case we claim that the components (t+2) through m are good and at least one faulty component in group "1." If none of the group "1" components were actually faulty then the test results obtained at this step are reliable. The system would then have t+l faulty components contradicting our assumption to the effect that, at most, t components are faulty. The remaining cases are the same as above. Unfortunately, the above argument gives the information that at least one of the group "1" components is faulty, but the identification of the faulty component in group "1" is still not available. Heuristic Algorithm: Based upon the "Analog heuristic" the Heuristic algorithm was presented as a multifailure decision algorithm. <sup>41,42</sup> In practice, the Heuristic algorithm is used with a coupling table.

The coupling table is designed to detect whether or not a faulty group "1" component will effect the test results on a group "2" component. Two components are called "coupled" if they are functions of each other. In order to set up this coupling table, we first look for the relationship between the group "2" components and the group "1" components.

Consider the equations (2.10) and (2.11) with the constant matrix K. One can rewrite the equation (2.10) as follows:

$$\begin{bmatrix} a_{1} \\ a_{2} \\ \vdots \\ a_{n-m}^{1} \end{bmatrix} = \begin{bmatrix} K_{11} \end{bmatrix} \begin{bmatrix} b_{1} \\ b_{2} \\ \vdots \\ b_{n-m}^{1} \end{bmatrix} + \text{ constant term}$$

and then

$a_{i}^{l} = \sum_{k=1}^{n-m} K_{11} b_{k}^{l} + \text{ constant term}$

If K<sup>ik</sup><sub>ll</sub> is not zero, then the group "1" component k effects the group

..."1" component i. Thus the (n-m) equations give the relationships between

the group "1" components. The equation (2.11) can be written as

$$a_{i}^{2} = \sum_{k=1}^{n-m} \kappa_{21}^{ik} b_{k}^{1} + \text{ constant term}$$

$$b_{i}^{2} = \sum_{k=1}^{n-m} \kappa_{21}^{tk} b_{k}^{1} + \text{ constant term, } t = m + i.$$

58 If  $K_{21}^{ik}$  or  $K_{21}^{tk}$  is not zero, then the group "1" component k effects the group "2" component i, and the components i and k are therefore coupled. ALGORITHM VI: (Coupling Table) • .• (Generate the matrix A for the relationship between Step 1: the group "1" components) (By a transitive closure algorithm<sup>1</sup>  $A = I \oplus E^{1} \oplus F^{2} \oplus F^{k}$ where  $E^k$  gives an explicit accounting of all the vertices jointed by paths of length k,  $\oplus$  is the Boolean "or" expression, and A is defined as A<sub>ij</sub> = 1 if i effects j = 0 otherwise ) Let E be the matrix K<sub>I</sub> in the equation (2.12). (K<sub>I</sub> is a m by m matrix and  $K_{21}$  is a 2m by m matrix) Initialize A(\*,\*)=0, F(i,i)=1 for i=1,2,..m. DO i=1 TO m  $F \leftarrow F \star E$  (i.e.,  $F=E^{i}$ ) IF F(j,k)=1 THEN A(j,k)=1 for all j and k End of loop (Generate the matrix B for the relationship between the Step 2: group "2" components and the group "1" components) (Let B<sub>1</sub> and B<sub>2</sub> be two Boolean matrices which are defined as follows:  $B_{1}^{ij} = 0 \quad \text{if} \quad K_{21}^{ij} = 0; \quad i=1,2,..m. \\ j=1,2,..,n-m. \\ = 1 \quad \text{if} \quad K_{21}^{ij} \neq 0$ and  $B_{2_{j}}^{ij} = 0 \quad \text{if} \quad K_{21}^{ij} = 0; \quad i=m+1, m+2, \dots 2m.$ = 1 \text{ if} \quad K\_{21}^{ij} \neq 0; \quad j=1,2,\dots n-m. therefore,  $B = B_1 \oplus B_2$ ) (define the matrices  $B_1$  and  $B_2$ ) DO i=1 TO m DO j=1 TO n-m IF  $K_{21}(i,j) = 0$  THEN  $B_1(i,j) = 0$