# **PK2100**C-Programmable Controller

**User's Manual**

Revision C

#### PK2100 User's Manual

Part Number 019-0014 • Revision C Last revised on April 28, 2000 • Printed in U.S.A.

# Copyright

© 1998 Z-World, Inc. • All rights reserved.

Z-World reserves the right to make changes and improvements to its products without providing notice.

#### **Trademarks**

- Dynamic C<sup>®</sup> is a registered trademark of Z-World, Inc.

- Windows is a registered trademark of Microsoft Corporation

- PLCBus is a trademark of Z-World, Inc.

- Hayes Smart Modem<sup>®</sup> is a registered trademark of Hayes Microcomputer Products, Inc.

#### **Notice to Users**

When a system failure may cause serious consequences, protecting life and property against such consequences with a backup system or safety device is essential. The buyer agrees that protection against consequences resulting from system failure is the buyer's responsibility.

This device is not approved for life-support or medical systems.

All Z-World products are 100 percent functionally tested. Additional testing may include visual quality control inspections or mechanical defects analyzer inspections. Specifications are based on characterization of tested sample units rather than testing over temperature and voltage of each unit. Z-World may qualify components to operate within a range of parameters that is different from the manufacturer's recommended range. This strategy is believed to be more economical and effective. Additional testing or burn-in of an individual unit is available by special arrangement.

# **Company Address**

**Z-World, Inc.** Telephone: (530) 757-3737 2900 Spafford Street Facsimile: (530) 753-5141

Davis, California 95616-6800 Web Site: http://www.zworld.com USA E-Mail: zworld@zworld.com

# **C**ONTENTS

| About This Manual                          | vii  |

|--------------------------------------------|------|

| PK2100 Overview                            | 1-1  |

| PK2100 Overview                            | 1-2  |

| PK2100 Features·                           | 1-3  |

| PK2110 Features                            | 1-3  |

| PK2120 Features                            | 1-3  |

| PK2130 Features                            | 1-3  |

| Options and Upgrades                       | 1-3  |

| Software Development and Evaluation Tools  | 1-4  |

| Getting Started                            | 2-1  |

| Initial PK2100 Setup                       | 2-2  |

| Connecting the PK2100 to a Host PC         | 2-3  |

| Establishing Communication                 | 2-3  |

| Running a Sample Program                   | 2-3  |

| I/O Configurations                         | 3-1  |

| PK2100 Inputs and Outputs                  | 3-2  |

| Universal Inputs                           | 3-4  |

| Digital Inputs                             |      |

| High-Sensitivity Differential Analog Input | 3-8  |

| Relay Outputs                              | 3-11 |

| Digital Outputs                            | 3-12 |

| Analog Output                              | 3-13 |

| Communication Interfaces                   | 3-14 |

| System Development                         | 4-1  |

| Programming                                | 4-2  |

| Gate Programming                           |      |

| Costatements                               | 4-2  |

| The Real-Time Kernel                       | 4-2  |

| The Five-Key System                        | 4-2  |

| Full C-Language Programming                |      |

PK2100 Contents • iii

| Virtual Driver                         |            |

|----------------------------------------|------------|

| Invoking the Virtual Driver            |            |

| Virtual Driver Services                | 4-4        |

| Virtual Driver Variables               |            |

| Digital Outputs                        | 4-6        |

| Digital Inputs                         | 4-6        |

| Universal Inputs                       | 4-6        |

| Timers                                 | 4-7        |

| Downloading Code                       | 4-8        |

| Direct Programming of the Serial Ports | 4-8        |

| Attainable Baud Rates                  | 4-9        |

| Z180 Serial Ports                      | 4-9        |

| Software Reference                     | 5-1        |

| Driver Software                        | 5-2        |

| Digital Input                          | 5-2        |

| Direct Driver                          | 5-2        |

| Virtual Driver                         | 5-2        |

| Digital Output                         | 5-2        |

| Direct Driver                          | 5-2        |

| Indirect Driver                        | 5-2        |

| Analog Input                           | 5-3        |

| Low-Level Direct Driver                |            |

| Calibrated Direct Driver               | 5-3        |

| Virtual Driver for Universal Inputs    | 5-4        |

| Analog Output                          | 5-5        |

| Direct Driver                          | 5-5        |

| Virtual Driver                         | 5-6        |

| High-Speed DMA Counter                 |            |

| Battery-Backed Clock                   |            |

| Liquid Crystal Display and Keypad      |            |

| EEPROM Read/Write                      |            |

| Flash EPROM Write                      |            |

| Communication                          |            |

| RS-232 Communication                   |            |

| Support Libraries and Sample Programs  | 5-12       |

| Appendix A: Troubleshooting            | <b>A-1</b> |

| Out of the Box                         |            |

| Dynamic C Will Not Start               |            |

| Dynamic C Loses Serial Link            |            |

| PK2100 Resets Repeatedly               |            |

| Common Programming Errors              | A-4        |

| Appendix B: Specifications                     | B-1 |

|------------------------------------------------|-----|

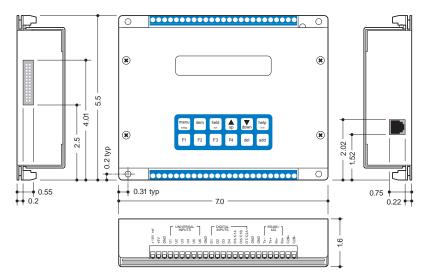

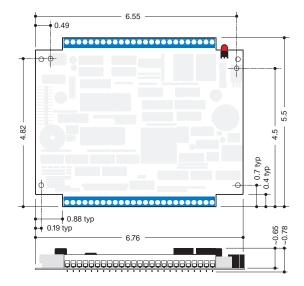

| Hardware Dimensions                            | B-2 |

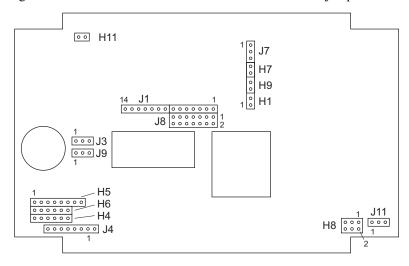

| Jumper and Header Specifications               | B-4 |

| Connectors                                     | B-7 |

| Environmental Temperature Constraints          | B-7 |

| Appendix C: Power Management                   | C-1 |

| Power Failure Interrupts                       |     |

| Heat Sinking                                   |     |

| Appendix D: I/O Map and Interrupt Vectors      | D-1 |

| I/O Map                                        | D-2 |

| Interrupt Vectors                              |     |

| Jump Vectors                                   |     |

| Interrupt Priorities                           |     |

| Appendix E: EEPROM                             | E-1 |

| PK2100/PK2120 24-V Version Calibration         | E-2 |

| PK2110/PK2130 12-V Version Calibration         | E-4 |

| Field Calibration                              | E-4 |

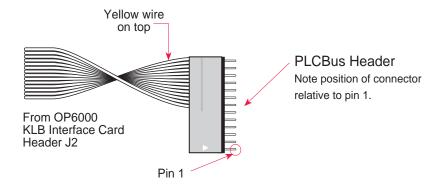

| Appendix F: PLCBus                             | F-1 |

| PLCBus Overview                                | F-2 |

| Allocation of Devices on the Bus               |     |

| 4-Bit Devices                                  | F-6 |

| 8-Bit Devices                                  | F-7 |

| Expansion Bus Software                         | F-7 |

| Appendix G: Battery                            | G-1 |

| Storage Conditions and Shelf Life              | G-2 |

| Instructions for Replacing the Lithium Battery |     |

| Battery Cautions                               |     |

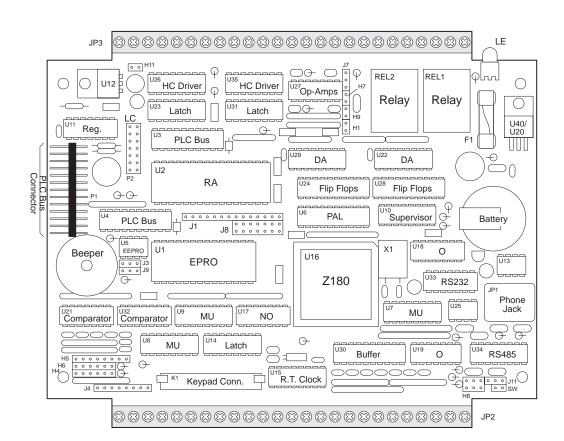

# **Board Layout**

# Index

PK2100 Contents + v

vi + Contents PK2100

# ABOUT THIS MANUAL

This manual provides instructions for installing, testing, configuring, and interconnecting the Z-World PK2100 controller. Instructions are also provided for using Dynamic  $C^{TM}$  functions.

Instructions to get started using Dynamic C software programming functions as well as complete C and Dynamic C references and programming resources are referenced when necessary.

# **Assumptions**

Assumptions are made regarding the user's knowledge and experience in the following areas:

- Ability to design and engineer the target system that a PK2100 will control.

- Understanding of the basics of operating a software program and editing files under Windows on a PC.

- Knowledge of the basics of C programming.

For a full treatment of C, refer to the following texts:

*The C Programming Language* by Kernighan and Ritchie (published by Prentice-Hall).

and/or

*C: A Reference Manual* by Harbison and Steel (published by Prentice-Hall).

• Knowledge of basic Z80 assembly language and architecture.

For documentation from Zilog, refer to any of the following texts:

Z180 MPU User's Manual Z180 Serial Communication Controllers Z80 Microprocessor Family User's Manual

## **Terms and Abbreviations**

Table 1 lists and defines terms and abbreviations that may be used in this manual.

Table 1. Terms and Abbreviations

| Term / Abbreviation | Description                                    |

|---------------------|------------------------------------------------|

| PIO                 | Programmable Input / Output Integrated Circuit |

| RAM                 | Random Access Memory                           |

| RTC                 | Real-Time Clock                                |

| SIB                 | Serial Interface Board                         |

| SRAM                | Static Random Access Memory                    |

| NMI                 | Non-Maskable Interrupt                         |

#### **Conventions**

Table 2 lists and defines typographical conventions that may be used in this manual.

Table 2. Term and Abbreviation Conventions

| Example  | Description                                                                                                                                    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| While    | Courier font (bold) indicates a program, a fragment of a program, or a Dynamic C keyword or phrase.                                            |

| // IN-01 | Program comments are written in Courier font, plain face.                                                                                      |

| Italics  | Indicates that something should be typed instead of the italicized words (e.g., in place of <i>filename</i> , type a file's name).             |

| Edit     | Sans serif font (bold) signifies a menu or menu selection.                                                                                     |

|          | An ellipsis indicates that (1) irrelevant program text is omitted for brevity or that (2) preceding program text may be repeated indefinitely. |

| []       | Brackets in a C function's definition or program segment indicate that the enclosed directive is optional.                                     |

#### byte

To emphasize that certain functions must operate on 8-bit bytes, the term byte is used as a type specifier. Byte is actually a type character, not a standard C keyword. Parameters defined by byte are not standard C characters, they are 8-bit bytes. This function does not work in an application unless first declared with typedef or #define.

## • Pin Number 1

A black square indicates pin 1 of all headers and jumpers.

#### **Icons**

Table 3 displays and defines icons that may be used in this manual.

Table 3. Icons

| Icon     | Meaning         |

|----------|-----------------|

| 6        | Refer to or see |

| <b>1</b> | Please contact  |

| <u> </u> | Caution         |

|          | Note            |

| Tip      | Tip             |

|          | Factory Default |

# PK2100 OVERVIEW

Chapter 1 provides an overview and brief description of the PK2100 C-Programmable controller features, options, and upgrades.

#### PK2100 Overview

The PK2100 series is Z-World's most comprehensive controller that connects directly to many sensors and peripheral devices without needing intermediate signal conditioning. A typical application for the PK2100 is the control of medium-scale production equipment, such as packaging machinery, special-purpose machine tools, or material processing systems. The PK2100 can be used to detect contact closures, count pulses, and measure analog values such as temperature or pressure.

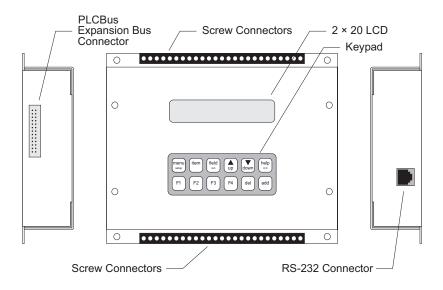

The PK2100 has two built-in relays and it can directly drive 10 external relays or solenoids. There is an analog output capability, including the 4-to 20-mA loop output standard in the control industry. The PK2100 has an optional built-in keypad and liquid-crystal display (LCD). There is a PLCBus expansion bus connector that allows external expansion of the input/output capabilities or the addition of interface devices designed by the user. The PK2100 has serial communication capability suitable for communicating with other controllers one at a time or in a plant-wide network. It supports both RS-232 and RS-485/RS-422 serial communication modes.

Figure 1-1. PK2100 C-Programmable Controller

#### PK2100 Features

- · Seven fixed digital inputs

- · Six "universal" inputs

- · One high-gain differential analog input

- Ten high-current outputs capable of driving inductive loads such as solenoids and relays

- · Two SPDT relays

- Two analog outputs

- 2 x 20-charcter LCD screen (backlighted display available) and 2 x 6 keypad

- PLCBus port

- One RS-232 port and one RS-232 or RS-485/RS-422 port

- Rugged enclosure

- · Battery-backed RAM up to 512 kbytes

- EPROM up to 512 kbytes for holding program and data

- Optional flash EPROM to replace standard EPROM

- · Battery-backed time/date clock

- Lithium button battery, which lasts about 10 years in normal use, to

provide power for the time/date clock and the battery-backed memory

when no external power is supplied to the unit; option for nickelcadmium battery or a super capacitor for battery backup

- · Watchdog timer

- Power failure warning interrupt

- EEPROM, standard 512 bytes, to hold factory-set calibration constants and user configuration data of a more permanent nature than data held in the battery-backed RAM

#### PK2110 Features

The PK2110 is a 12-volt version of the PK2100.

#### PK2120 Features

The PK2120 is a PK2100 without the enclosure, the keypad or the LCD.

#### PK2130 Features

The PK2130 is a 12-volt version of the PK2120.

# **Options and Upgrades**

- 9.216-MHz clock upgrade can be factory installed.

- 128-kbyte flash EPROM can be factory installed.

- 128-kbyte or 512-kbyte SRAM can be factory installed.

- Backlit-character LCD is available for the PK2100 and the PK2110.

Appendix B provides detailed specifications for the PK2100.

# **Software Development and Evaluation Tools**

Dynamic C, Z-World's Windows-based real-time C language development system, is used to develop software for the PK2100. The host PC downloads the executable code through the PK2100's RS-232 port to one of the following places:

- battery-backed RAM,

- ROM written on a separate ROM programmer and then substituted for the standard Z-World ROM, or

- optional flash EPROM, which may be programmed or reprogrammed without removing it from the controller.

This allows fast in-target development and debugging.

A PK2100 Development Kit contains the manual, schematics, programming cable, power supply, 128-kbyte flash EPROM and a demonstration board to simulate input/output.

Z-World's Dynamic C reference manuals provide complete software descriptions and programming instructions.

# **GETTING STARTED**

Chapter 2 provides instructions for connecting the PK2100 to a host PC and running a sample program.

# **Initial PK2100 Setup**

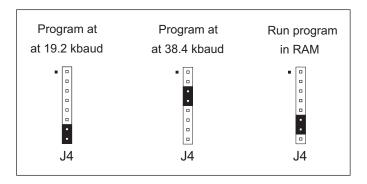

When the PK2100 powers up, it reads its board jumpers, the keypad, if any, and the contents of the EEPROM to determine its mode of operation. The following modes of operation are available:

- 1. Run a program stored in battery-backed RAM.

- 2. Program at 19.2 kbaud using the RS-232 port.

- 3. Program at 38.4 kbaud using the RS-232 port.

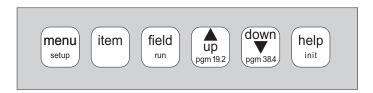

The keypad (Figure 2-1) may be used to set the mode. Hold down the MENU/setup key and one other key (FIELD/run, UP/pgm 19.2, or DOWN/pgm 38.4) simultaneously. The unit will beep to acknowledge the change of operating mode.

Figure 2-1. PK2100 Keypad

The watchdog timer must be enabled when the keypad is used to set the mode.

A jumper installed on jumper block J4 overrides any keypad settings. The jumper block must be used when a keypad is not available, for example, in the PK2120 controller. Figure 2-2 illustrates the jumper configurations.

Figure 2-2. PK2100 Jumper Configurations for Programming

# Connecting the PK2100 to a Host PC

- 1. Make sure the PK2100 power source is not connected.

- Connect the PK2100 to the host PC's RS-232 serial COM port. A 9-pin to RS-232 "phone plug" adapter is included with the developer's kit.

- 3. Connect the red-tagged lead from the 24-volt (or 12-volt) power supply to the +24-volt screw connector. Connect the other power supply lead to the GND screw connector.

- 4. Plug the power supply into a wall socket.

The North American version of the PK2100 developer's kit comes with a 24-volt D.C. power supply. International users and users of PK2110/PK2130 controllers, which are designed for 12 volts, must provide an appropriate power supply.

The PK2100 is now ready to be programmed.

# **Establishing Communication**

Communication between the PC and the PK2100 becomes possible once the hardware is connected and the Dynamic C software has been installed. Double-click the Dynamic C icon to start the software. Note that the PC attempts to communicate with the PK2100 each time Dynamic C is started. No error messages are displayed once communication is established.

See Appendix A, Troubleshooting, if an error message such as **Target Not Responding** or **Communication Error** appears.

Once the necessary changes have been made to establish communication between the host PC and the PK2100, use the Dynamic C short-cut **Ctrl Y** to reset the controller and initiate communication.

# **Running a Sample Program**

1. Open a sample program located in Dynamic C subdirectory. **SAMPLES\CPLC**.

See Appendix A, Troubleshooting, if an error message such as **Target Not Responding** or **Communication Error** appears.

- 2. Compile the program by pressing **F3** or by choosing **Compile** from the Compile menu. Dynamic C compiles and downloads the program into the PK2100's flash memory.

- 3. Run the program by pressing **F9** or by choosing **Run** from the **Run** menu.

- 4. Press **Ctrl Z** to stop execution of the program.

- 5. If needed, press **F9** to restart execution of the program.

# I/O CONFIGURATIONS

Chapter 3 discusses how to configure the available inputs/outputs in the PK2100 controller.

# **PK2100 Inputs and Outputs**

The PK2100 provides these types of inputs/outputs:

- "Universal" analog inputs.

- Protected digital inputs.

- · High-gain differential analog input.

- · SPDT relays.

- High-current driver outputs capable of driving inductive loads such as solenoids and relays.

- · Analog outputs.

- 2 × 20-charcter LCD screen (backlighted display available) and 2 × 6 keypad.

- Serial communication channels: PLCBus port, RS-232 port, and RS-232 or RS-485/RS-422 port.

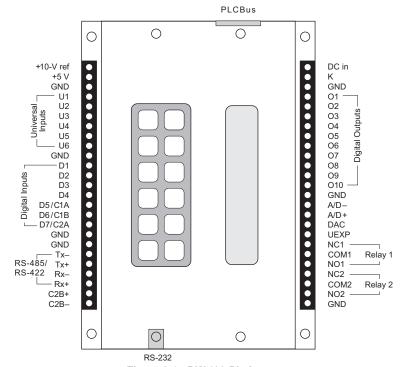

Figure 3-1 shows the signal names of the PK2100's screw connectors. The chapter describes the various interfaces and presents some typical applications. There are 50 screw terminals used for input, output, and power connections. In addition, there are two connectors on the sides of the unit: a modular "phone jack" connector for the RS-232 port, and a 26-pin connector for the PLCBus expansion port.

Figure 3-1. PK2100 Pin Layout

The connector labeled "+10-V ref" is nominally 7 volts for the PK2110/PK2130 12-volt versions of the PK2100. The connector labeled "DC in" is 12 or 24 volts, depending on the specific PK2100 model.

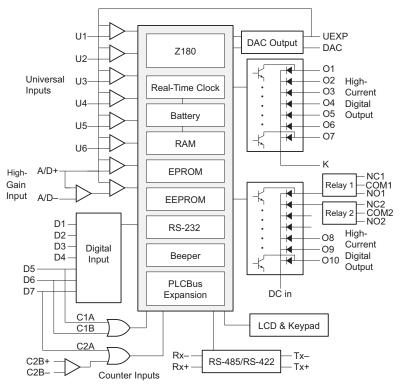

Figure 3-2 shows a PK2100 block diagram. The PK2100's board layout and schematic are included in this manual.

Figure 3-2. PK2100 Block Diagram

The PK2100 has the following input/output interfaces:

- Six universal inputs that may be used as analog inputs (to measure voltage, current, or resistance) or as digital inputs (to measure a voltage compared to a specific threshold voltage or to softwarespecifiable high and low thresholds). The universal inputs accept 0– 10 volts with 10-bit resolution.

- 2. Seven digital inputs with a 2.5-volt threshold. Three of the inputs are dual-purpose—they function either as general-purpose digital inputs or as counter inputs. When serving as counter inputs, the three inputs provide two counter inputs capable of counting pulses at 100 kHz or more. The counter inputs can also be used to measure pulse widths and other pulse timing characteristics.

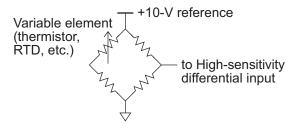

- 3 One high-sensitivity differential analog input. Normally, the high-sensitivity range is 0–1 volts, but the input gain can be changed by installing different input resistors on the operational amplifier. When the positive side of the differential input is more than 1 volt, its voltage can be measured by the universal input with which it is coupled. This input is suitable for connection to resistance bridges.

- 4. Two relay-contact outputs (NO, NC, COM for each relay). The relays are rated for 3 amps at 48 volts. Contact-protection devices may be installed.

- 5. Ten high-current outputs suitable for driving relays, stepping motors, or solenoids. These outputs can sink approximately 300 milliamps each at up to 48 volts, subject to total heat dissipation restrictions for the integrated-circuit driver.

- 6. One analog output (DAC), which may be a voltage output (0–10 volts for PK2100/PK2120 and 0–7 volts for PK2110/PK2130) or a current output (0–20 mA for PK2100/PK2120 and 0–15 mA for PK2110/PK2130). A second analog voltage output (UEXP) is available when the universal inputs are used as fixed-threshold digital inputs.

- 7 Communication interfaces including a full-duplex RS-422/RS-485 serial port that can operate asynchronously at up to 38,400 baud, and an RS-232 serial port with two handshaking lines that can operate at up to 38,400 baud. A second RS-232 port can be configured as a substitute for the RS-422/RS-485 port by changing board jumpers, but it will have no handshaking lines. There is also a 26-pin connector to Z-World's PLCBus expansion bus for customer-designed devices or Z-World PLCBus expansion devices.

# Universal Inputs

The "universal" interface comprises six analog inputs (U1–U6) with a measurement range of 0–10 volts (0–7 volts for PK2110/PK2130). An additional universal input channel (A/D+) is available when it is not in use as part of the high-gain input.

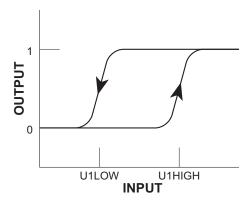

A universal input may be read either as an analog input (by taking an analog reading) or as a digital input by comparing the voltage at the input with a threshold. Software provided by Z-World can be used to compare the input voltage to a single fixed threshold or to two software-specified thresholds.

Single Threshold. A digital "1" results when the voltage is above the threshold. Otherwise a digital "0" results.

*Dual Threshold.* A digital "1" results when the voltage is above the high threshold. A digital "0" results when the voltage is below the low threshold. Otherwise, the software reports no change. Z-World's virtual driver

software (see Chapter 4, System Development) provides the two thresholds.

The universal inputs are protected against overloads between -48 and +48 volts. The analog resolution is 10 bits, providing approximately 1024 steps over the range 0–10 volts (0–7 volts for PK2110/PK2130). Its sensitivity is about 10 millivolts per step.

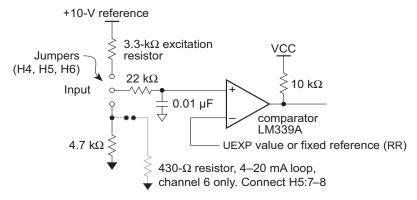

Figure 3-3 shows a schematic of a single universal input channel.

Figure 3-3. Universal Input Channel

Each input uses a comparator driven by the signal and by an internal DAC to measure the input voltage. The input resistor and capacitor filter out high-frequency noise and provide protection against overloads. Clamp diodes in the LM339A provide additional protection against overload. The input has a high D.C. impedance unless one of the jumpers is connected. If the excitation resistor is connected, the circuit provides an excitation voltage or current to an external device. This is convenient for measuring an external resistance such as a potentiometer or a temperature sensor (Figure 3-4).

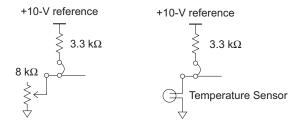

Figure 3-4. Measuring Variable External Resistance

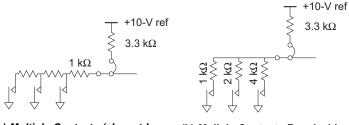

Multiple contacts may be connected with external resistors to a single universal input (Figure 3-5).

(a) Multiple Contacts (closest has (b) Muliple Contacts Resolvable priority) Individually

Figure 3-5. Use of External Resistors to Connect Multiple Contacts to Single Universal Input

#### Digital Inputs

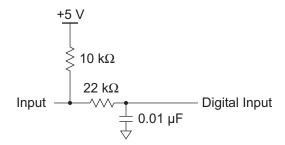

The seven digital inputs accept an input voltage with a digital threshold at approximately 2.5 volts. The inputs are protected against overload over a range from -48 to +48 volts. These inputs are convenient for detecting contact closures or sensing devices with open collector transistor outputs. Logic-level outputs can also be detected as long as they are supplied from CMOS logic outputs guaranteed to swing to at least 3.5 volts. Three of the digital inputs are shared as inputs to the high-speed counters.

Figure 3-6 shows a digital input. The RC circuit helps to stabilize the input, but note the 0.2-millisecond RC time constant, which affects signals faster than 5 kHz. While it may be tempting to disable the capacitor with a jumper, this is not recommended because the signal may be degraded.

Figure 3-6. PK2100 Digital Input

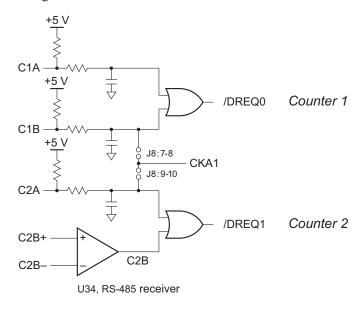

Three of the digital inputs also serve as counter inputs. In addition, there is a special differential counter input. The counter inputs are arranged as shown in Figure 3-7.

Figure 3-7. Digital Inputs Used As Counter Inputs

The counters count on a negative-going edge. Each counter has two inputs, which are symmetrical in that one can be used as a gate and the other can be used as a count input.

The RS-485 receiver input can be used as a digital input by attaching one side of it to the desired threshold voltage. This input can be used as a true differential input for such devices as inductive pickups. It has a common-mode voltage range from -12 to +12 volts with an input hysteresis of 50 millivolts.

An internal jumper can connect the signal from input/output procesor CKA1, which is controlled by the second (RS-485) serial port's hardware. CKA1 can be set to count pulses at 100 kHz or more down to a few hundred hertz.

The counters are implemented by using the DMA channels of the Z180 microprocessor. The maximum count speed is more than 100 kHz. The DMA channel can be programmed to store a byte from an input/output port to memory for each count, if desired. This byte can be the least significant byte of the internal programmable counter (PRT), which allows the count edge to be localized in time. This feature can also determine the

exact time, within a few microseconds, at which an event occurs by programming the DMA channel to store one byte and then interrupt the count. The interrupt routine can read the most significant part of the PRT counter and any software extension of this counter. In general, the maximum count is 65,536, which can be extended by software to larger counts if the counting speed is not higher than about 10 kHz.

The capabilities of the counters are summarized below.

- Counters measure the time at which a negative edge occurs with a

precision of a few microseconds. The measurement can be repeated

hundreds of times per second. A minimum time must occur between

successive events to allow for interrupt processing.

- Counters measure the width of a pulse by counting (up to 65,536) at a rate from more than 100 kHz to 300 Hz. This provides 16-bit accuracy in the measurement of pulse widths.

- Counters count negative-going edges for up to two channels. The maximum count for high-speed counting (5 kHz to more than 100 kHz) is 65,536. The maximum count for low-speed counting is unlimited.

# High-Sensitivity Differential Analog Input

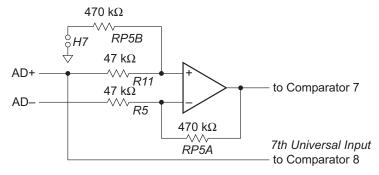

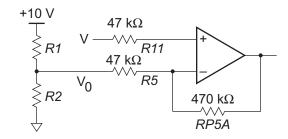

One high-sensitivity analog input is available. This input has a differential input with a gain of 10 compared to the universal input. This input is useful for devices requiring higher input sensitivity, for example, thermistors or RTDs in a bridge. Although the high-sensitivity input has 10 times the gain and accuracy, the dynamic range is necessarily 10 times less, since the number voltage steps available from the conversion (1024) does not change. Figure 3-8 shows the high-sensitivity input circuit.

Figure 3-8. High-Sensitivity Differential Analog Input

The gain at the plus and minus inputs is 10 when jumper H7 is installed. The gain of the plus input becomes higher (11) when H7 is removed. This has the effect of skewing the output from a nulled bridge circuit to the middle of the measurement range. Such a bridge circuit is shown in Figure 3-9 below. When the bridge is nulled, both inputs are equal to 5 volts. The output voltage of the input amplifier with H7 removed is  $5 \times (11 - 10) = 5$  volts. This is in the middle of the 10-volt measurement range of

Figure 3-9. Nulled Bridge Circuit for Measuring High-Sensitivity Differential Analog Input

0-10 volts.

The bridge makes it possible to detect changes of  $\pm 0.04$  percent in the value of the variable-resistor element when the gain is 10. A change of only  $\pm 0.2$  percent can be detected without a bridge.

$$g = 10 = \frac{R5 + RP5A}{R5} \times \frac{RP5B}{RP5B + R11}$$

Jumper H7 installed

The gain for the negative input, AD-, is given by RP5A/R5. The gain for

$$g = 11 = \frac{R5 + RP5A}{R5} \times (1)$$

. Jumper H7 not installed

the positive input, AD+, is given by:

Ωt

The calibration gain and offsets are stored in the EEPROM (see Appendix E).

The output voltage, y, is given by

$$y = a_1 \times (x_1 + a_0) - b_1 \times x_2$$

where

$x_1$  and  $x_2$  are the positive and negative inputs, respectively,

$a_1$  is the positive-side gain,

$a_0$  is the positive-side offset, and

$b_1$  is the negative-side gain.

**RK219A** at  $b_1$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to the calibrated value of  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to  $a_1^{\text{IV}}$  is also equal to  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to  $a_1^{\text{IV}}$  is also equal to  $a_1^{\text{IV}}$  in  $a_1^{\text{IV}}$  (where  $a_1^{\text{IV}}$  is also equal to  $a_$

If the negative input x, is tied to ground, the equation becomes

$$y = a_1 \times (x_1 + a_0)$$

or, solving for  $x_1$ ,

$$x_1 = \frac{y}{a_1} - a_0 .$$

This equation returns the input voltage, given the output. The function  $up\_higain(1)$  returns this value (with Jumper H7 removed). If the output of the operational amplifier is out of range  $(x_1$  input above 1 volt, y output above 10 volts), the value of a direct measurement of  $x_1$  is returned. This is less accurate by a factor equal to the gain ratio. Solving this equation for  $(x_1 - x_2)$  in terms of y and  $x_1$  yields

$$(x_1 - x_2) = \frac{y}{b_1} - \left(\frac{a_1}{b_1} - 1\right) \times x_1 - a_0 \times \frac{a_1}{b_1}$$

.

The function  $up\_higain(2)$  returns this value (with Jumper H7 removed). This is the difference between inputs  $x_1$  and  $x_2$  in terms of y and  $x_1$ , both of which can be measured directly. The accuracy with which the difference voltage is measured is approximately 10 times greater than for the regular universal input channels: 1 millivolt instead of 10 millivolts.

Change resistor R5, and possibly R11, to change the gain of the high-gain input. These 47-k $\Omega$  resistors are factory-installed for a gain of 10 (or 11 if Jumper H7 is removed). A smaller resistor will increase the gain. For example, changing both the R5 and R11 resistors to  $10 \text{ k}\Omega$  will increase the gain to 47 (or 48 with Jumper H7 removed). When differential inputs are desired, it is preferable to operate with H7 removed since the gain difference between the positive and negative inputs will be exactly 1 and will not depend on a balance between resistors, making the output 5 volts when both differential inputs are 5 volts. As the gain is increased, it becomes necessary to use an operational amplifier with a more stable offset voltage than the LM324, which has considerable drift over temperature. The Linear Technology LM1014 is suitable for gains up to 100 or more. The negative input has a low input impedance compared to the positive input when H7 is removed. If R5 is decreased to increase the gain, this impedance becomes even lower. When a bridge is used, the finite impedance of the negative input will change the gain slightly.

The gain for a bridge such as

would be

$$g = g_0 \times \left(1 - \left(\frac{1}{1 + \frac{R5}{R2} + \frac{R5}{R1}}\right)\right)$$

.

The change in gain for the input  $(V-V_0)$  is given by the above formula. If R5 is 47 k $\Omega$  and R1 and R2 are each 350  $\Omega$ , then the gain is reduced by the factor

$$1 - \left(\frac{1}{1 + \frac{47,000}{350} + \frac{47,000}{350}}\right) = 0.9962$$

or about 4 parts in 1000.

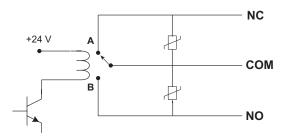

## Relay Outputs

The PK2100 has two relays. Each relay (Figure 3-10) is single pole, double throw. The rated current is 3 A and the rated voltage is 48 V. Optional metal-oxide varistors (MOV) may be installed on the board to protect the contacts. When the voltage across the contact exceeds the trigger voltage of the MOV, the MOV acts as a short circuit, preventing or minimizing sparking and arcing.

Figure 3-10. PK2100 Relay

The relay output signals are routed through the U35 high-current driver chip.

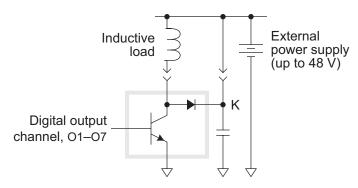

## **Digital Outputs**

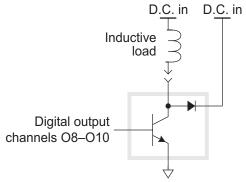

The PK2100 has 10 digital outputs (O1–O10). Seven of the outputs belong to one high-current driver chip (U26) and three belong to another chip (U35). These outputs can drive inductive loads such as relays, small solenoids, and stepping motors.

Outputs O1–O7 on U26 use a common bus ("K") for the protective diodes. Thus, it is possible to use a power supply for these outputs other than the power supply for the PK2100. All loads connected to the same group of drivers must use the same power supply so the diodes can return inductive spikes to the same power supply. Refer to Figure 3-11.

Figure 3-11. Routing External Power Supply for PK2100 Digital Outputs

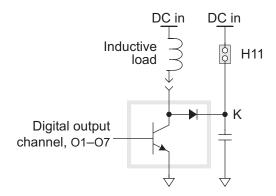

If the PK2100's power supply (DC in, 12 or 24 volts) is used, route K to the power supply by connecting jumper H11. Refer to Figure 3-12.

Figure 3-12. Routing PK2100 Internal Power Supply for Digital Outputs

The diodes on U35 for outputs O8–O10 use the PK2100's power supply directly.

Figure 3-13. Routing PK2100 Power Supply for Digital Outputs 08–010

The drivers used are the Motorola MC1413B or the equivalent Texas Instruments ULN2003. One drives outputs O1–O7, and the other drives outputs O8–O10, the onboard relays and the beeper. Each driver chip can dissipate a maximum of 1.25 watts when the ambient temperature is 60°C. Each output consumes power, depending on the current, as follows.

100 mA 0.10 W 200 mA 0.25 W 350 mA 0.50 W

This limits the maximum current to approximately 150 milliamps per output if all outputs are turned on at the same time for a 100 percent duty cycle. The maximum current for any single output is 500 milliamps.

# **Analog Output**

One analog output (DAC) is provided. With Pins 2-3 on Jumper J7 connected, the output can be a voltage (0–10 volts for PK2100/PK2120 and 0–7 volts for PK2110/PK2130); connecting Pins 1-2 on Jumper J7 turns the output into a current output suitable for driving current loops at 4–20 mA. The analog output will drive 20 milliamps (15 milliamps for PK2110/PK2130) up to 470  $\Omega$  with a resolution of 10 bits.

Another 10-bit analog output channel (UEXP) is available if it is not being used to support the universal inputs.

#### Communication Interfaces

The PK2100 comes with a full-duplex RS-422/RS-485 serial port that can operate asynchronously at up to 38,400 baud (57,600 with the optional 9.216-MHz clock upgrade). An RS-232 serial port with two handshaking

lines can also operate at up to 38,400 baud (57,600 with the optional 9.216-MHz clock upgrade).

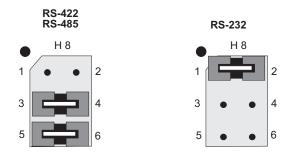

A second RS-232 port can be configured as a substitute for the RS-422/RS-485 port by changing board jumpers, but it will have no handshaking lines. Pins 3-4 and 5-6 on Header 8 are connected to enable RS-422/RS-485 communications. Remove these jumpers and connect Pins 1-2 on Header 8 to enable the second RS-232 output. The RS-232 output pin will be TX-, and the input will be RX-. RX+ must be tied to ground. The jumper arrangements are shown in Figure 3-14.

The PK2100 has a 26-pin connection to allow access to Z-World's PLCBus expansion bus for customer-designed devices or Z-World's PLCBus expansion devices.

Figure 3-14. H8 Jumper Configurations

# System Development

Chapter 4 describes the programming support for the PK2100.

# **Programming**

Z-world supports program development for the PK2100 in a variety of ways. Support for some of these stems from a virtual driver, which monitors the PK2100's ports and provides a set of "virtual" latches, timers, counters, function keys and two DAC analog outputs.

## Gate Programming

Gate programming is a quick and easy way to program the PK2100's inputs and outputs. The logic elements are summarized in Table 4-1.

| External             | Internal                           |

|----------------------|------------------------------------|

| Seven digital inputs | Thirty memory latches              |

| Six universal inputs | Ten on-delay timers                |

| Ten digital outputs  | Five countdown counters            |

| Two relay outputs    | Four special function keys         |

|                      | Discrete digital-to-analog outputs |

Table 4-1. Gate Programming Logic Elements

An operator updates the parameters supported by these logic elements using the five-key system. Gate programs can be downloaded or uploaded serially through the RS-232 connection to a PC.

Gate programming is not C programming. It is done with an application program, written in C, that modifies the parameters of the virtual driver.

Support functions for gate programming may be found in the subdirectory LIBRARY\GATE\_P.LIB. The programs SCAN.C and GATER.C in SAMPLES\CPLC are examples of gate programming.

#### Costatements

Costatements, formerly called function blocks, implement cooperative multitasking, and use the virtual driver.

#### The Real-Time Kernel

The real-time kernel allows a preemptive multitasking system to be developed.

# The Five-Key System

The five-key system implements a user interface to the software using the PK2100's keypad and liquid crystal display.

# Full C-Language Programming

Full C-language programming may access all the features available in Dynamic C and its libraries. Gate programming and costatements use Z-World's virtual driver. Full Dynamic C programming, of course, may include any method or combinations of methods.

#### Virtual Driver

The virtual driver is a software package activated by a periodic interrupt every 25 milliseconds and provides certain services to the application programmer.

The virtual driver provides the following services.

- Running real-time second and millisecond clocks.

- Scanning the universal inputs to compare them against preset thresholds.

- Scanning the digital inputs and setting digital outputs.

- Providing any number of "virtual" watchdog timers.

- Providing clock drive for the optional real-time kernel.

- Providing control for an audible beeper.

- Providing a driver for the keypad.

- Providing a driver for the liquid crystal display.

The following switches turn off the services of the virtual driver. If used, they must precede driver calls. Leave the switch undefined to avoid disabling the service.

#### #define NOUNIVERSAL

Disable the virtual driver for digital inputs, universal inputs, digital outputs and relays.

#### • #define NOTIMERS

Disable the virtual timers. The virtual timers are software timers, useful in ladder logic programming and gate programming.

#### • #define NOLCD

Disable the liquid crystal display (LCD). This directive will prevent the initialization of the LCD. Commands to the LCD have no effect unless the LCD has been initialized. The following preprocessor variables control features of the virtual driver.

#### • #define N WATCHDOG nn

Specify the number of virtual watchdog timers. Each virtual watchdog has a counter that has to be reloaded. If the counter for any virtual watchdog counts down to zero, a hardware reset is forced. To reload a virtual watchdog, type

#### up wdoghit( int watchdog, byte count )

where count is the number of 25-millisecond ticks to countdown. A virtual watchdog wdog can be monitored, if necessary, by reading the internal variable 1c\_wdogarray[wdog-1]. The program VWDOG.C in the subdirectory SAMPLES\CPLC illustrates the use of virtual watchdog timers.

#### • #define RUNKERNEL

Request the real-time kernel. It will be initialized.

#### • #define KEYREQUEST nn

Request a real-time kernel task when a key is pressed. The sample program **SAMPLES\CPLC\VWDOG.C** illustrates the use of this directive.

#### Invoking the Virtual Driver

Call uplc\_init() from the main function to invoke the virtual driver. This call will initialize the following items:

Variables for the virtual driver.

Virtual watchdog timers (if requested).

The liquid crystal display (unless disabled).

The real-time kernel (if requested).

The timer that runs the background routine.

The program must periodically hit the (hardware) watchdog uplc init() to keep it from timing out.

## Virtual Driver Services

# • up\_beep( int milliseconds )

Beeps the built-in beeper for the number of milliseconds specified.

#### • up beepvol( int code )

Sets beeper volume. The **code** is 0, 1, or 2, and corresponds to beeper off, low, or high volume.

#### • lcd\_printf( long cursor, char \*fmt, arg...)

Print on the liquid crystal display screen. The variable cursor determines the position of the cursor before and after the string of characters determined by the format \*fmt and the arguments (arg...) is printed according to traditional printf conventions. The cursor variable is a long integer consisting of four bytes, Y1, X1, Y2, X2, where Y1 is in the most significant byte. The pair Y1, X1 is the position of the cursor before writing and Y2, X2 is where the cursor will be positioned after writing. The upper four bits of Y2 specify whether the cursor will be left on (1) or off (0) after the print is complete. If \*fmt is a null string, then only cursor positioning will take place.

Lines on a  $2 \times 20$  screen (Y values) are numbered 0 and 1. Columns (X values) are numbered 0...19. A screen with four lines has lines numbered 0–3.

The function <code>lcd\_printf</code> is not reentrant. If it is used in a multitasking environment, it is necessary to restrict <code>lcd\_printf</code> to only one task at a time. Several utility routines make this possible.

The following routines save and restore the contents of the liquid crystal display screen. The program must "have the token" to use these routines in a multitasking environment.

```

lcd_savscrn( struct lcd_scrn *s )

lcd resscrn( struct lcd_scrn *s )

```

The following routines erase the screen or a line on the screen. The user must "have the token" to call these routines in a multitasking environment.

```

lcd_erase()

lcd erase line( int line )  // line is 0 or 1

```

A copy of the display contents and the location of the cursor is updated in memory whenever lcd\_printf prints to the liquid crystal display. The function lcd\_savscrn copies this image to a user-specified save area. The function lcd\_resscrn copies the screen save area back to the screen and the image copy. A task can use these routines to interrupt another task using the liquid crystal display, save the image, use the liquid crystal display, restore the image, and return the liquid crystal display to the original task.

#### Virtual Driver Variables

The variables described here are defined in **CPLC.LIB**. The virtual driver updates the input variables every 25 milliseconds to reflect the state of the hardware inputs and sets the hardware outputs based on the state of its output variables.

The virtual driver does not change input variables unless the hardware input has the same value for at least two ticks of the virtual driver.

## **Digital Outputs**

The 10 digital outputs and the two relay outputs are represented by the following variables:

```

RELAY1, RELAY2

OUT1, OUT2...OUT9, OUT10

```

Storing a 1 in these variables causes the corresponding output to be energized on the next virtual driver tick. Storing a 0 clears the corresponding output.

## Digital Inputs

Seven variables represent the seven digital inputs:

```

DIGIN1, DIGIN2...DIGIN6, DIGIN7

```

These variables are updated every virtual driver tick (25 ms). They are set to either 1 or 0 depending on the state of the physical input. A 1 corresponds to an input value of at least 2.5 volts.

## Universal Inputs

The universal inputs are represented by these variables:

```

U1IN, U2IN, U3IN, U4IN, U5IN, U6IN

```

They are updated to 1 or 0 depending on the relationship of the analog input to preset thresholds.

A high threshold and a low threshold are associated with each universal input variable. These are the levels at which the flags **U1IN**, **U2IN**, . . . are switched.

```

U1LOW, U1HIGH, U2LOW, U2HIGH, ... U6LOW, U6HIGH

```

The way the universal inputs are interpreted is determined by setting these thresholds.

#### **Timers**

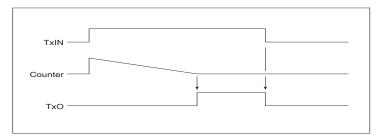

There are 10 virtual timers. Each timer has an input flag, an output flag, and a reload value.

```

T1IN, T2IN ... T10IN // input flags

T1O, T2O ... T10O // output flags

T1RLD, T2RLD ... T10RLD // reload values

```

When a timer input (for example, **T1IN**) goes from 0 to 1, the counter starts counting from the reload value (for example, **T1RLD**) down, one count every virtual driver tick (25 milliseconds). The output flag (**T10**) is set to 1 when the count reaches zero. The output is forced to zero whenever the input is set to zero.

Figure 4-1. Timer Ouput Variation Over Time with Timer Input and Counter

# **Downloading Code**

A program may be downloaded to the PK2100 via a serial or other communications link. A related problem is loading programs to EPROM, RAM, or an external mass storage device for execution.

The basic method for downloading starts with writing a *monitor* program that is burned into EPROM. This monitor program serves as a master controller to load and start execution of the programs and to regain control when the executed program finishes.

The monitor program must also gain control when the board is reset through hardware, either by power-on, watchdog time-out, or the reset key. An external hardware reset line may be installed to allow the computer that is downloading the program to be able to force a hardware reset of the PK2100. Connect Pins 2 and 3 on Jumper J11 to use the CTS0 line from the 6-pin phone jack to control external resetting of the PK2100. However, the handshaking line for the RS-232 port will be lost. To be safe, tie the /CTS0 line of the RS-232 port to ground to continue to use the RS-232 port for communication.

Refer to the Dynamic C manual for a discussion on memory mapping and remote downloading and execution of code.

# **Direct Programming of the Serial Ports**

The *Z180 Technical Manual* and the *Z80 SIO Technical Manual*, available from Zilog, Inc., in Campbell, California, provide detailed information to plan extensive use of the serial ports and synchronous communications. Z-World provides just a few low-level utility functions:

```

int sysclock()

int z180baud( int clock, int baud )

```

The **sysclock** function returns the clock frequency in units of 1200 Hz, as read from the EEPROM. The clock frequency was stored at location 108H at the factory. The **z180baud** function returns the byte to be stored in **CNTLB0** or **CNTLB1**, considering only the bits needed to set the baud rate. The clock and baud rate must be specified in units of 1200 Hz. Thus, a 9.216-MHz clock is expressed by 7680, and 19,200 baud is expressed by 16. The return value is -1 if the baud value cannot be derived from the given clock frequency.

Each serial port appears to the CPU as a set of registers. Each serial port can be accessed directly with the **inport** and **outport** library functions, using the symbolic constants for Address 00–09 in Table D-1, Appendix D.

For example, to read and write from serial port 0:

```

char ch;

ch = inport( RDR0 );

outport( TDR0, ch );

```

Ports may be polled or interrupt-driven. The interrupt vectors are given in Table D-4, Appendix D.

#### Attainable Baud Rates

The serial ports built into the Z180 can generate standard baud rates when the clock frequency is 6.144 MHz or 9.216 MHz or a small multiple, for example, 3.072, 4.608, 6.144, 9.216, or 12.288 MHz. A crystal is stamped with twice the clock frequency.

#### 7180 Serial Ports

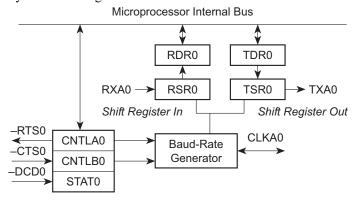

The Z180 has two independent, full-duplex asynchronous serial channels, with a separate baud-rate generator for each channel. The baud rate can be divided down from the microprocessor clock or from an external clock for either or both channels.

The serial ports have a multiprocessor communications feature that can be enabled. When enabled, an extra bit is included in the transmitted character (where the parity bit would normally go). Receiving Z180s can be programmed to ignore all received characters except those with the extra multiprocessing bits enabled. This provides a 1-byte attention message that can be used to wake up a processor without the processor having to monitor (intelligently) all traffic on a shared communications link.

Figure 4-2 shows the configuration for Serial Channel 0. The configuration for Serial Channel 1 is similar, but modem control lines –RTS1 and –DCD0 are not available. Five of the seven registers shown are accessible directly as internal registers.

Figure 4-2. Z180 Serial Channel 0 Configuration

The serial ports may be polled or interrupt-driven. A polling driver tests the ready flags (TDRE and RDRF) until a ready condition appears (transmitter data register empty or receiver data register full). If an error condition occurs on receive, the routine must clear the error flags and take any appropriate action. If the –CTS line is used for flow control, transmission of data is automatically stopped when –CTS goes high because the TDRE flag is disabled. This prevents the driver from transmitting more characters, because it thinks the transmitter is not ready. The transmitter will still function with –CTS high, but care must be exercised since TDRE is not available to synchronize the loading of the data register (TDR).

An interrupt-driven driver works with the program enabling the receiver interrupt as long as it wants to receive characters. The transmitter interrupt is enabled only while characters are waiting in the output buffer. When an interrupt occurs, the interrupt routine must determine the cause: receiver data register full, transmitter data register empty, receiver error, or –DCD0 pin high (channel 0 only). None of these interrupts is edgetriggered. Another interrupt will occur immediately, if the interrupts are re-enabled without disabling the condition causing the interrupt. The signal –DCD0 is especially treacherous because it cannot be disabled when the receive interrupts are on. In most designs, the –DCD0 line should be connected directly to ground, thus taking it out of the picture.

# SOFTWARE REFERENCE

Chapter 5 presents information on the Dynamic C software drivers and communication software for the PK2100.

### **Driver Software**

Drivers in the Dynamic C software library make it easy to communicate with the PK2100 inputs and outputs. Drivers may be *direct* or *indirect*. A direct driver immediately reads or writes to the controlled hardware. An indirect driver uses intermediate variables. Z-World's *virtual driver* is a periodically called interrupt service routine that connects the hardware with intermediate variables.

Drivers may be low-level drivers that return, send, or transmit values when the values are received or presented by the interface. High-level drivers modify the inputs or outputs in some way, such as by introducing calibration, hysteresis or averaging. Indirect, high-level drivers are preferred because they eliminate any concern about the technical details of the input/output interface. The price for this convenience is a slight loss of speed and efficiency.

#### Digital Input

#### **Direct Driver**

• int up digin( int channel )

Gets the value at the specified digital input channel (1-7). The function returns 1 when the channel is high and 0 when the channel is low.

#### Virtual Driver

Reference the parameters DIGIN1, DIGIN2, DIGIN3, DIGIN4, DIGIN5, DIGIN6, and DIGIN7. For example,

```

heater = DIGIN1 || DIGIN2;

```

These variables take the value 1 if the input is high (greater than 2.5 volts) and 0 if the input is low. The parameter value changes only if the new value remains the same for 2 ticks (25–50 ms) of the virtual driver.

## Digital Output

#### **Direct Driver**

• int up\_setout( int channel, int value )

Passes channel number 1–10 and value 0 for "OFF," 1 for "ON." If

channel is 11 or 12, relay 1 or 2 is switched.

#### **Indirect Driver**

Set the variables **OUT1**, **OUT2**, **OUT3**, ... **OUT9**, **OUT10** to a value of 0 to turn the output off, or to a value of 1 to turn the output on. Outputs pull low when turned on. The variables **RELAY1** and **RELAY2** control the relay contacts.

## Analog Input

The A/D system relies on software calibration, using calibration constants stored in the system EEPROM. Uncalibrated values are in the range 0–1023, with each count representing approximately 10 millivolts. Calibrated values are kept on a scale 0–10,000, with each count representing 1 millivolt, or in the case of the single high-gain input, 0.1 millivolt. Since it requires about 200 milliseconds to convert an uncalibrated value to a calibrated value or vice versa, preliminary data storage or averaging may be done using uncalibrated values to save computing time. The following utility routines convert back and forth between uncalibrated and calibrated values.

#### Low-Level Direct Driver

#### int up\_adrd( int channel )

Returns a 10-bit uncalibrated value scaled so that 1023 corresponds to full scale (10 volts). The conversion time is less than 200 milliseconds. Each count represents approximately 10 millivolts.

The channel may be 1–8. Channels 1–6 are universal inputs. Channel 8 may be used as a universal input unless it is used with the high-sensitivity input, Channel 7.

#### **Calibrated Direct Driver**

# int up\_adcal( int channel )

Returns a voltage value scaled so that the value 10,000 represents 10 volts. The calibration applied considers the actual value of the voltage reference and the nonlinearity of UEXP. The calibration for the high-sensitivity input, Channel 7, is such that 10,000 equals 1 volt. (Values slightly less than 0 and slightly over 10,000 are possible.)

## int up\_in420()

Returns the current flowing through universal Channel 6 when subjected to a current input. The function returns 1000 for each milliampere. The maximum value is approximately 25,000. Jumper H6-6 must be connected to H5-6 and Jumper H5-7 must be connected to H5-8 to place a load resistor equivalent to 392  $\Omega$  in the circuit. The driver must be able to deliver an input voltage of about 8 volts to achieve 20 milliamps.

#### • int up adtest( int channel, int testval )

Returns 1 if external voltage is greater than test value expressed as an uncalibrated 0–1023 value. Use up\_uncal routine to compute test value. For example up\_adtest(2,up\_uncal(2600)) returns 1 if the Channel 2 input is greater than 2.60 volts.

#### • int up uncal( int calval )

Returns uncalibrated value 0–1023 given calibrated value in millivolts, 0–10,000. This function is used to generate a raw threshold value, corresponding to a calibrated value, for use with the universal input channels and the high-gain channel.

#### • up docal (int calval)

Generates calibrated value 0–10,000 millivolts given uncalibrated value 0–1023. This can be used with up\_adrd(channel) when data are collected in uncalibrated form.

#### • float up higain (int mode)

Returns a value from the high-gain differential analog input. There are three modes of operation, all of which assume Jumper H7 is removed. Mode 1 assumes AD– is grounded and returns voltage on AD+ in the range 0–1 volts. Mode 2 returns the difference voltage ( (AD+) – (AD–) ). The possible voltage range depends on the common-mode voltage, varying from 0–1 volts when AD– is at ground, from –0.5 to +0.5 volts when AD– is at -0.5 volts, and from -1 to 0 volts when AD– is at -1.0 volt. Mode 3 returns the input voltage on AD+ in the range 0–10 volts. The function returns the input voltage at AD+ if the output of the amplifier is out of range.

## **Virtual Driver for Universal Inputs**

The virtual driver assesses the state of universal inputs 1–6. Each of these channels has a high and low threshold, and a flag to indicate the relationship of the incoming signal to the thresholds.

The incoming analog signal is compared with the high and low threshold every tick of the virtual driver (25 milliseconds). For example, the flag U1IN is set to 1 if the signal on Channel 1 is above the high threshold, and is set to 0 if the signal is below the low threshold. The flag is not altered when the signal is in the hysteresis region. In addition, the flag is not altered unless the new condition that requires the flag to be altered persists for two clock ticks (25–50 milliseconds). A program such as the one in the following example can set the thresholds to any desired level and then check the associated flag.

This relationship is shown in Figure 5-1 for Channel 1.

Note that the thresholds are expressed as raw (uncalibrated) values. This saves computation time in the interrupt routine. Use the routine up\_uncal to compute the raw values from the desired calibrated values.

Figure 5-1. Universal Input Hysteresis

# **Analog Output**

Analog output consists of the DAC output channel, which can be set up as either a current or a voltage output. There is also an option for the UEXP output to be used as a voltage DAC output if the universal input is configured as a digital-only input. Only direct drivers are available for analog output.

#### **Direct Driver**

• void up\_daccal ( int value )

Sends a calibrated value to the DAC output channel. A calibrated voltage is a value expressed in millivolts. (10,000 for 10 volts).

void up dacout ( int rawval )

Sends a raw value to the DAC output channel. Each count represents an increment of 0.01 volts over the count range 0–1023.

#### void up\_dac420( int current )

Sends a current value to the DAC output channel. The current is specified such that 1000 = 1 milliamp. The maximum is 20,000 or 20 milliamps. Pins 1-2 on Jumper J7 must be connected for current output. The maximum output is approximately 12 volts.

#### • void up expout ( int rawval )

Sends a raw value to UEXP, the internal D/A converter. Use this function primarily for testing and calibration since, in most cases, UEXP is subject to constant manipulation by interrupt routines. Use

```

up expout( up docal(value) );

```

to output a calibrated value expressed in millivolts.

#### Virtual Driver

The virtual driver does not perform analog output.

## High-Speed DMA Counter

The two DMA channels are used as high-speed counters, and are capable of counting up to 600 kHz. Function calls load the countdown value for the DMA channel and enable the DMA interrupt. Flags for the DMA channel are set to 1 once a counter reaches zero. A program can monitor these flags.

#### • void DMA0Count( uint count )

Loads the DMA channel 0 with the count value and enables the DMA Channel 0 interrupt. The function sets the flag \_DMAFLAGO to zero. When count negative edges have been detected, the channel will cause an interrupt and the interrupt service routine will set the flag \_DMAFLAGO to 1. A program can monitor \_DMAFLAGO to determine if the number of counts has occurred.

#### • void DMA1Count( uint count )

Loads DMA Channel 1 with the count value and enables the DMA Channel 1 interrupt. The function sets the flag \_\_DMAFLAG1 to zero. When count negative edges have been detected, the channel will cause an interrupt, and the interrupt service routine will set the flag \_\_DMAFLAG1 to 1. A program can monitor \_\_DMAFLAG1 to determine if the number of counts has occurred.

#### uint DMASnapShot( byte channel, uint \*counter )

This function reads the number of pulses that a DMA channel (0 or 1) has counted. A DMA counter is initialized with one of the two preceding functions. The function returns 0 if a DMA channel is counting too fast to allow for stable reading of the count value. If the function reads a stable count value, it returns 1 and sets the parameter count. Note that DMA interrupts will still occur when the DMA channel counts down from its loaded value even if the counts cannot be read.

For example,

The program **DMACOUNT**. **C** in the subdirectory **SAMPLES\CPLC** illustrates the use of these DMA functions.

# Battery-Backed Clock

The battery-backed clock, Toshiba part number TC8250, retains the time and date with a resolution of one second, and an accuracy of about one second per day. It automatically accounts for leap year.

The following structure is used to hold the time and date:

The following routines read and write the clock:

```

int tmc_wr( struct tm *x );  // write the clock

int tmc rd( struct tm *x );  // read the clock

```

The following routines convert the time to and from a long integer. The long-integer format represents the number of seconds that have passed since midnight (00:00:00), January 1, 1980.

```

// return long seconds from structure

long mktime( struct tm *t );

// return structure from long seconds

int mktm( struct tm *t, long time );

```

The long-integer format is easier for making comparisons. It represents time until 12:00 midnight, December 31, 1999.

The real-time clock can also be programmed to interrupt the processor periodically through the INT2 interrupt line. The Toshiba TC8250 data book contains further details.

## Liquid Crystal Display and Keypad

The library **CPLC.LIB** includes functions for writing to the LCD and "reading" the keypad. There is a 16-element keypad buffer.

## • void lc\_char( char ch )

Sends a character to the LCD. The function waits for the LCD to become free before sending the character.

## int lc\_cmd( int cmd )

Sends a 1-byte command to the LCD. The function waits for the LCD to become free before sending the command. If the LCD does not become free within a certain time (5,000 attempts to write), the function returns –1. Otherwise, it returns 0, indicating success.

# void lc\_ctrl( byte cmd )

Sends a 1-byte command to the control register of the LCD. The function waits for the LCD to become free (not busy) before writing.

# void lc\_init()

Initializes the LCD. The display is turned on, cleared, and the cursor (now in the top left character position) blinks.

# void lc\_init\_keypad()

Initializes the keypad, timer1 and the real-time kernel (if it is in use).

### • void lc init timer1( uint count )

Initializes the timer reload register. The term **count** is expressed as shown below for the 6.144-MHz clock.

| count | Frequency | Period  |

|-------|-----------|---------|

| 192   | 1600 Hz   | 625 μs  |

| 384   | 800 Hz    | 1.25 ms |

| 6144  | 50 Hz     | 20 ms   |

In other words, **count** = clock speed  $(20 \times \text{frequency})$ .

#### • int lc kxget( byte mode )

Gets the current entry from the keypad buffer. If **mode** is 0, the byte pointer is advanced. Otherwise, it remains at the current byte.

The function returns an integer representing which key was pressed. Numbers from 0–11 are returned for a  $2 \times 6$  keypad.

The function returns -1 if the buffer is empty.

#### void lc\_kxinit()

Initializes the keypad. The virtual watchdogs are initialized if virtual watchdogs are defined (see the *virtual driver*).

### • void lc nl()

Performs a newline on the LCD.

# void lc\_pos( int line, int column )

Positions the cursor at line (0, 1, ...) and column (0, 1, 2, 3, ...).

# • void lc\_printf( char\* fmt, ...)

Perform a **printf** on the LCD. The function arguments are specified as they are for the standard **printf**.

# • void lc\_setbeep( int count )

Sounds the beeper for the number of 2560-Hz cycles specified by count.

• void lc wait()

Waits for the LCD to become free (i.e., not busy).

#### EEPROM Read / Write

• int ee rd( int address )

Reads EEPROM at specified address and returns result in lower byte. Returns –1 if EEPROM is not functioning.

• int ee\_wr( int address, char data )

Writes character data at address in EEPROM. Returns –1 if EEPROM is not functioning.

• int eei rd( int address )

Reads EEPROM integer (2 bytes, least significant byte first) at address specified. Does not return a distinct error code if EEPROM fails.

#### Flash EPROM Write

int WriteFlash( ulong addr, char\* buf, int num )

Writes num bytes from buf to flash EPROM, starting at addr. The term addr is an absolute physical address.

To do this with Dynamic C, allocate flash data in Dynamic C by declaring *initialized* variables or arrays, or initialized **xdata**. The data name for **xdata** must be passed directly to the function

```

xdata my_data { 0, 0xFF, 0x08 };

. . . .

WriteFlash { my_data, my_buffer, my_count };

For normal data, pass the physical address of the data to the function

```

```

char xxx[ ] = { 0, 0xFF, 0x08 };

. . .

```

WriteFlash { phy\_adr(xxx), my\_buffer, my\_count };

The function returns

- 0 if the operation is successful,

- -1 if no flash EPROM is present,

- -2 if a physical address is within the BIOS area,

- -3 if a physical address is within the symbol table, or

- -4 if the write times out.

The data are placed in RAM, not ROM, when some form of initialization is not included when the data are declared. The function then will not work.

It may seem to be contradictory to write to ROM, but this is possible with flash EPROM, where the flash memory is treated as nonvolatile memory.

Flash EPROM is rated for 10,000 writes. Z-World's experience has been that flash EPROM seems to last for at least 100,000 writes. Nevertheless, there is a limit after which the flash EPROM chip will need replacement.

### Communication

#### RS-232 Communication

Z-World has RS-232 support libraries for the Z180 port 0, and for the RS-232 expansion card that interfaces through the PLCBus to the PK2100. Functional support for serial communication includes the following functions:

- Initialization of the serial ports.

- Monitoring and reading a circular receive buffer.

- Monitoring and writing to a circular transmit buffer.

- · An echo option.

- CTS (clear to send) and RTS (request to send) control.

- XModem protocol for downloading and uploading data.

- · A modem option.

# Support Libraries and Sample Programs

Dynamic C provides subdirectories with libraries and software samples. Table 5-1 lists and describes libraries of use to the PK2100 in the LIB subdirectory.

Table 5-1. PK2100 Support Libraries

| Library      | Description                                                                                                                                           |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Z0232.LIB    | RS-232 library for the Z180 port 0.                                                                                                                   |

| MODEM232.LIB | Miscellaneous functions common to the other communication libraries.                                                                                  |

| UART232.LIB  | RS-232 library for the RS-232 expansion card.                                                                                                         |

| NETWORK.LIB  | RS-485 9-bit binary half-duplex support for master/slave communication for Z180 port 1.                                                               |

| CPLC.LIB     | Low-level drivers for the PK2100. Includes drivers for the real-time clock, LCD, keypad, virtual drivers, DAC, A/D, digital input and digital output. |

| 5KEY.LIB     | Driver for the five-key system.                                                                                                                       |

| 5KEYEXTD.LIB | Drivers for input/output display under the five-key system.                                                                                           |

| GATE_P.LIB   | Drivers for gate programming.                                                                                                                         |

Table 5-2 lists and describes sample programs of use to the PK2100 in the **SAMPLES\CPLC** subdirectory.

Table 5-2. Sample Programs in SAMPLES\CPLC

| Program    | Description                                                                                  |

|------------|----------------------------------------------------------------------------------------------|

| 5KEYCODE.C | Code-driven sample program for the five-key system.                                          |

| 5KEYDEMO.C | Uses a code-driven five-key system and the RTK for I/O monitor and control.                  |

| 5KEYLAD.C  | Combines 5KEYCODE.C and LADDERC.C.                                                           |

| 5KEYLINK.C | Linked-list sample program for the five-key system.                                          |

| 5KEYSCAN.C | Combines 5KEYCODE.C and SCANBLK.C.                                                           |

| ADCDEMO.C  | Use keypad to select which ADC channel to monitor.                                           |

| CDEMO_RT.C | Demonstrate the use of the real-time kernel.                                                 |

| DACDEMO.C  | Use keypad to select output voltage on the DAC.                                              |

| DIGDEMO.C  | Use the keypad to select which digital input channel to monitor.                             |

| DIGVDVR.C  | Similar to <b>DIGDEMO.C</b> , but uses the virtual driver to monitor the state of the input. |

| DMACOUNT.C | Demonstrates the use of the high-speed counters.                                             |

| GATER.C    | Elaborate program using ladder C or gate programming to control and monitor the I/Os.        |

| OUTDEMO.C  | Use the keypad to toggle the state of the digital outputs.                                   |

| OUTVDVR.C  | Similar to <b>OUTDEMO.C</b> , but uses the virtual driver to change the state of the output. |

| PRT0DEMO.C | Use <b>TIMER0</b> for interrupt timer.                                                       |

| READIO.C   | Read and toggle the I/Os through STDIN. The I/Os are driven by function calls.               |

| READKEY.C  | Read the keypad and write to the LCD and to the STDIO window.                                |

| SCAN.C     | Elaborate program using function blocks or gate programming to control and monitor the I/Os. |

| SCANBLK.C  | Use function blocks for I/O control.                                                         |

| UINVDVR.C  | Use the virtual driver to monitor the universal inputs.                                      |

| UREADIO.C  | Read and toggle the I/Os through <b>STDIN</b> . The virtual driver drives the I/Os.          |

| VWDOG.C    | Illustrates the use of the virtual watchdogs and of KEYREQUEST.                              |

Table 5-3 lists and describes sample communication programs in the **SAMPLES\NETWORK** subdirectory.

Table 5-3. Sample Communication Programs in SAMPLES\NETWORK

| Sample     | Description                                                                                                                                                                                                                                                                                                                                                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RS232.C    | RS-232 communication with a PC dumb terminal, with or without a modem. Also, master-to-slave communication with another board running RS485.C.                                                                                                                                                                                                                                  |

| RS485.C    | Slave program to communicate with the master running RS232.C.                                                                                                                                                                                                                                                                                                                   |