# **125 Series** Wi**125**

2111 Comprehensive Drive

Aurora, Illinois 60505

Phone: 630-851-4722

Fax: 630-851-5040

www.conwin.com

D

$\Lambda$

П

Δ

S

Н

Ε

Т

| Bulletin | SG170        |

|----------|--------------|

| Page     | 1 of 20      |

| Revision | 02           |

| Date     | 16 June 2010 |

# **TABLE OF CONTENTS**

| 1      | INT                                           | RODUCTION                                                                                                                  | 4                    |

|--------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2      | SPE                                           | CIFICATION                                                                                                                 | 6                    |

|        | 2.1<br>2.2<br>2.3<br>2.4                      | Performance                                                                                                                | 7<br>7               |

| 3      |                                               | SICAL CHARACTERISTICS                                                                                                      |                      |

|        | 3.1<br>3.2<br>3.3                             | Physical Interface Details Wi125 Dimensions Solder Pad Size and Placement                                                  | 8<br>9               |

| 4      | SIGI                                          | NAL DESCRIPTION                                                                                                            |                      |

|        | 4.1<br>4.2<br>4.3<br>4.4<br>4.5               | Power Signals  RF Signals  Emulation/Test Signals  Control Signals  I/O Signals                                            | 12<br>12<br>13       |

| 5      | SPE                                           | CIAL FEATURES                                                                                                              | 15                   |

|        | 5.1<br>5.2<br>5.3                             | User Commands Self-Survey Wi125 Embedded Identification                                                                    | 15                   |

| 6      | TAP                                           | E AND REEL SPECIFICATIONS                                                                                                  | 16                   |

| 7<br>8 |                                               | DER PROFILEPLICATION HINTS                                                                                                 |                      |

| •      | 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7 | Power Supply  RF Connection  Grounding  Battery Backup  Over Voltage & Reverse Polarity Protection  LEDs  Reset Generation | 17<br>18<br>19<br>19 |

|        | 8.8                                           | Boot Options                                                                                                               | 19                   |

# Figure and Table Contents

# **List of Figures**

| Figure 1 Wi125 Block Diagram                     | 7  |

|--------------------------------------------------|----|

| Figure 2 Wi125 Form and Size                     | 8  |

| Figure 3 Wi125 Dimensions                        | 9  |

| Figure 4 Solder Pad Size and Placement           | 10 |

| Figure 5 RF Tracking Example                     | 17 |

| Figure 6 Grounding the Wi125 with a ground plane | 18 |

| Figure 7 Typical VBATT Supplies                  | 19 |

|                                                  |    |

| List of Tables                                   |    |

| Table 1 Revision History                         | 2  |

| Table 2 Additional Documentation List            | 3  |

| Table 3 Wi125 Specification                      | 6  |

| Table 4 Absolute Maximum Ratings                 | 7  |

| Table 5 Absolute Maximum Ratings                 | 7  |

| Table 6 Wi125 Signal List                        | 8  |

| Table 7 RF Track & Gap Widths                    | 17 |

# **Revision History of Version 1.0**

| Revision | Date     | Released By    | Note                                           |

|----------|----------|----------------|------------------------------------------------|

| 00       | 07/20/09 | Keith Loiselle | New Release of Wi125 Data Sheet                |

| 01       | 04/13/10 | Dave Jahr      | Update to 1PPS (timing) Accuracy Specification |

| 02       | 06/16/10 | Dave Jahr      | 125 Series Revised                             |

**Table 1 Revision History**

## **Other Documentation**

The following additional documentation may be of use in understanding this document.

| Document                  | Ву              | Note |

|---------------------------|-----------------|------|

| Wi125 User Manual         | Connor-Winfield |      |

| Wi125 Dev Kit User Manual | Connor-Winfield |      |

**Table 2 Additional Documentation List**

### 1 INTRODUCTION

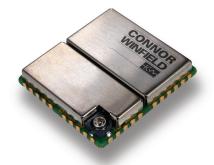

The 125 Series Wi125 is a small OEM surface mount GPS module specifically designed for use in synchronization and timing in WiMax applications. This compact module has an onboard programmable NCO oscillator that outputs a synthesized frequency up to 30 MHz that is steered by a GPS receiver. The self-survey mode of operation allows the receiver to enter a position hold mode allowing accurate timing to be continued with only one satellite being tracked.

Additionally, the 125 Series Wi125 has phase alignment of 1 PPS/10 MHz with a very stable holdover. The 1 PPS/10 MHz outputs maintain phase alignment with holdover being base only on the local oscillator, dismissing spurious GPS measurements during reacquisition. When the receiver regains GPS lock after a period of holdover, the 1PPS and 10 MHz outputs maintain phase alignment and are offset in frequency at the maximum rate of 100 ppb until the 1 PPS aligns with that of the GPS solution. This slow recovery from holdover allows for uninterrupted operation of the WiMax base station.

The Wi125 has a highly accurate output frequency, which can achieve full PRC MTIE performance. Additionally it can track satellites and provide GPS synchronization in weak signal areas including indoor applications, reducing the need for high antenna placement.

The Wi125 is an exceptionally small surface mount package with a highly integrated architecture that requires a minimum of external components allowing easy integration into host systems.

## Key information includes:

- System Block Diagram

- Maximum Ratings

- Physical Characteristics Wi125 Dimensions, castellation information Solder Pad and placement information

- Signal Descriptions

- Special Features

- Application Information

Power supply modes

RF connections

Grounding

Battery Back-up

Over Voltage and Reverse Polarity

LED's

#### **Features**

- 1PPS/ 10 MHz Phase alignment

- Stable Holdover

- Holdover Recovery

- 1 PPS & NCO Frequency Output

- GPS/UTC time/scale synchronization to 25 ns RMS

- Stable proven design with long term availability and multi-year support

- 12 channel hardware correlator processor design

- OEM SM footprint 25 x 27 mm

- Automatic entry into holdover

- Loss-of-lock and entry-into-holdover indication

The specifications in the following sections refer to the standard software builds of the Wi125. The performance and specification of the Wi125 can be modified with the use of customized software builds.

# 2 SPECIFICATION <sup>1</sup>

## 2.1 Performance

| Physical    | Module dimensions             | 25mm (D) x 27mm (W) x 4.2mm (H)                            |

|-------------|-------------------------------|------------------------------------------------------------|

| . Hyolodi   | Supply voltages               | 3V3 (Digital I/O), 3V3 (RF), 1V8 (Core option), 3V         |

|             | 11,7                          | (Standby Battery)                                          |

|             | Operating Temp                | -30°C to +85°C                                             |

|             | Storage Temp                  | -40°C to +85°C <sup>2</sup>                                |

|             | Humidity                      | 5% to 95% non-condensing                                   |

|             | Max Velocity / Altitude       | 515ms <sup>-1</sup> / 18,000m                              |

|             | Max Acceleration / Jerk       | 4g / 1gs <sup>-1</sup> (sustained for less than 5 seconds) |

| Sensitivity | Acquisition w/network assist  | -185dBW                                                    |

|             | Tracking                      | -186dBW                                                    |

|             | Acquisition Stand Alone       | -173dBW                                                    |

| Acquisition | Hot Start with network assist | Outdoor: <2s                                               |

| Time        |                               | Indoor (-178dBW): <5s                                      |

|             | Stand Alone (Outdoor)         | Cold: <45s                                                 |

|             |                               | Warm: <38s                                                 |

|             |                               | Hot: <5s                                                   |

|             |                               | Reacquisition: <0.5s (90% confidence)                      |

| Accuracy    | Position: Outdoor / Indoor    | <5m rms / <50m rms                                         |

|             | Velocity                      | <0.05ms <sup>-1</sup>                                      |

|             | Latency                       | <200ms                                                     |

|             | Raw Measurement Accuracy      | Pseudorange <0.3m rms, Carrier phase <5mm rms              |

|             | Tracking                      | Code and carrier coherent                                  |

| Power       | 1 fix per second              | 0.6W typically                                             |

|             | Coma Mode Current             | 10mA                                                       |

|             | (RF3V3+DIG 3V3)               |                                                            |

|             | Standby Current (VBATT)       | 1.5μΑ                                                      |

| Interfaces  | Serial                        | 3 UART ports, CMOS levels                                  |

|             | Multi-function I/O            | 1PPS and Frequency Output available on GPIO [0]            |

|             |                               | Event Counter/Timer Input                                  |

|             |                               | Up to 4 x GPIO (multi-function)                            |

|             |                               | 2 x LED Status Drive                                       |

|             |                               | I <sup>2</sup> C, External Clock (on special build)        |

|             | Protocols                     | Network Assist, NMEA 0183, Proprietary ASCII and           |

|             |                               | binary message formats                                     |

|             | 1pps Timing Output            | 10nS rms accuracy, <5nS resolution                         |

|             |                               | User selectable pulse width                                |

|             | Event Input                   | 30nS rms accuracy, <10nS resolution                        |

|             | Frequency Output (GPIO [0])   | 10 Hz to 30 MHz (Wi125)                                    |

|             | Receiver Type                 | 12 parallel channel x 32 taps up to 32 point FFT.          |

|             |                               | Channels, taps and FFT can be switched off to              |

|             |                               | minimize power or simulate simpler designs.                |

| General     | Processor                     | ARM 966E-S on a 0.18µ process at up to 120 MHz.            |

Note: 1. The features listed above may require specific software builds and may not all be available in the initial release.

Table 3 Wi125 Specification

<sup>2.</sup> Please contact factory for other temperature options.

## 2 SPECIFICATION continued

# 2.2 Recommended Ratings

| Symbol     | Parameter              | Min   | Max   | Units |  |

|------------|------------------------|-------|-------|-------|--|

| RF_3V3     | RF Supply Voltage      | +3.0  | +3.6  | Volts |  |

| DIG_3V3    | Digital Supply Voltage | +3.0  | +3.6  | Volts |  |

| DIG_1V8    | Digital Supply Voltage | +1.65 | +1.95 | Volts |  |

| VBATT      | Battery Backup Voltage | +2.7  | +3.5  | Volts |  |

| ANT_SUPPLY | Antenna Supply Voltage | +3.0  | +12   | Volts |  |

Table 4 Recommended Maximum Ratings

# 2.3 Absolute Maximum Ratings

| Symbol     | Parameter                     | Min  | Max  | Units |  |

|------------|-------------------------------|------|------|-------|--|

| RF_3V3     | RF Supply Voltage             | -0.3 | +6.5 | Volts |  |

| DIG_1V8    | Digital Supply Voltage        | -0.3 | +2.0 | Volts |  |

| DIG_3V3    | Digital Supply Voltage        | -0.3 | +3.7 | Volts |  |

| VBATT      | Battery Backup Voltage        | -0.5 | +7.0 | Volts |  |

| ANT_SUPPLY | Antenna Supply Voltage        | -15  | +15  | Volts |  |

| DIG_SIG_IN | Any Digital Input Signal      | -0.3 | +5.5 | Volts |  |

| RF_IN      | RF Input                      | -15  | +15  | Volts |  |

| TSTORE     | Storage temperature           | -40  | +85  | °C    |  |

| IOUT       | Digital Signal Output Current | -6   | +6   | mA    |  |

Table 5 Absolute Maximum Ratings

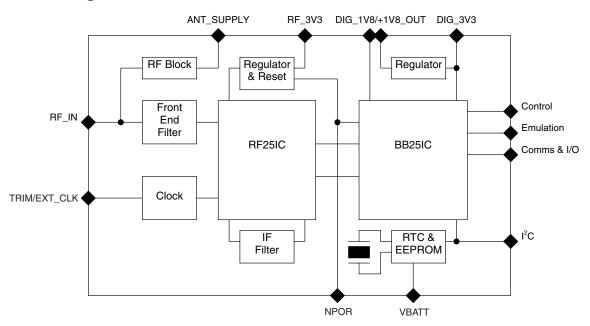

## 2.4 Block Diagram

Figure 1 Wi125 Block Diagram

## **3 PHYSICAL CHARACTERISTICS**

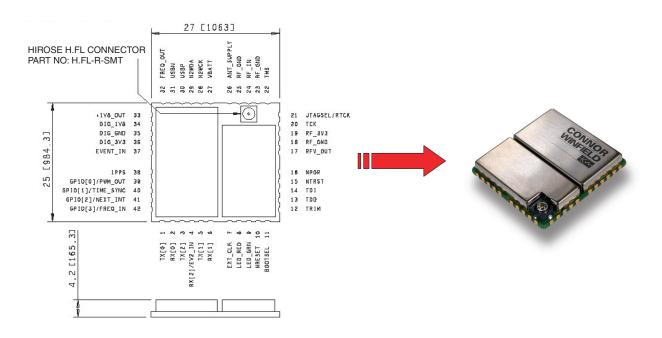

The 125 Series Wi125 is a multi-chip module (MCM) built on an FR4 fiberglass PCB. All digital and power connections to the Wi125 are via castellations on the 25 x 27 mm PCB. The RF connection is via castellations or an RF connector. The general arrangement of the Wi125 is shown in the diagram below. Dimensions are in mm (inches/1000).

Figure 2 Wi125 Form and Size

## 3.1 Physical Interface Details

The interface to the Wi125 is via 1mm castellations on a 2mm pitch. There are 42 connections in all. There is also an RF connector for connecting to the GPS antenna. The details of the interface connections are given below.

Note: 3. Frequency Output is available on pin 32 (FREQ\_OUT) with custom software only.

Table 6 Wi125 Signal List

### 3 PHYSICAL CHARACTERISTICS continued

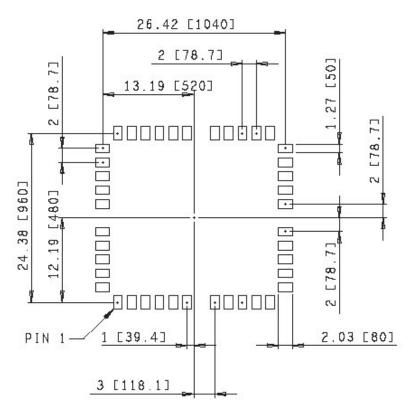

### 3.2 Wi125 Dimensions

The figure below provides the dimensions of the positioning of the Wi125 castellations. Dimensions are in mm (inches/1000).

Figure 3 Wi125 Dimensions

## 3.3 Solder Pad Size and Placement

It is recommended that the footprint of the solder pad under each castellation be 2mm x 1mm, centered on the nominal centre point of the radius of the castellation. The castellations are gold plated and so are lead free. Note that if the RF IN connector is being used, there should not be a pad or solder resist under the RF IN castellation. If the RF\_IN castellation is to be used, the pad should be shortened by 0.5mm underneath the Wi125 and standard RF design practices must be observed. The diagram below shows the placement of the pads under the castellations.

Figure 4 Solder Pad Size and Placement

# **4 SIGNAL DESCRIPTION**

The signals on the Wi125 are described in the table below.

# 4.1 Power Signals

| RF_3V3      | Type: Power                                                          | Direction: Input                                                   | Pin: 19                                                                                                                        |

|-------------|----------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|             | section of the Wi125                                                 |                                                                    | s the 2.9V LDO regulator in the RF is well filtered with no more that                                                          |

| _RF_GND     | Type: Power                                                          | Direction: Input/Output                                            | Pins: 18, 23, 25                                                                                                               |

|             | •                                                                    | •                                                                  | RF_3V3 supply and the ground for DIG_GND externally to the Wi125.                                                              |

| RFV_OUT     | Type: Power                                                          | Direction: Output                                                  | Pin: 17                                                                                                                        |

|             | the power to the RF RF components but                                | subsystem of the Wi125 . This m                                    | y the RF_3V3 signal. This supplies hay also be used to power external noise onto this signal. No more than external circuitry. |

| _ANT_SUPPLY | Type: Power                                                          | Direction: Input                                                   | Pin: 26                                                                                                                        |

|             |                                                                      | enna. The maximum voltage sho                                      | upply power to the RF_IN signal, for ould not exceed ±15V and the current                                                      |

| DIG_3V3     | Type: Power                                                          | Direction: Input                                                   | Pin: 36                                                                                                                        |

|             | and the LDO regulate                                                 |                                                                    | olies the I/O ring of the BB25IC chip<br>125 . It is important that this supply is<br>sise with respect to DIG_GND.            |

| DIG_1V8     | Type: Power                                                          | Direction: Input                                                   | Pin: 34                                                                                                                        |

|             | to the +1V8_OUT sig                                                  |                                                                    | nis is normally connected directly V ± 5% is available, a lower overall ng an external supply.                                 |

| +1V8_OUT    | Type: Power                                                          | Direction: Output                                                  | Pin: 33                                                                                                                        |

|             | The 1.8V output from this is connected to the but care must be taken | n the LDO regulator that is powe<br>he DIG_1V8 signal. This may al | ered by the DIG_3V3 signal. Normally, so be used to power external logic ignal. No more than an additional                     |

| DIG_GND     | Type: Power                                                          | Direction: Input/Output                                            | Pin: 35                                                                                                                        |

|             | · ·                                                                  | •                                                                  | 3V3 supply and the ground reference RF_GND externally to the Wi125.                                                            |

# 4.1 Power Signals cont'd

| VBATT            | Type: Power                                                                              | Direction: Input/Output                                                                                                         | Pin: 27                                                                                                                                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | powered from the V<br>DIG_3V3) should b<br>The input has a blo<br>ing circuit. Typically | BATT signal. A supply of typic e applied to this signal. This si cking diode and so rechargeal, a 1K resister in series with th | n board Real Time Clock (RTC). This is ally 3v (greater than 2.5V and less than gnal can be left floating if not required. ble batteries will need an external chargis signal and the external battery will consumption from VBATT during test. |

| 4.2 RF Signals   |                                                                                          |                                                                                                                                 |                                                                                                                                                                                                                                                 |

| RF_IN            | Type: RF                                                                                 | Direction: Input                                                                                                                | Pin: 24                                                                                                                                                                                                                                         |

|                  | be used when track<br>ANT_SUPPLY sign<br>Wi125 . Only one a                              | king to this signal. This signal h<br>al. This is the same signal pres<br>ntenna connection should be r                         | tenna. Standard RF design rules must has an RF blocked connection to the sented on the RF connector on the made. If the RF connector is to be used, connected pad, to this castellation.                                                        |

| TRIM             | Type: RF                                                                                 | Direction: Input                                                                                                                | Pin: 12                                                                                                                                                                                                                                         |

|                  | When floating, this jected into this sign                                                | signal is biased to the control                                                                                                 | CXO. This signal is normally left open. voltage of the VCTCXO. Any noise inee performance of the Wi125. This signal pplication notes.                                                                                                           |

| EXT_CLK          | Type: RF                                                                                 | Direction: Input                                                                                                                | Pin: 7                                                                                                                                                                                                                                          |

|                  | the Wi125 that are the VCTCXO, do no                                                     | not fitted with an internal VCT0<br>ot connect this input. The exter<br>or an amplitude between 1V and                          | s to be used only in special builds of CXO. For the normal build, containing rnal clock is a 9 MHz to 26 MHz clipped d 3V peak to peak. The return path for                                                                                     |

| 4.3 Emulation/Te | est Signals                                                                              |                                                                                                                                 |                                                                                                                                                                                                                                                 |

| TDI              | Type: Test                                                                               | Direction: Input                                                                                                                | Pin: 14                                                                                                                                                                                                                                         |

|                  | The Test Data In Si<br>is DIG_GND.                                                       | gnal. This is the standard JTAC                                                                                                 | G test data input. The signal return path                                                                                                                                                                                                       |

| TDO              | Type: Test                                                                               | Direction: Output                                                                                                               | Pin: 13                                                                                                                                                                                                                                         |

|                  | The Test Data Out spath is DIG_GND.                                                      | Signal. This is the standard JT/                                                                                                | AG test data output. The signal return                                                                                                                                                                                                          |

| TCK              | Type: Test                                                                               | Direction: Input                                                                                                                | Pin: 20                                                                                                                                                                                                                                         |

|                  |                                                                                          |                                                                                                                                 | test clock input. The signal return path is                                                                                                                                                                                                     |

# 4.3 Power Signals cont'd

| TMS              | Type: Test                                                                                                                                                                                                                                             | Direction: Input                                                                                                                                                                                                                                            | Pin: 22                                                                                                                                                                                                                                                                                                                                                   |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | The Test Mode Sepath is DIG_GND.                                                                                                                                                                                                                       | lect Signal. This is the standard                                                                                                                                                                                                                           | JTAG test mode input. The signal return                                                                                                                                                                                                                                                                                                                   |

| JTAGSEL/RTCK     | Type: Test                                                                                                                                                                                                                                             | Direction: Input/Output                                                                                                                                                                                                                                     | Pin: 21                                                                                                                                                                                                                                                                                                                                                   |

|                  | an input and select<br>the embedded AR<br>mode is selected.<br>When NPOR is de<br>signal provides the<br>a single clock dom<br>cause a variable le<br>nized version of the                                                                             | ets the function of the JTAG interests the function of the JTAG interests. When the value on this signal is latched asserted (high) and the JTAG of the return clock to the ARM Multiplain, the TCK has to be internally ength delay in the validity of the | ignal is asserted (low), this signal is rface. When high, JTAG emulation into how, the BB25IC chip boundary scan ed when NPOR de-asserts (goes high). emulation mode has been latched, this ICE. Because the ARM9 functions off y synchronized in the ARM9. This can TDO signal. The RTCK is a synchroses the RTCK output signal to indicate the blg_GND. |

| NTRST            | Type: Test                                                                                                                                                                                                                                             | Direction: Input                                                                                                                                                                                                                                            | Pin: 15                                                                                                                                                                                                                                                                                                                                                   |

| 4.4 Control Sigi | is DIG_GND.                                                                                                                                                                                                                                            | gnal. This is the active low JTAG                                                                                                                                                                                                                           | test reset signal. The signal return path                                                                                                                                                                                                                                                                                                                 |

| NPOR             | Type: Control                                                                                                                                                                                                                                          | Direction: Input/Output                                                                                                                                                                                                                                     | Pin: 16                                                                                                                                                                                                                                                                                                                                                   |

| THI OIT          | The Power On Re<br>the Wi125 . The W<br>used to reset exte                                                                                                                                                                                             | set Signal. This active low, open<br>/i125 can be held in reset by ass                                                                                                                                                                                      | collector signal is the master reset for serting this signal. The signal can be aken to ensure no DC current is drawn                                                                                                                                                                                                                                     |

| NRESET           | Type: Control                                                                                                                                                                                                                                          | Direction: Input/Output                                                                                                                                                                                                                                     | Pin: 10                                                                                                                                                                                                                                                                                                                                                   |

|                  | The System Reset Signal. This active low, open collector signal is generated by the BB25IC chip in response to the assertion of the NPOR. It may also be driven to reset the ARM9 processor in the BB25IC without completely re-initializing the chip. |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                           |

| BOOTSEL          | Type: Control                                                                                                                                                                                                                                          | Direction: Input                                                                                                                                                                                                                                            | Pin: 11                                                                                                                                                                                                                                                                                                                                                   |

|                  | by the Wi125 . Thi<br>signal is high or le                                                                                                                                                                                                             | s signal is sampled when the NI                                                                                                                                                                                                                             | t up modes, but only two are supported POR is de-asserted. If the BOOTSEL from its on-chip FLASH memory. If the om its on-chip ROM.                                                                                                                                                                                                                       |

# 4.5 I/O Signals

| TX[0]         | Type: I/O                                                                                                                                                                                                                                                                                                                                     | Direction: Output                   | Pin: 1                                |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------|

|               | The Transmit Signate path is DIG_GND.                                                                                                                                                                                                                                                                                                         | al for UART 0. This is a standard   | UART output signal. The signal return |

| TX[1]         | Type: I/O                                                                                                                                                                                                                                                                                                                                     | Direction: Output                   | Pin: 5                                |

|               | The Transmit Signate path is DIG_GND.                                                                                                                                                                                                                                                                                                         | al for UART 1. This is a standard   | UART output signal. The signal return |

| TX[2]         | Type: I/O                                                                                                                                                                                                                                                                                                                                     | Direction: Output                   | Pin: 3                                |

|               | The Transmit Signal for UART 2. This is a standard UART output signal. The signal return path is DIG_GND.                                                                                                                                                                                                                                     |                                     |                                       |

| RX[0]         | Type: I/O                                                                                                                                                                                                                                                                                                                                     | Direction: Input                    | Pin: 2                                |

|               | The Receive Signal for UART 0. This is a standard UART input signal. The signal return path is DIG_GND.                                                                                                                                                                                                                                       |                                     |                                       |

| RX[1]         | Type: I/O                                                                                                                                                                                                                                                                                                                                     | Direction: Input                    | Pin: 6                                |

|               | The Receive Signate path is DIG_GND.                                                                                                                                                                                                                                                                                                          | al for UART 1. This is a standard l | JART input signal. The signal return  |

| _RX[2]/EV2_IN | Type: I/O                                                                                                                                                                                                                                                                                                                                     | Direction: Input                    | Pin: 4                                |

|               | This is a Dual Mode Signal. Normally, this is the receive signal for UART 2, a standard UART receive signal. Under software control, it can also be used as general purpose I/O or to detect events. It can be used to detect the timing of the leading edge of the start bit of the incoming data stream. The signal return path is DIG_GND. |                                     |                                       |

| FREQ_OUT      | Type: I/O                                                                                                                                                                                                                                                                                                                                     | Direction: Input/Output             | Pin: 32                               |

|               | Optional Frequency Output Signal. This is NOT the same signal as pin 39. This signal is turned off by default. This is a complex signal which under software can provide any of either an NCO generated output frequency, a PWM signal, a GPS aligned EPOCH pulse or general purpose I/O signal. The signal return path is DIG_GND.           |                                     |                                       |

| 1PPS          | Type: I/O                                                                                                                                                                                                                                                                                                                                     | Direction: Input/Output             | Pin: 38                               |

|               | The 1 Pulse Per Second Signal. This is normally a 1 pulse aligned with GPS time, bu under software control also provide general purpose I/O or an additional event input. pulse width of the 1PPS is software selectable with a default of 100µs. The signal retroated path is DIG_GND.                                                       |                                     |                                       |

| EVENT_IN      | Type: I/O                                                                                                                                                                                                                                                                                                                                     | Direction: Input/Output             | Pin: 37                               |

|               | The Event Input Signal with internal connection to Pin 39 (GPIO[1] / Time Sync) allows phase measurement of the Frequency Output. The signal return path is DIG_GND.                                                                                                                                                                          |                                     |                                       |

# 4.5 I/O Signals cont'd

| N2WCK                   | Type: I/O                                                                                                                                                                                                                                                               | Direction: Input/Output                                              | Pin: 28                                  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------|

|                         | •                                                                                                                                                                                                                                                                       |                                                                      | collector I2C compatible Clock Signal    |

|                         | for the 2 wire serial interface. The signal return path is DIG_GND.                                                                                                                                                                                                     |                                                                      |                                          |

| N2WDA                   | Type: I/O                                                                                                                                                                                                                                                               | Direction: Input/Output                                              | Pin: 29                                  |

|                         | The NavSync 2 Wire Data Signal. This is the open collector I2C compatible Data Signal                                                                                                                                                                                   |                                                                      |                                          |

|                         | for the 2 wire serial interface. The signal return path is DIG_GND.                                                                                                                                                                                                     |                                                                      |                                          |

| USBP <sup>4</sup>       | Type: I/O                                                                                                                                                                                                                                                               | Direction: Input/Output                                              | Pin: 30                                  |

|                         | The positive USB Signal. The signal return path is DIG_GND.                                                                                                                                                                                                             |                                                                      |                                          |

|                         |                                                                                                                                                                                                                                                                         |                                                                      |                                          |

| USBN <sup>4</sup>       | Type: I/O                                                                                                                                                                                                                                                               | Direction: Input/Output                                              | Pin: 31                                  |

|                         | The negative US                                                                                                                                                                                                                                                         | B Signal. The signal return path is E                                | DIG_GND.                                 |

| LED_RED                 | Type: I/O                                                                                                                                                                                                                                                               | Direction: Output                                                    | Pin: 8                                   |

|                         | This is a Dual Fu                                                                                                                                                                                                                                                       | nction Signal. Normally this signal is                               | s used to drive a red LED. Standard      |

|                         |                                                                                                                                                                                                                                                                         | _                                                                    | s. In special software builds, this sig- |

|                         |                                                                                                                                                                                                                                                                         | _                                                                    | MOS drive. A series limiting resistor is |

|                         | required to limit d                                                                                                                                                                                                                                                     | output current to ±5mA. The signal r                                 | eturi patri is Did_GND.                  |

| LED_GRN                 | Type: I/O                                                                                                                                                                                                                                                               | Direction: Output                                                    | Pin: 9                                   |

|                         |                                                                                                                                                                                                                                                                         | nction Signal. Normally this signal is                               | _                                        |

|                         | dard software builds use this signal to indicate GPS status. In special software builds, this signal can be used as GPIO. This signal has a 3.3V CMOS drive. A series limiting resistor is required to limit output current to ±5mA. The signal return path is DIG_GND. |                                                                      |                                          |

|                         |                                                                                                                                                                                                                                                                         |                                                                      |                                          |

|                         |                                                                                                                                                                                                                                                                         |                                                                      |                                          |

| GPIO[0]/PWM             | Type: I/O                                                                                                                                                                                                                                                               | Direction: Input/Output                                              | Pin: 39                                  |

|                         | •                                                                                                                                                                                                                                                                       |                                                                      | ency Output that defaults to 10 MHz,     |

|                         |                                                                                                                                                                                                                                                                         | •                                                                    | al. The output is enabled on power-up    |

|                         | -                                                                                                                                                                                                                                                                       | the GPS solution. Custom soπware<br>WM or EPOCH output. The signal r | e versions can also configure this pin   |

|                         | ior general i/o, i                                                                                                                                                                                                                                                      | vvivi or Er Gori Gatpat. The signar                                  | otam patino bia_anb.                     |

| GPIO[1]/TIME_SYNC       | Type: I/ODirection                                                                                                                                                                                                                                                      | n: Input/Output                                                      | Pin: 40                                  |

|                         | The GPIO[1]/TIME_SYNC pin provides a synchronization pulse generated by the on-                                                                                                                                                                                         |                                                                      |                                          |

|                         | board RTC. Custom software versions can also configure this pin for general purpose I/O, or an additional PPS output. The signal return path is DIG_GND.                                                                                                                |                                                                      |                                          |

| Note A HOD's set of the | or an additional F                                                                                                                                                                                                                                                      | רא סענput. דחפ signal return path is                                 | S DIG_GND.                               |

Note: 4. USB is not supported in the current software build.

## 4.5 I/O Signals cont'd

| GPIO[2]/NEXT_INT | Type: I/O                                                                                | Direction: Input/Output | Pin: 41                            |  |

|------------------|------------------------------------------------------------------------------------------|-------------------------|------------------------------------|--|

|                  |                                                                                          |                         | status indicator for the Frequency |  |

|                  | Output available on pin 39 (GPIO[0]/PWM). Custom software versions can also configure    |                         |                                    |  |

|                  | this pin for general purpose I/O. The signal return path is DIG_GND.                     |                         |                                    |  |

|                  |                                                                                          |                         |                                    |  |

| GPIO[3]/FREQ_IN  | Type: I/O                                                                                | Direction: Input/Output | Pin: 42                            |  |

|                  | The GPIO[3]/FREQ_IN output provides an active high status 3D fix indicator. This indi-   |                         |                                    |  |

|                  | cator can also be used to determine the validity of the pin 38 (1PPS) output. The signal |                         |                                    |  |

|                  | return path is DIG_GND.                                                                  |                         |                                    |  |

## **5 SPECIAL FEATURES**

While most of the features on the Wi125 are just a subset of the capabilities of the Wi125 and so are described in the Wi125 Data Sheet and the Wi125 User Manual, there are some additional features specific to the Wi125 that require explanation.

## 5.1 User Commands

The Wi125 can accept a number of specific user commands for setting receiver parameters such as UART baud rate and NMEA message subset, output frequency, etc. Many of these parameters are stored in Non-Volatile Memory (NVM) so that the settings are retained when the receiver loses power. The available commands are defined in detail in the Wi125 User Manual.

## 5.2 Self Survey

To optimize timing performance, the Wi125 performs a 10-minute survey each time the receiver is powered up and after obtaining a GPS fix. When the survey is complete, the receiver automatically enters fixed timing mode. For applications with specific timing performance requirements, it may be necessary to allow the survey to complete before using the 1PPS and frequency outputs. The status of the survey can be determined by querying the receiver dynamics setting as described in the Wi125 User Manual.

### 5.3 Wi125 Embedded Identification

The hardware version number is hard coded onto the Wi125; firmware also contains a version number allowing for easy identification of the hardware and software version in embedded applications.

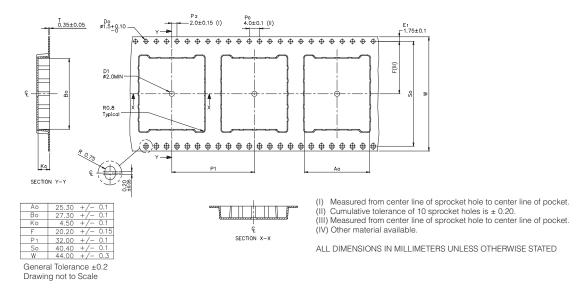

## **6 TAPE AND REEL SPECIFICATIONS**

Figure 5 Tape and Reel

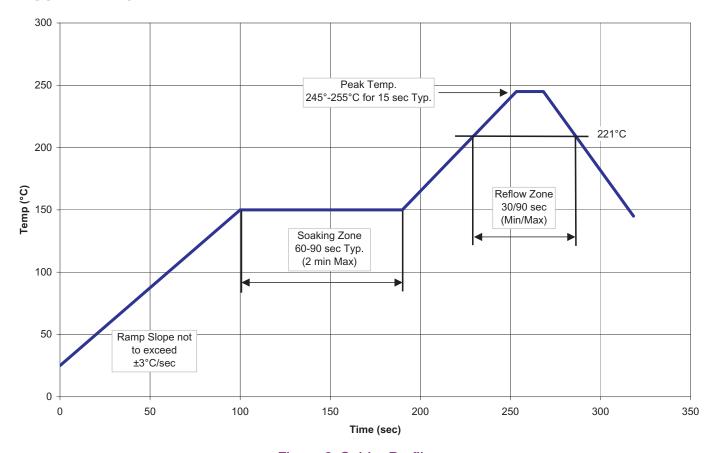

## 7 SOLDER PROFILE

Figure 6 Solder Profile

### **8 APPLICATION HINTS**

The following are a list of application hints that may help in implementing system based on the Wi125.

## 8.1 Power Supply

The power supply requirements of the Wi125 can all be provided from a single 3.3V supply. To simplify system integration on-board regulators provide the correct voltage levels for the RF and oscillator (2.9V or 3.0V) and low voltage digital core (1.8V). In power sensitive applications it is recommended that the DIG\_1V8 supply is provided from a high efficiency external 1.8V source e.g. switch mode power supply, rather than the on-board linear regulator.

If the source impedance of the power supply to the Wi125 is high due to long tracks, filtering or other causes, local decoupling of the supply signals may be necessary. Care should be taken to ensure that the maximum supply ripple at the pins of the Wi125 is 50mV peak to peak.

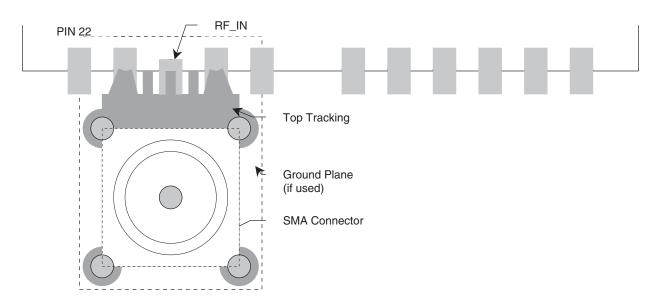

### 8.2 RF Connection

The RF connection to the Wi125 can be done in two ways. The preferred method is to use standard microstrip design techniques to track from the antenna element to the RF\_IN castellation. This also allows the systems integrator the option of designing in external connectors suitable for the application. The user can easily fit an externally mounted MCX, SMA or similar connector, provided it is placed adjacent to the RF\_IN castellation. If the tracking guidelines given below are followed, the impedance match will be acceptable. The diagram below shows how this could be achieved. In this diagram, the centre via of the RF connector is presumed to be plated through with a minimal pad top and bottom. The PCB material is assumed to be 1.6mm thick FR4 with a dielectric constant of 4.3. Two situations are considered; one with no ground plane and one with a ground plane on the bottom of the board, underneath the RF connector. In both cases there is no inner layer tracking under the RF connector.

Figure 7 RF Tracking Example

## 8 APPLICATION HINTS continued

The widths of the RF\_IN track and the associated gaps are given in the table below.

| Scenario             | Track Width (1/1000 Inch) | Gap Width (1/1000 Inch) |  |

|----------------------|---------------------------|-------------------------|--|

| Without ground plane | 37                        | 6                       |  |

|                      | 56                        | 8                       |  |

| With ground plane    | 32                        | 6                       |  |

|                      | 43                        | 8                       |  |

Table 7 RF Track & Gap Widths

Alternatively, the user can attach the antenna to the Hirose H.FL-R-SMT using a flying lead fitted with a suitable plug.

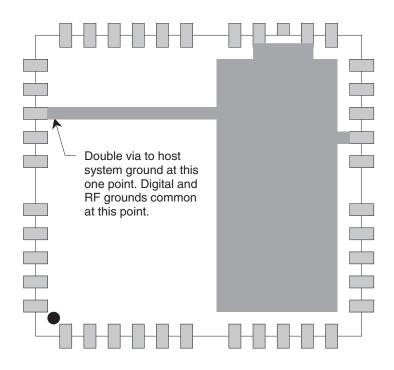

## 8.3 Grounding

In connecting the Wi125 into a host system, good grounding practices should be observed. Specifically, ground currents from the rest of the system hosting the Wi125 should not pass through the ground connections to the Wi125 . This is most easily ensured by using a single point attachment for the ground. There must also be a good connection between the RF\_GND and the DIG\_GND signals. While there is not a specific need to put a ground plane under the Wi125 , high energy signals should not be tracked under the Wi125 . It is however recommended that a ground plane be used under the Wi125 . In this case, the following would be an example of the pattern that may be used

Figure 8 Grounding the Wi125 with a Ground Plane

## 8 APPLICATION HINTS continued

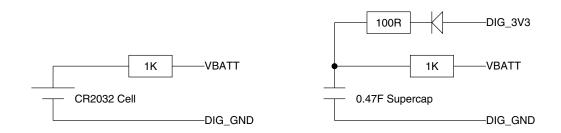

## 8.4 Battery Backup

The Wi125 has an on-board real time clock (RTC). This is used to store date and time information while the Wi125 is powered down. Having a valid date and time speeds the Time To First Fix (TTFF), allowing the Wi125 to meet its quoted TTFF specification. The Wi125 relies on an external power source to power the RTC (VBATT) when the DIG\_3V3 is not present. If the user application does not require the warm or hot fix performance, or the required information is provided by network assistance, there is no need to provide the VBATT signal. The VBATT signal must be greater than 2.6V and less than DIG\_3V3 + 0.6V. Typically, a 3V lithium primary cell or a high capacity "supercap" will be used. The Wi125 has an internal blocking diode, so if a "supercap" or rechargeable battery is used, an external charging circuit will be required.

Figure 7 Typical VBATT Supplies

# 125 Series Wi125 Series

2111 Comprehensive Drive

Aurora, Illinois 60505

Phone: 630-851-4722

Fax: 630-851-5040

www.conwin.com