# MMA955xL Intelligent, Motion-Sensing Platform Software Reference Manual

Devices Supported: MMA9550L MMA9551L MMA9553L

Document Number: MMA955XLSWRM

Rev. 0, 04/2012

#### How to Reach Us:

Home Page: www.freescale.com

Web Support:

http://www.freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: http://www.reg.net/v2/webservices/Freescale/Docs/TermsandConditions.htm.

Freescale, the Freescale logo, CodeWarrior, ColdFire, Energy Efficient Solutions logo, are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. ColdFire+ and Xtrinsic are trademarks of Freescale Semiconductor, Inc.

All other product or service names are the property of their respective owners.

© 2012 Freescale Semiconductor, Inc. All rights reserved.

### **Contents**

**Chapter 1 About This Document** 1.1 1.2 1.3 1.4 1.5 **Chapter 2 Introduction** 2.1 MMA955xL package: axis orientation ......16 2.2 2.3 2.4 2.5 2.6 **Chapter 3 Version Application** 3.1 Reading the version information ...... **Chapter 4 Scheduler Application** 4.1 4.2 4.3 4.4 4.4.2 Low-priority task becoming ready during high-priority task .......40 4.5 4.6 Scheduler configuration registers ......42 4.6.3 Interrupt assignment registers ......45 4.6.4 Scheduler parameters register ......50 4.7

| Sect | tion Nun | mber Title                                      | Page |

|------|----------|-------------------------------------------------|------|

|      |          | Chapter 5 Communication Interface               |      |

| 5.1  | Overvie  | iew of Communication Interface                  | 55   |

| 5.2  | Mailbox  | x interface                                     | 55   |

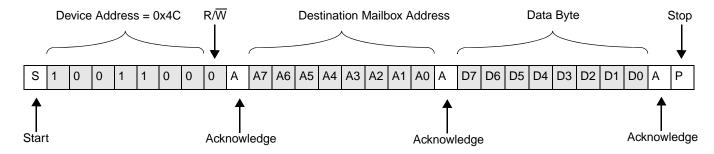

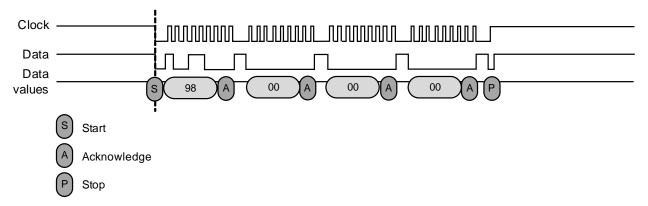

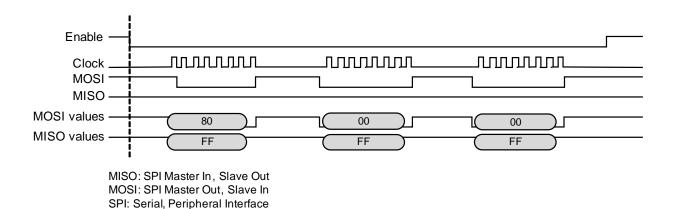

|      | 5.2.1    | Mailbox timing diagrams                         | 56   |

| 5.3  |          | ox usage                                        |      |

|      |          | Mailbox command format for a write              |      |

|      |          | Application IDs, names, and descriptions        |      |

|      | 5.3.3    | Mailbox command format for a read               | 60   |

|      |          | Chapter 6 GPIO Application                      |      |

| 6.1  |          | iew of GPIO application                         |      |

| 6.2  |          | configuration registers                         |      |

|      |          | GPIO register tables                            |      |

|      |          | GPIO polarity configuration                     |      |

|      | 6.2.3    | GPIO application bit descriptions               | 66   |

|      |          | Chapter 7 Mailbox Application                   |      |

| 7.1  |          | iew of Mailbox application                      |      |

| 7.2  |          | ox configuration registers                      |      |

|      |          | MBOX bit descriptions                           |      |

|      |          | Configuring XYZ data                            |      |

| 7.3  |          | ox status registers                             |      |

| 7.4  | Reading  | ng aggregated data (Legacy mode - Quick read)   | /4   |

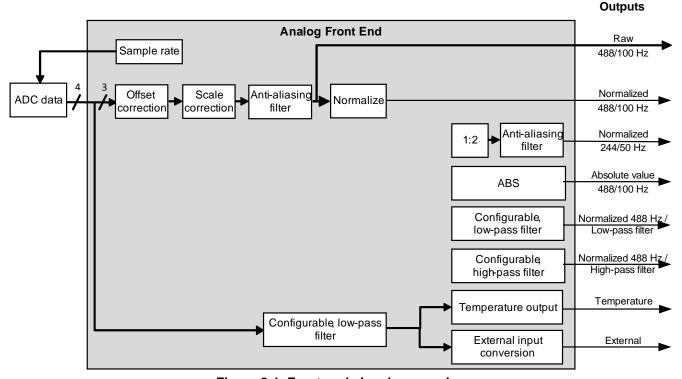

|      |          | Chapter 8 Analog Front End Application          |      |

| 8.1  |          | iew of Analog Front End application             |      |

|      |          | Sample rate                                     |      |

|      |          | Offset and scale correction                     |      |

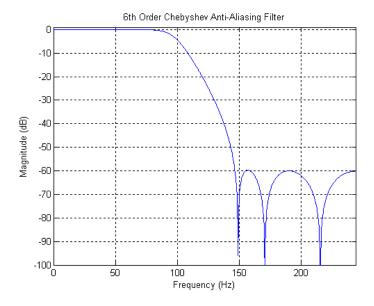

|      |          | Anti-aliasing filter                            |      |

|      |          | Raw data                                        |      |

|      | 8.1.5    |                                                 |      |

|      |          | Down-sampling and stage-1, anti-aliasing filter |      |

|      | 8.1.8    |                                                 |      |

| 8.2  |          | onfiguration registers                          |      |

| 0.2  | 8.2.1    |                                                 |      |

|      | 8.2.2    |                                                 |      |

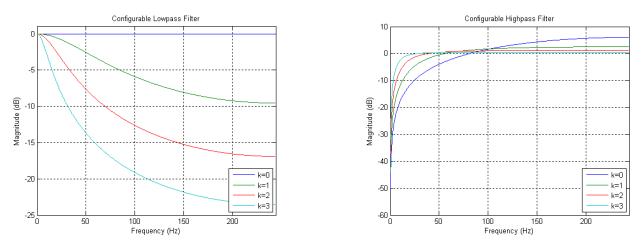

|      | _        | config_k                                        |      |

|      |          | sfd_rate                                        |      |

| 8.3  |          | tatus registers                                 |      |

|      | 8.3.1    | output[FRONTEND_Stage_0][XYZ]                   | 87   |

|      | 8.3.2    |                                                 |      |

|      |          | output[FRONTEND_Stage_0_ABS][XYZ]               |      |

|      | 8.3.4    | output[FRONTEND_Stage_0_GM][XYZ]                | 90   |

|      |          |                                                 |      |

| Sect | ion Nur | mper little                                                               | Page   |

|------|---------|---------------------------------------------------------------------------|--------|

|      | 8.3.5   | output[FRONTEND_Stage_0_LPF][XYZ]                                         | 91     |

|      | 8.3.6   |                                                                           |        |

|      | 8.3.7   |                                                                           |        |

|      | 8.3.8   | output_EIC                                                                |        |

|      | 8.3.9   | frame_counter                                                             | 94     |

|      |         | Chapter 9 Portrait/Landscape Application                                  |        |

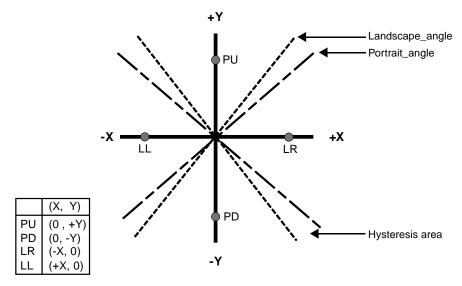

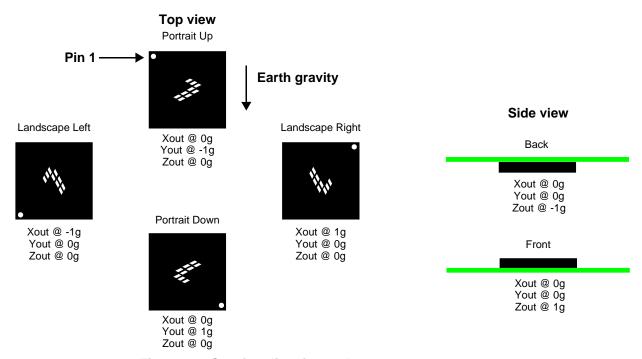

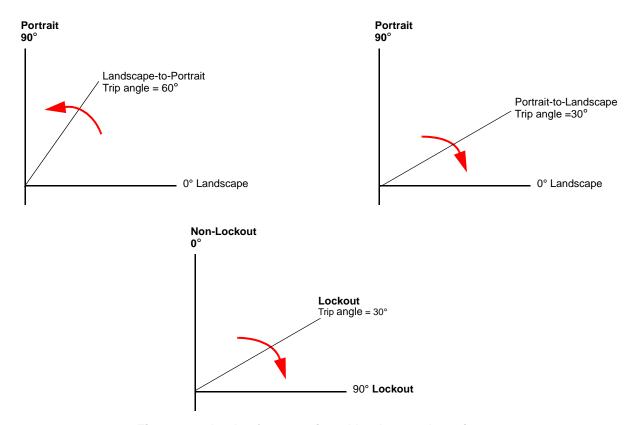

| 9.1  | Overvie | ew of Portrait/Landscape application                                      |        |

| 9.2  |         | t/Landscape configuration registers                                       |        |

|      | 9.2.1   | threshold_tilt                                                            |        |

|      | 9.2.2   |                                                                           |        |

|      | 9.2.3   |                                                                           |        |

|      | 9.2.4   |                                                                           |        |

|      | 9.2.5   | · · · · · · · · · · · · · · · · · · ·                                     |        |

|      | 9.2.6   | hysteresis_BAFRO                                                          |        |

| 0.0  | 9.2.7   | <b>5</b>                                                                  |        |

| 9.3  |         | t/Landscape status registers                                              |        |

|      |         | PL_Out                                                                    |        |

|      | 9.3.2   | Programming example                                                       | 103    |

|      |         | Chapter 10 High-g/Low-g Application                                       |        |

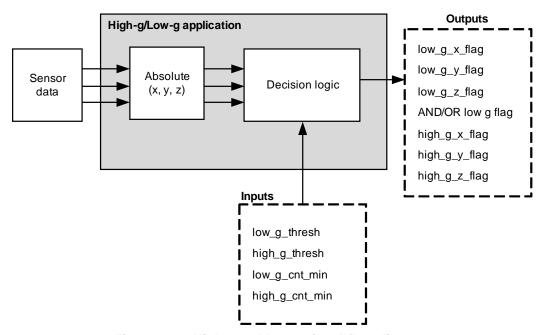

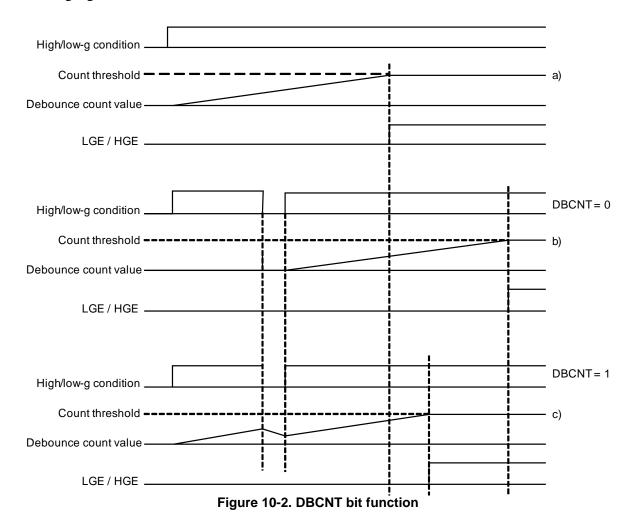

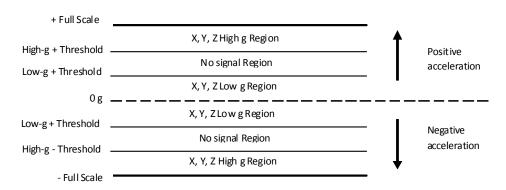

|      |         | ew of High-g/Low-g application                                            |        |

| 10.2 |         | /Low-g configuration registers                                            |        |

|      |         | 1 low_g_thresh                                                            |        |

|      |         | 2 low_g_cnt_min                                                           |        |

|      |         | 3 low_g_cfg                                                               |        |

|      |         | 4 high_g_thresh                                                           |        |

|      |         | 5 high_g_cnt_min                                                          |        |

|      |         | 7 lhg_event_mask                                                          |        |

| 10 3 |         | /Low-g status register                                                    |        |

| 10.0 |         | 1 lhg out                                                                 |        |

|      | 10.0.   | <u> </u>                                                                  |        |

|      |         | Chapter 11 Tap Detection Application                                      |        |

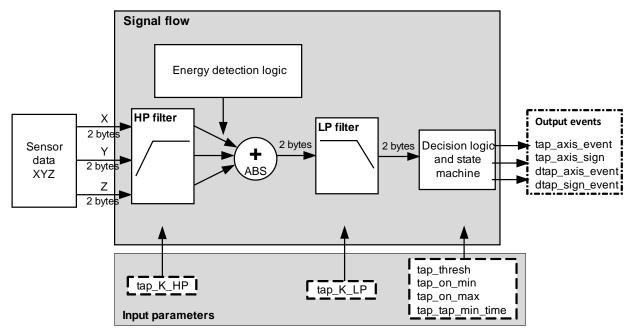

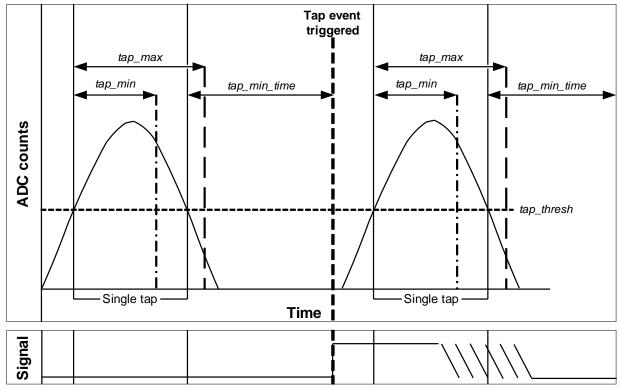

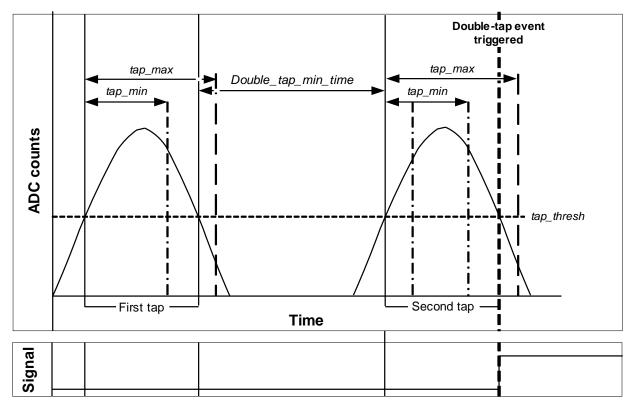

|      |         | ew of Tap Detection application                                           |        |

| 11.2 |         | etection configuration registers                                          |        |

|      |         | 1 tap_thresh                                                              |        |

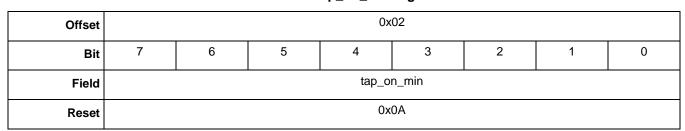

|      |         | 2 tap_on_min                                                              |        |

|      |         | 3 tap_on_max                                                              |        |

|      |         | 4 double_tap_min_time                                                     |        |

|      |         | 5 tap_K_HP                                                                |        |

|      |         | 6 tap_K_LP                                                                |        |

|      |         | 8 tap_events_mask                                                         |        |

|      | 11.4.0  | 0 tdp_010110_11100k                                                       |        |

|      |         | MMA955xL Intelligent Motion-Sensing Platform Software Reference Manual, R | lev. 0 |

| Sect | tion Number                       | Title                          | Page |

|------|-----------------------------------|--------------------------------|------|

| 11.3 | Tap-Detection status registers    |                                | 124  |

|      | 11.3.1 TAP_Out                    |                                |      |

|      | 11.3.2 DTAP_Out                   |                                |      |

|      | Chapt                             | er 12 Tilt Application         |      |

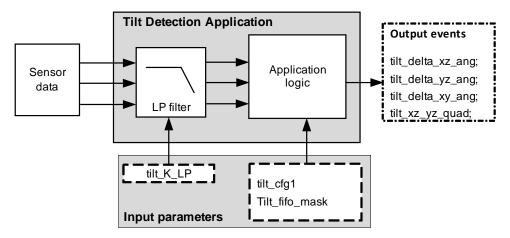

| 12.1 | Overview of Tilt application      |                                |      |

| 12.2 | Tilt configuration registers      |                                |      |

|      | 12.2.1 tilt_K_LP                  |                                |      |

|      | 12.2.2 tilt_cfg1                  |                                |      |

|      | 12.2.3 tilt_event_mask            |                                |      |

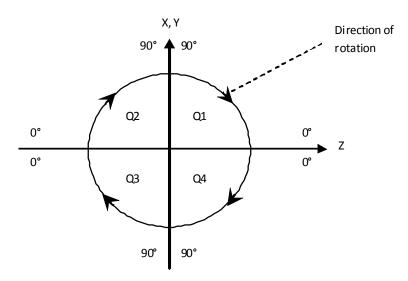

| 12.3 | Tilt status registers             |                                |      |

|      | 12.3.1 tilt_delta_xz_ang          |                                |      |

|      | 12.3.2 tilt_delta_yz_ang          |                                |      |

|      | 12.3.3 tilt_delta_xy_ang          |                                |      |

|      | 12.3.4 tilt_xz_yz_quad            |                                |      |

|      | Chapter 13 I                      | Frame Counter Application      | on   |

| 13.1 | Overview of Frame Counter appli   | cation                         |      |

|      | Frame-Counter configuration regi  |                                |      |

| 13.3 | Frame-Counter status register     |                                |      |

|      | 13.3.1 frame_cnt                  |                                |      |

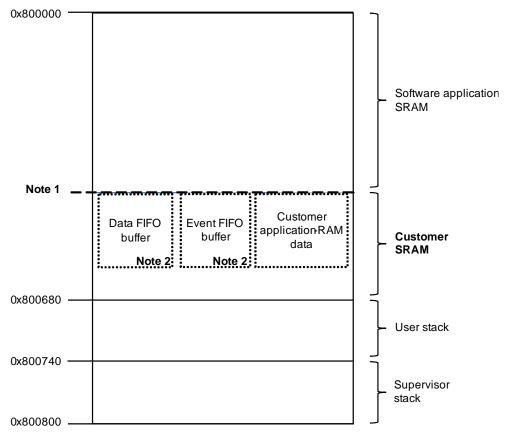

|      | Chapter 1                         | 4 Data FIFO Application        |      |

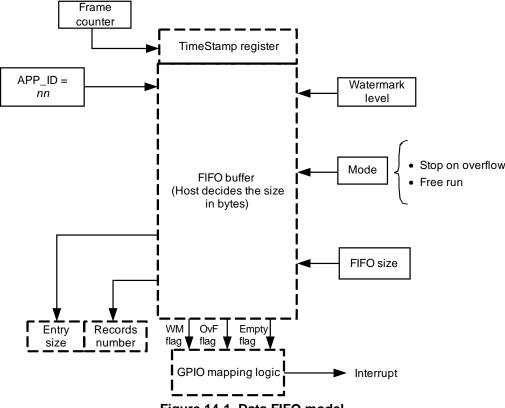

| 14.1 | Overview of Data FIFO application |                                |      |

|      | Modes of operation                |                                |      |

|      | 14.2.1 Stop-on-overflow           |                                |      |

|      | 14.2.2 Free-run                   |                                |      |

| 14.3 | Reading process                   |                                |      |

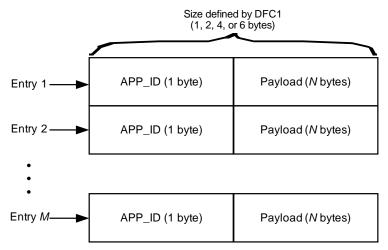

|      | Data FIFO block diagram           |                                |      |

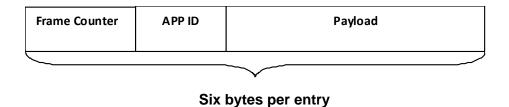

|      | 14.4.1 Entries format             |                                |      |

| 14.5 | Data FIFO configuration registers |                                |      |

|      | 14.5.1 FIFO configuration byte    |                                |      |

|      | 14.5.2 FIFO size word             |                                |      |

|      | 14.5.3 FIFO APP_ID                |                                |      |

|      | 14.5.4 Watermark                  |                                |      |

| 14.6 | Data FIFO status registers        |                                |      |

|      | 14.6.1 Records number             |                                |      |

|      | 14.6.2 Entry size                 |                                |      |

|      | 14.6.3 FIFO_Status                |                                |      |

|      | Chapter 15                        | <b>Event Queue Application</b> | 1    |

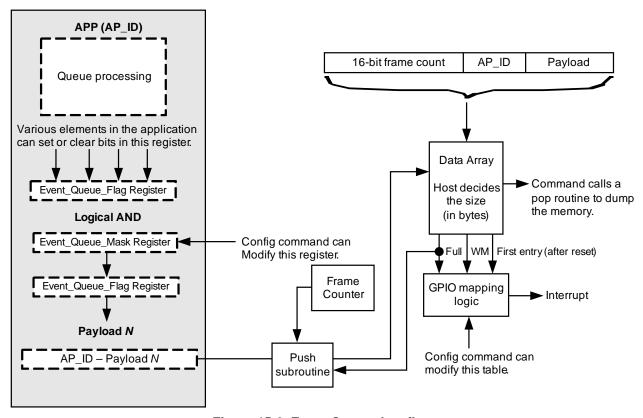

| 15.1 | Overview of Event Queue applica   |                                |      |

|      | 15.1.1 Modes of operation         |                                |      |

|      | 15.1.2 Reading process            |                                |      |

|      | 31                                |                                |      |

|       | n Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Title P              | age   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|

|       | 15.1.3 Event Queue block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      | . 155 |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       | 15.3.1 records_number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      | .158  |

|       | 15.3.2 entry_size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      | .158  |

|       | 15.3.3 queue_status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      | .159  |

|       | Chapter 16 Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Degister Application |       |

| 404.0 | <del>-</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Register Application | 404   |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

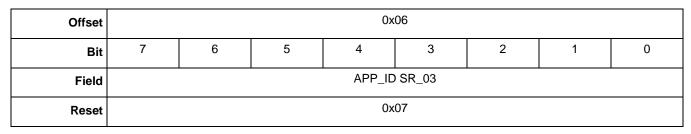

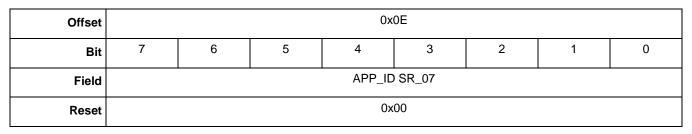

|       | 16.2.3 APP_ID 3R_U1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      | 162   |

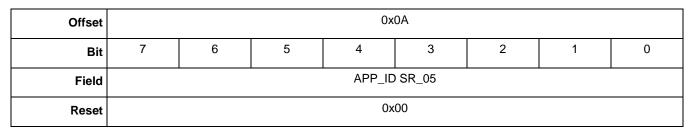

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       | 16.2.10Output Bit ID SR 04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | .164  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |