## **INSTALLATION GUIDE**

# 18-Slot NI PXIe-1075 Backplane

This guide describes installation requirements for the 18-slot NI PXIe-1075 backplane.

# **Contents**

| NI PXIe-1075 Backplane Overview                       | 2  |

|-------------------------------------------------------|----|

| Interoperability with CompactPCI                      | 3  |

| System Controller Slot                                |    |

| Hybrid Peripheral Slots                               |    |

| PXI Express Peripheral Slots                          | 4  |

| System Timing Slot                                    |    |

| PXI Local Bus                                         | 5  |

| PXI Trigger Bus                                       | 6  |

| System Reference Clock                                |    |

| PXIe_SYNC_CTRL                                        |    |

| Mechanical Requirements                               | 10 |

| Mounting                                              |    |

| Cooling                                               | 10 |

| Handling                                              | 10 |

| Dimensions                                            | 11 |

| Electrical Requirements                               | 12 |

| PXI Connectors                                        | 12 |

| Power                                                 | 13 |

| Connector J505                                        | 13 |

| Connector J506                                        | 15 |

| Connector J500                                        | 15 |

| Connectors J1, J2, J5, and J3                         | 16 |

| Backplane Specifications                              | 16 |

| System Synchronization Clock (PXI_CLK10, PXIe_CLK100, |    |

| PXIe_SYNC100) Specifications                          |    |

| 10 MHz System Reference Clock: PXI_CLK10              | 17 |

| 100 MHz System Reference Clock: PXIe_CLK100           |    |

| and PXIe_SYNC100                                      | 17 |

| External Clock Source                                 | 18 |

| PXIe_SYNC_CTRL                               | 18 |

|----------------------------------------------|----|

| PXI Differential Star Triggers (PXIe-DSTARA, |    |

| PXIe-DSTARB, PXIe-DSTARC)                    | 19 |

| Pinouts                                      | 19 |

| System Controller Slot Pinouts               | 20 |

| System Timing Slot Pinouts                   |    |

| Hybrid Slot Pinouts                          | 23 |

# NI PXIe-1075 Backplane Overview

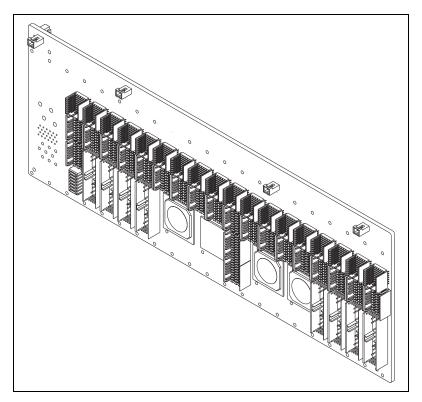

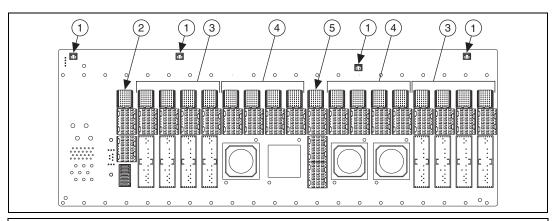

This section provides an overview of the backplane features for the NI PXIe-1075 chassis. Figure 1 shows the backplane.

Figure 1. 18-Slot NI PXIe-1075 Backplane

## Interoperability with CompactPCI

With the NI PXIe-1075, you can use the following devices in a single PXI Express system:

- PXI Express-compatible products

- CompactPCI Express-compatible 4-Link system controller products

- CompactPCI Express-compatible Type-2 peripheral products

- Hybrid-compatible PXI peripheral products

- Standard CompactPCI peripheral products

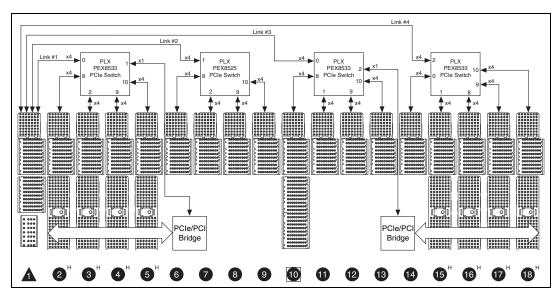

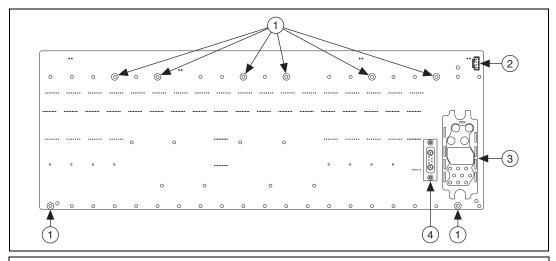

Figure 2. NI PXIe-1075 Backplane Architecture

### **System Controller Slot**

The system controller slot is Slot 1 of the chassis and is a 4-Link configuration system slot as defined by the CompactPCI Express and PXI Express specifications. It has three system controller expansion slots for system controller modules that are wider than one slot. These slots allow the system controller to expand to the left to prevent the system controller from using peripheral slots.

The backplane routes each of the system slots' x4 PCI Express (PCIe) links to a PCIe switch. The four PCIe switches have x4 PCIe links routed to each peripheral slot as well as x1 links to two (2) PCIe-to-PCI bridges providing 32-bit/33 MHz PCI busses to the hybrid slots. Refer to Figure 2 for the connectivity of PCIe and PCI.

By default, the system controller controls the power supply with the PS\_ON# signals. A logic low on this line turns on the power supply.

### **Hybrid Peripheral Slots**

The backplane includes eight hybrid peripheral slots as defined by the *PXI-5 PXI Express Hardware Specification*: slots 2–5 and 15–18. A hybrid peripheral slot can accept the following peripheral modules:

- A PXI Express peripheral with a x4 or x1 PCI Express link to the system slot or through a switch to the system slot.

- A CompactPCI Express Type-2 peripheral with a x4 or x1 PCI Express link to the system slot or through a switch to the system slot.

- A hybrid-compatible PXI peripheral module modified by replacing the J2 connector with an XJ4 connector installed in the upper eight rows of J2. Refer to the PXI Express Specification for details. The PXI peripheral communicates through the backplane 32-bit PCI bus.

- A CompactPCI 32-bit peripheral on the backplane 32-bit PCI bus.

The hybrid peripheral slots provide full PXI Express functionality and 32-bit PXI functionality except for PXI Local Bus. The hybrid peripheral slot connects only to PXI Local Bus 6 left and right.

## **PXI Express Peripheral Slots**

There are eight PXI Express peripheral slots: slots 6–9 and 11–14. Slots 6–9 are connected to the system slot link 2 through a PCI Express switch. Slots 11–13 are connected to the system slot link 3 through a PCI Express switch. Slot 14 is connected to the system slot link 4 through a PCI Express switch. PXI Express peripheral slots can accept the following modules:

- A PXI Express peripheral with a x4 or x1 PCI Express link to the system slot or through a switch to the system slot.

- A CompactPCI Express Type-2 peripheral with a x4 or x1 PCI Express link to the system slot or through a switch to the system slot.

## System Timing Slot

The system timing slot is slot 10. The system timing slot accepts the following peripheral modules:

- A PXI Express system timing module with a x4 or x1 PCI Express link to the system slot through a PCIe switch.

- A PXI Express peripheral with a x4 or x1 PCI Express link to the system slot through a PCIe switch.

- A CompactPCI Express Type-2 peripheral with a x4 or x1 PCI Express link to the system slot through a PCIe switch.

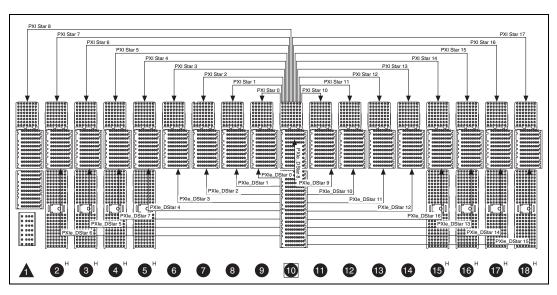

The system timing slot has three dedicated differential pairs (PXIe\_DSTAR) connected from the TP1 and TP2 connectors to the XP3 connector for each PXI Express peripheral or hybrid peripheral slot, as well as routed back to the XP3 connector of the system timing slot, as shown in Figure 3. You can use the PXIe\_DSTAR pairs for high-speed triggering, synchronization, and clocking. Refer to the *PXI Express Specification* for details.

The system timing slot also has a single-ended (PXI Star) trigger connected to every slot. Refer to Figure 3 for details.

The system timing slot has a pin (PXI\_CLK10\_IN) through which a system timing module can source a 10 MHz clock to which the backplane phase-locks. Refer to the *System Reference Clock* section for details.

The system timing slot has a pin (PXIe\_SYNC\_CTRL) through which a system timing module can control the PXIe\_SYNC100 timing. Refer to the PXI Express Specification and the PXIe\_SYNC\_CTRL section for details.

Figure 3. PXIe\_DSTAR and PXI Star Connectivity Diagram

## **PXI Local Bus**

The PXI backplane local bus is a daisy-chained bus that connects each peripheral slot with adjacent peripheral slots to the left and right.

The backplane routes PXI Local Bus 6 between adjacent PXI slots. The left local bus 6 from slot 1 is not routed anywhere, and the right local bus signal from slot 18 is not routed anywhere.

Local bus signals may range from high-speed TTL signals to analog signals as high as 42 V.

Initialization software uses the configuration information specific to each adjacent peripheral module to evaluate local bus compatibility.

## **PXI Trigger Bus**

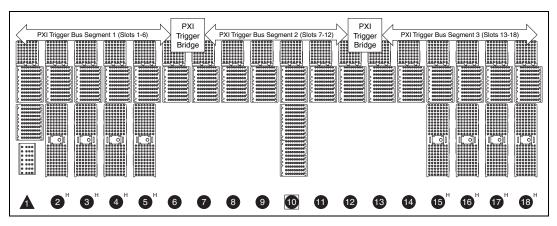

All slots on the same PXI bus segment share eight PXI trigger lines. You can use these trigger lines in a variety of ways. For example, you can use triggers to synchronize the operation of several different PXI peripheral modules. In other applications, one module in the system timing slot can control carefully timed sequences of operations performed on other modules in the system. Modules can pass triggers to one another, allowing precisely timed responses to asynchronous external events the system is monitoring or controlling. Figure 4 shows the PXI trigger bus connectivity.

The PXI trigger lines from adjacent PXI trigger bus segments can be routed in either direction across the PXI trigger bridges through buffers. This allows you to send trigger signals to, and receive trigger signals from, every slot in the chassis. You can configure static trigger routing (user-specified line and directional assignments) through Measurement & Automation Explorer (MAX). Dynamic routing of triggers (automatic line assignments) is supported through certain National Instruments drivers such as NI-DAQmx.

**Note** Although you can route any trigger line in either direction, you cannot route it in more than one direction at a time.

Figure 4. PXI Trigger Bus Connectivity Diagram

## **System Reference Clock**

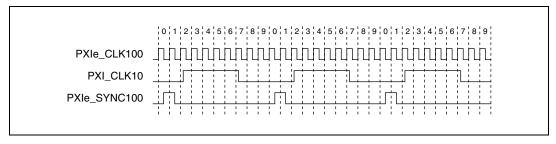

The NI PXIe-1075 chassis supplies PXI\_CLK10, PXIe\_CLK100, and PXIe\_SYNC100 to every peripheral slot with an independent driver for each signal.

An independent buffer (having a source impedance matched to the backplane and a skew of less than 1 ns between slots) drives PXI\_CLK10 to each peripheral slot. You can use this common reference clock signal to synchronize multiple modules in a measurement or control system.

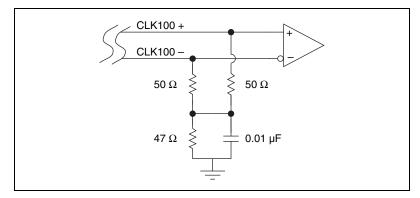

An independent buffer drives PXIe\_CLK100 to each peripheral slot. These clocks are matched in skew to less than 100 ps. The differential pair must be terminated on the peripheral with LVPECL termination for the buffer to drive PXIe\_CLK100 so that when there is no peripheral or a peripheral that does not connect to PXIe\_CLK100, no clock is being driven on the pair to that slot. Refer to Figure 5 for a termination example.

Figure 5. CLK100 Termination

An independent buffer drives PXIe\_SYNC100 to each peripheral slot. The differential pair must be terminated on the peripheral with LVPECL termination for the buffer to drive PXIe\_SYNC100 so that when there is no peripheral or a peripheral that does not connect to PXIe\_SYNC100, no SYNC100 signal is being driven on the pair to that slot. Refer to Figure 5 for a termination example.

In summary, PXI\_CLK10 is driven to every slot. PXIE\_CLK100 and PXIE\_SYNC100 are driven to every peripheral slot.

PXI\_CLK10, PXIe\_CLK100, and PXIe\_SYNC100 have the default timing relationship described in Figure 6.

Figure 6. System Reference Clock Default Behavior

To synchronize the system to an external clock, you can drive PXI\_CLK10 from an external source through the PXI\_CLK10\_IN pin on the System Timing Slot. Refer to Table 11, *XP4 Connector Pinout for the System Timing Slot*, for the pinout. When a 10 MHz clock is detected on this pin, the backplane automatically phase-locks the PXI\_CLK10, PXIe\_CLK100, and PXIe\_SYNC100 signals to this external clock and distributes these signals to the slots. Refer to the *Backplane Specifications* section for the specification information for an external clock provided on the PXI\_CLK10\_IN pin of the system timing slot.

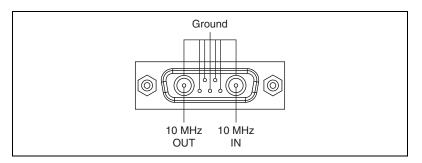

You also can drive a 10 MHz clock on connector J506. Refer to Figure 10 for the location of this connector. When a 10 MHz clock is detected on this connector, the backplane automatically phase-locks the PXI\_CLK10, PXIe\_CLK100, and PXIe\_SYNC100 signals to this external clock and distributes these signals to the slots. Refer to the *Backplane Specifications* section for the specification information for an external clock provided on the 10 MHz REF IN connector on the chassis rear panel.

If the 10 MHz clock is present on both the PXI\_CLK10\_IN pin of the System Timing Slot and connector J506, the signal on the System Timing Slot is selected. Refer to Table 1, which explains how the backplane selects the 10 MHz clocks.

System Timing Slot PXI\_CLK10\_IN

Rear Chassis Panel 10 MHz REF IN

Backplane PXI\_CLK10, PXIe\_CLK100 and PXIe\_SYNC100

No clock present

No clock present

Backplane generates its own clocks

No clock present

PXI\_CLK10, PXIe\_CLK100 and PXIe\_SYNC100 all phase-locked to Rear Chassis Panel—10 MHz REF IN

**Table 1.** Backplane External Clock Input Truth Table

**Table 1.** Backplane External Clock Input Truth Table (Continued)

| System Timing Slot<br>PXI_CLK10_IN | Rear Chassis Panel<br>10 MHz REF IN | Backplane PXI_CLK10, PXIe_CLK100 and PXIe_SYNC100                                           |

|------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------|

| 10 MHz clock present               | No clock present                    | PXI_CLK10, PXIe_CLK100 and PXIe_SYNC100 all phase-locked to System Timing Slot—PXI_CLK10_IN |

| 10 MHz clock present               | 10 MHz clock present                | PXI_CLK10, PXIe_CLK100 and PXIe_SYNC100 all phase-locked to System Timing Slot—PXI_CLK10_IN |

A copy of the backplane's PXI\_CLK10 is exported to connector J506. Refer to Figure 10 for the location of this connector. An independent buffer drives this clock. Refer to the *Backplane Specifications* section for the specification information for the 10 MHz REF OUT signal on the chassis rear panel.

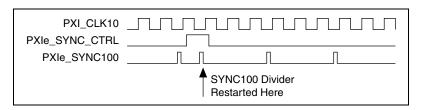

### PXIe\_SYNC\_CTRL

PXIe\_SYNC100 is by default a 10 ns pulse synchronous to PXI\_CLK10. The frequency of PXIe\_SYNC100 is 10/n MHz, where n is a positive integer. The default for n is 1, giving PXIe\_SYNC100 a 100 ns period. However, the backplane allows n to be programmed to other integers. For example, setting n = 3 creates a PXIe\_SYNC100 with a 300 ns period while still maintaining its phase relationship to PXI\_CLK10. The n value can be any positive integer from 1 to 255.

The system timing slot has a control pin for PXIe\_SYNC100 called PXIe\_SYNC\_CTRL, for use when n > 1. Refer to Table 10, XP3 Connector Pinout for the System Timing Slot, for the system timing slot pinout. Refer to the Backplane Specifications section for the PXIe\_SYNC\_CTRL input specifications.

By default, a high level detected by the backplane on the PXIe\_SYNC\_CTRL pin causes a synchronous restart for the PXIe\_SYNC100 signal. On the next PXI\_CLK10 edge, the PXIe\_SYNC100 signal restarts. This allows several chassis to have their PXIe\_SYNC100 in phase with each other. Refer to Figure 7 for timing details with this method.

Figure 7. PXIe\_SYNC100 at 3.33 MHz Using PXIe\_SYNC\_CTRL as Restart

## **Mechanical Requirements**

## Mounting

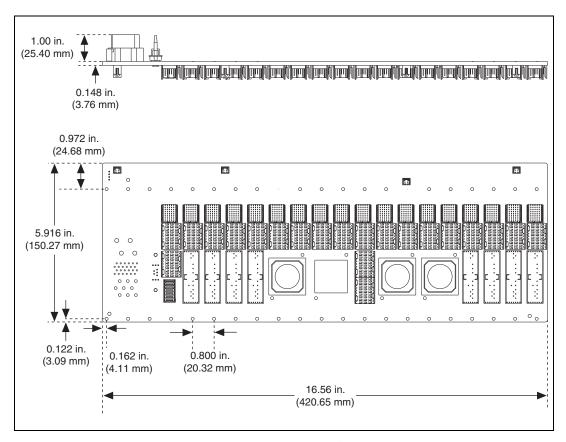

Figure 8 shows the backplane dimensions. There are 40 holes available for mounting with M2.5 hardware.

Use all mounting holes for proper backplane support.

Six mounting holes on top of the backplane have plated annular pads on the back of the backplane. Use these mounting holes to connect the backplane ground to the chassis in which the backplane is mounted. If you do not want to connect the backplane ground to the chassis, use insulated washers at these mounting holes. Refer to Figure 10 for the mounting hole positions.

For full backplane mounting and card cage dimensions, refer to the *CompactPCI Express PICMG EXP.0 R1.0 Specification*.

## Cooling

**Note** National Instruments is not responsible for damage to the backplane if inadequate cooling is used.

You should mount a fan below the backplane. Airflow should be from the bottom to the top of the PXI modules. You must determine the airflow requirements for your system based on the *PXI Hardware Specification*.

## **Handling**

**Caution** Be careful to avoid bending or otherwise damaging the pins on the backplane connectors. Bent pins may cause functional failures or damage when the backplane is powered.

**Caution** To protect both yourself and the backplane from electrical hazards, leave the chassis powered off until you finish installing the PXI controller and modules.

**Caution** Electrostatic discharge can damage your equipment. To avoid such damage, discharge the static built up on your body by touching a grounded metal object before handling the PXI equipment. Then touch the antistatic plastic package containing the backplane to a metal part of your PXI chassis before removing the backplane from the packaging.

## **Dimensions**

Figure 8. Dimensions

# **Electrical Requirements**

#### **PXI Connectors**

The PXI and PXI Express connectors have pin descriptions defined in the *PXI Hardware Specification* and *PXI Express Hardware Specification*. Figure 9 shows the connectors.

- 1 Card-Cage Thermistor Connectors (x4)

- 2 Slot 1 (Controller Slot)

- 3 Hybrid Peripheral Slots (2-5, 15-18)

- 4 PXI Express Peripheral Slots (6-9, 11-14)

- 5 System Timing Slot (10)

Figure 9. PXI Connectors

- 1 Plated Mounting Holes (8x)

- 2 Connector J500

- 3 Connector J505

- 4 Connector J506

Figure 10. Backplane Power, J500, and CLK10 Connectors

#### Power

Refer to the *PXI Express Hardware Specification* for power requirements and to the specifications of the chosen power supply to determine the minimum load required.

#### **Connector J505**

Connector J505 is the NI PXIe-1075 backplane power supply connector. Figure 10 shows the J505 location. Refer to Table 2 for the pin descriptions. Connector J505 consists of four large #8 pins (34–37) and nine #12 pins (1–9) for power. There are also 24 #20 pins (10–33) for mixed power and signaling. Table 2 also indicates which pins must be connected for basic backplane operation.

Refer to the CompactPCI Express specification for details regarding PS\_ON# and PS\_OK.

**Caution** Do not use the voltage sense pins (10, 18, and 25) to power the board. These pins are connected by thin trace to the backplane center and are for voltage sensing only. Providing current through these pins may damage the backplane. If your power supply has voltage sensing, use these pins; otherwise, leave them unconnected. Pins with "power plane" in the description are connected to the backplane's internal power planes and are suitable for carrying current.

**Note** Tyco Electronics manufactures the J505 mating connector, which you can order with part number 6648167–1.

**Note** The connector SMBus pins are connected to the backplane SMBus, which the CompactPCI Express specification defines. (The specification also defines uses and addressing.) Improper use of the SMBus could result in system controller malfunctions.

There are three SMBus slave devices on the NI PXIe-1075 backplane. The Backplane Descriptor EEPROM is at slave address  $A4_{\rm H}$  as defined by the CompactPCI Express specification, and the backplane clocking CPLD is at slave address  $5A_{\rm H}$ . There is a temperature monitoring device at slave address  $5C_{\rm H}$ . If you must connect an SMBus slave device to the J505 SMBus pins, use slave address  $58_{\rm H}$ .

Table 2. Connector J505 Pin Descriptions

| Connector                                | Pin | Signal      | Description                                      | Required<br>for Basic<br>Power Up |

|------------------------------------------|-----|-------------|--------------------------------------------------|-----------------------------------|

| Connector                                | 1   | +5V         | -                                                | Yes                               |

|                                          | 2   | GND         | +5 V power plane                                 |                                   |

|                                          |     |             | Ground plane                                     | Yes                               |

|                                          | 3   | GND         | Ground plane                                     | Yes                               |

|                                          | 4   | +3.3V       | +3.3 V power plane                               | Yes                               |

|                                          | 5   | +12V        | +12 V power plane                                | Yes                               |

|                                          | 6   | GND         | Ground plane                                     | Yes                               |

|                                          | 7   | GND         | Ground plane                                     | Yes                               |

|                                          | 8   | +12V        | +12 V power plane                                | Yes                               |

|                                          | 9   | GND         | Ground plane                                     | Yes                               |

|                                          | 10  | +12V_SENSE  | +12 V sense only, no power                       | No                                |

|                                          | 11  | GND         | Ground plane                                     | Yes                               |

| (34) (35)                                | 12  | -12V        | −12 V power plane                                | Yes                               |

|                                          | 13  | GND         | Ground plane                                     | No                                |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0  | 14  | OVERTEMP#   | Alert of over-temperature condition in card cage | No                                |

|                                          | 15  | GND         | Ground plane                                     | No                                |

| 16 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 16  | LED1        | J500—pin 3                                       | No                                |

|                                          | 17  | LED2        | J500—pin 4                                       | No                                |

|                                          | 18  | +5V_SENSE   | +5 V sense only, no power                        | No                                |

|                                          | 19  | GND         | Ground plane                                     | No                                |

|                                          | 20  | GND         | Ground plane                                     | No                                |

|                                          | 21  | GND         | Ground plane                                     | No                                |

|                                          | 22  | SMBCLK      | Backplane SMBus clock                            | No                                |

|                                          | 23  | SMBDAT      | Backplane SMBus data                             | No                                |

|                                          | 24  | SMBALERT#   | Backplane SMBus alert#                           | No                                |

|                                          | 25  | +3.3V_SENSE | +3.3 V sense only,<br>no power                   | No                                |

|                                          | 26  | GND         | Ground plane                                     | Yes                               |

|                                          | 27  | -12V        | −12 V power plane                                | Yes                               |

|                                          | 28  | 5VAUX       | 5VAUX power plane                                | Yes                               |

**Table 2.** Connector J505 Pin Descriptions (Continued)

| Connector | Pin | Signal  | Description                      | Required<br>for Basic<br>Power Up |

|-----------|-----|---------|----------------------------------|-----------------------------------|

|           | 29  | GND     | Ground plane                     | Yes                               |

|           | 30  | PS_ON#  | From system<br>slot J20—pin D2   | No                                |

|           | 31  | 12V_FAN | To test point E8                 | No                                |

|           | 32  | GND     | Ground plane                     | Yes                               |

|           | 33  | PS_OK   | To system slot from power supply | Yes                               |

|           | 34  | GND     | Ground plane                     | Yes                               |

|           | 35  | GND     | Ground plane                     | Yes                               |

|           | 36  | +3.3V   | +3.3 V power plane               | Yes                               |

|           | 37  | +5V     | +5 V power plane                 | Yes                               |

### **Connector J506**

Connector J506 is for interfacing with the backplane PXI\_CLK10 circuitry. Figure 11 shows the J506 connector location. Positronic manufactures the J506 mating connector, which you can order with part number CBD7W2M2000Z-759.1.

Figure 11. J506 Connector

#### **Connector J500**

Use connector J500 in conjunction with J505 for interfacing with an inhibit switch and LED. You do not need to connect anything to J500 for basic backplane power up. Refer to Table 3 for the pin descriptions. The power button (PWRBTN#) signal is a momentary pushbutton signal that tells the system controller to enable or inhibit the power supply. You can use signals LED1 and LED2 to drive a bicolor LED in the power switch, but you also can use these signals to carry another digital signal.

Table 3. Connector J500 Pin Descriptions

| Connector | Pin | Signal  | Description                     |

|-----------|-----|---------|---------------------------------|

| J500      | 1   | PWRBTN# | Input to system slot J20—pin F2 |

|           | 2   | GND     | Ground plane                    |

| 3         | 3   | LED1    | J505—pin 16                     |

|           | 4   | LED2    | J505—pin 17                     |

|           |     |         |                                 |

## Connectors J1, J2, J5, and J3

Use these connectors for four thermistors to monitor the card-cage temperature. You can use signal OVERTEMP# on J505 as an alarm indicating when the card-cage temperature exceeds 90  $^{\circ}$ C when used in conjunction with the four thermistors.

**Note** Use a Sensor Scientific KWM502C-6 or similar thermistor with these connectors.

**Note** The mating connector for J1, J2, J5, and J3 is Molex part number 50-57-9402.

## **Backplane Specifications**

| Size                          | 3U-sized; one system slot       |

|-------------------------------|---------------------------------|

|                               | (with three system expansion    |

|                               | slots) and 17 peripheral slots. |

|                               | Compliant with IEEE 1101.10     |

|                               | mechanical packaging.           |

|                               | PXI Express specification       |

|                               | compliant.                      |

|                               | Accepts both PXI Express and    |

|                               | CompactPCI (PICMG 2.0 R 3.0)    |

|                               | 3U modules.                     |

| Backplane bare-board material | UL 94 V-0 Recognized            |

| Backplane connectors          | Conforms to IEC 917 and         |

|                               | IEC 1076-4-101, and are         |

|                               | UL 94 V-0 rated                 |

# System Synchronization Clock (PXI\_CLK10, PXIe\_CLK100, PXIe\_SYNC100) Specifications

## 10 MHz System Reference Clock: PXI\_CLK10

**Note** For other specifications, refer to the *PXI-1 Hardware Specification*.

# 100 MHz System Reference Clock: PXIe\_CLK100 and PXIe SYNC100

**Note** For other specifications, refer to the *PXI-5 PXI Express Hardware Specification*.

## External 10 MHz Reference Out (on J506)

#### **External Clock Source**

## PXIe\_SYNC\_CTRL

## **PXI Star Trigger**

Maximum slot-to-slot skew ......250 ps

Backplane characteristic impedance......65  $\Omega \pm 10\%$

**Note** For PXI slot to PXI Star mapping, refer to the *System Timing Slot* section of Chapter 1, *Getting Started*, in the *NI PXIe-1075 User Manual*.

**Note** For other specifications, refer to the *PXI-1 Hardware Specification*.

# PXI Differential Star Triggers (PXIe-DSTARA, PXIe-DSTARB, PXIe-DSTARC)

**Note** For PXIe slot to PXI\_DSTAR mapping, refer to the *System Timing Slot* section of Chapter 1, *Getting Started*, in the *NI PXIe-1075 User Manual*.

**Note** For other specifications, the NI PXIe-1075 complies with the *PXI-5 PXI Express Hardware Specification*.

## **Pinouts**

This section describes the connector pinouts for the NI PXIe-1075 chassis backplane.

Table 4 shows the XP1 connector pinout for the System Controller slot.

Table 5 shows the XP2 Connector Pinout for the System Controller slot.

Table 6 shows the XP3 Connector Pinout for the System Controller slot.

Table 7 shows the XP4 Connector Pinout for the System Controller slot.

Table 8 shows the TP1 Connector Pinout for the System Controller slot.

Table 9 shows the TP2 Connector Pinout for the System Timing slot.

Table 10 shows the XP3 Connector Pinout for the System Timing slot.

Table 11 shows the XP4 Connector Pinout for the System Timing slot.

Table 12 shows the P1 connector pinout for the Hybrid peripheral slots.

Table 13 shows the XP3 Connector Pinout for the Hybrid peripheral slots.

Table 14 shows the XP4 Connector Pinout for the Hybrid peripheral slots.

For more detailed information, refer to the *PXI-5 PXI Express Hardware Specification*, Revision 2.0. Contact the PXI Systems Alliance for a copy of the specification.

# **System Controller Slot Pinouts**

Table 4. XP1 Connector Pinout for the System Controller Slot

| Pins | Signals |

|------|---------|

| A    | GND     |

| В    | 12V     |

| С    | 12V     |

| D    | GND     |

| Е    | 5V      |

| F    | 3.3V    |

| G    | GND     |

Table 5. XP2 Connector Pinout for the System Controller Slot

| Pin | A      | В      | ab  | C      | D      | cd  | E      | F      | ef  |

|-----|--------|--------|-----|--------|--------|-----|--------|--------|-----|

| 1   | 3PETp1 | 3PETn1 | GND | 3PERp1 | 3PERn1 | GND | 3РЕТр2 | 3PETn2 | GND |

| 2   | 3РЕТр3 | 3PETn3 | GND | 3PERp3 | 3PERn3 | GND | 3PERp2 | 3PERn2 | GND |

| 3   | 4PETp0 | 4PETn0 | GND | 4PERp0 | 4PERn0 | GND | 4PETp1 | 4PETn1 | GND |

| 4   | 4PETp2 | 4PETn2 | GND | 4PERp2 | 4PERn2 | GND | 4PERp1 | 4PERn1 | GND |

| 5   | 4РЕТр3 | 4PETn3 | GND | 4PERp3 | 4PERn3 | GND | RSV    | RSV    | GND |

| 6   | RSV    | RSV    | GND | RSV    | RSV    | GND | RSV    | RSV    | GND |

| 7   | RSV    | RSV    | GND | RSV    | RSV    | GND | RSV    | RSV    | GND |

| 8   | RSV    | RSV    | GND | RSV    | RSV    | GND | RSV    | RSV    | GND |

| 9   | RSV    | RSV    | GND | RSV    | RSV    | GND | RSV    | RSV    | GND |

| 10  | RSV    | RSV    | GND | RSV    | RSV    | GND | RSV    | RSV    | GND |

Table 6. XP3 Connector Pinout for the System Controller Slot

| Pin | A      | В      | ab  | С        | D        | cd  | E        | F        | ef  |

|-----|--------|--------|-----|----------|----------|-----|----------|----------|-----|

| 1   | RSV    | RSV    | GND | RSV      | RSV      | GND | RSV      | RSV      | GND |

| 2   | RSV    | RSV    | GND | PWR_OK   | PS_ON#   | GND | LINKCAP  | PWRBTN#  | GND |

| 3   | SMBDAT | SMBCLK | GND | 4RefClk+ | 4RefClk- | GND | 2RefClk+ | 2RefClk- | GND |

| 4   | RSV    | PERST# | GND | 3RefClk+ | 3RefClk- | GND | 1RefClk+ | 1RefClk- | GND |

Table 6. XP3 Connector Pinout for the System Controller Slot (Continued)

| Pin | A      | В      | ab  | C      | D      | cd  | E      | F      | ef  |

|-----|--------|--------|-----|--------|--------|-----|--------|--------|-----|

| 5   | 1PETp0 | 1PETn0 | GND | 1PERp0 | 1PERn0 | GND | 1PETp1 | 1PETn1 | GND |

| 6   | 1PETp2 | 1PETn2 | GND | 1PERp2 | 1PERn2 | GND | 1PERp1 | 1PERn1 | GND |

| 7   | 1PETp3 | 1PETn3 | GND | 1PERp3 | 1PERn3 | GND | 2PETp0 | 2PETn0 | GND |

| 8   | 2PETp1 | 2PETn1 | GND | 2PERp1 | 2PERn1 | GND | 2PERp0 | 2PERn0 | GND |

| 9   | 2PETp2 | 2PETn2 | GND | 2PERp2 | 2PERn2 | GND | 2PETp3 | 2PETn3 | GND |

| 10  | 3РЕТр0 | 3PETn0 | GND | 3PERp0 | 3PERn0 | GND | 2PERp3 | 2PERn3 | GND |

Table 7. XP4 Connector Pinout for the System Controller Slot

| Pin | Z   | A         | В         | С         | D        | E         | F   |

|-----|-----|-----------|-----------|-----------|----------|-----------|-----|

| 1   | GND | GA4       | GA3       | GA2       | GA1      | GA0       | GND |

| 2   | GND | 5Vaux     | GND       | SYSEN#    | WAKE#    | ALERT#    | GND |

| 3   | GND | RSV       | RSV       | RSV       | RSV      | RSV       | GND |

| 4   | GND | RSV       | RSV       | RSV       | RSV      | RSV       | GND |

| 5   | GND | PXI_TRIG3 | PXI_TRIG4 | PXI_TRIG5 | GND      | PXI_TRIG6 | GND |

| 6   | GND | PXI_TRIG2 | GND       | RSV       | PXI_STAR | PXI_CLK10 | GND |

| 7   | GND | PXI_TRIG1 | PXI_TRIG0 | RSV       | GND      | PXI_TRIG7 | GND |

| 8   | GND | RSV       | GND       | RSV       | RSV      | PXI_LBR6  | GND |

# **System Timing Slot Pinouts**

Table 8. TP1 Connector Pinout for the System Timing Slot

| Pin | A             | В             | ab  | C          | D          | cd  | E  | F  | ef  |

|-----|---------------|---------------|-----|------------|------------|-----|----|----|-----|

| 1   | PXIe_DSTARA3+ | PXIe_DSTARA3- | GND | NC         | NC         | GND | NC | NC | GND |

| 2   | PXIe_DSTARC4+ | PXIe_DSTARC4- | GND | PXI_STAR12 | PXI_STAR13 | GND | NC | NC | GND |

| 3   | PXIe_DSTARB4+ | PXIe_DSTARB4- | GND | NC         | NC         | GND | NC | NC | GND |

| 4   | PXIe_DSTARA4+ | PXIe_DSTARA4- | GND | NC         | NC         | GND | NC | NC | GND |

| 5   | PXIe_DSTARC5+ | PXIe_DSTARC5- | GND | PXI_STAR14 | PXI_STAR15 | GND | NC | NC | GND |

| 6   | PXIe_DSTARB5+ | PXIe_DSTARB5- | GND | NC         | NC         | GND | NC | NC | GND |

| 7   | PXIe_DSTARA5+ | PXIe_DSTARA5- | GND | NC         | NC         | GND | NC | NC | GND |

| 8   | PXIe_DSTARC6+ | PXIe_DSTARC6- | GND | PXI_STAR16 | RSV        | GND | NC | NC | GND |

| 9   | PXIe_DSTARB6+ | PXIe_DSTARB6- | GND | NC         | NC         | GND | NC | NC | GND |

| 10  | PXIe_DSTARA6+ | PXIe_DSTARA6- | GND | NC         | NC         | GND | NC | NC | GND |

Table 9. TP2 Connector Pinout for the System Timing Slot

| Pin | A             | В             | ab  | С             | D             | cd  | E              | F              | ef  |

|-----|---------------|---------------|-----|---------------|---------------|-----|----------------|----------------|-----|

| 1   | NC            | NC            | GND | PXIe_DSTARC8+ | PXIe_DSTARC8- | GND | PXIe_DSTARB8+  | PXIe_DSTARB8-  | GND |

| 2   | NC            | NC            | GND | NC            | NC            | GND | PXIe_DSTARA8+  | PXIe_DSTARA8-  | GND |

| 3   | NC            | NC            | GND | PXIe_DSTARC1+ | PXIe_DSTARC1- | GND | NC             | NC             | GND |

| 4   | PXIe_DSTARB1+ | PXIe_DSTARB1- | GND | PXI_STAR0     | PXI_STAR1     | GND | NC             | NC             | GND |

| 5   | PXIe_DSTARA1+ | PXIe_DSTARA1- | GND | PXI_STAR2     | PXI_STAR3     | GND | NC             | NC             | GND |

| 6   | PXIe_DSTARC2+ | PXIe_DSTARC2- | GND | PXI_STAR4     | PXI_STAR5     | GND | NC             | NC             | GND |

| 7   | PXIe_DSTARB2+ | PXIe_DSTARB2- | GND | PXI_STAR6     | PXI_STAR7     | GND | NC             | NC             | GND |

| 8   | PXIe_DSTARA2+ | PXIe_DSTARA2- | GND | PXI_STAR8     | PXI_STAR9     | GND | PXIe_DSTARC11+ | PXIe_DSTARC11- | GND |

| 9   | PXIe_DSTARC3+ | PXIe_DSTARC3- | GND | PXI_STAR10    | PXI_STAR11    | GND | PXIe_DSTARA11+ | PXIe_DSTARA11- | GND |

| 10  | PXIe_DSTARB3+ | PXIe_DSTARB3- | GND | NC            | NC            | GND | PXIe_DSTARB11+ | PXIe_DSTARB11- | GND |

Table 10. XP3 Connector Pinout for the System Timing Slot

| Pin | A            | В            | ab  | С             | D             | cd  | E            | F            | ef  |

|-----|--------------|--------------|-----|---------------|---------------|-----|--------------|--------------|-----|

| 1   | PXIe_CLK100+ | PXIe_CLK100- | GND | PXIe_SYNC100+ | PXIe_SYNC100- | GND | PXIe_DSTARC+ | PXIe_DSTARC- | GND |

| 2   | PRSNT#       | PWREN#       | GND | PXIe_DSTARB+  | PXIe_DSTARB-  | GND | PXIe_DSTARA+ | PXIe_DSTARA- | GND |

| 3   | SMBDAT       | SMBCLK       | GND | RSV           | RSV           | GND | RSV          | RSV          | GND |

| 4   | MPWRGD*      | PERST#       | GND | RSV           | RSV           | GND | 1RefClk+     | 1RefClk-     | GND |

| 5   | 1PETp0       | 1PETn0       | GND | 1PERp0        | 1PERn0        | GND | 1PETp1       | 1PETn1       | GND |

| 6   | 1PETp2       | 1PETn2       | GND | 1PERp2        | 1PERn2        | GND | 1PERp1       | 1PERn1       | GND |

| 7   | 1PETp3       | 1PETn3       | GND | 1PERp3        | 1PERn3        | GND | 1PETp4       | 1PETn4       | GND |

| 8   | 1PETp5       | 1PETn5       | GND | 1PERp5        | 1PERn5        | GND | 1PERp4       | 1PERn4       | GND |

| 9   | 1PETp6       | 1PETn6       | GND | 1PERp6        | 1PERn6        | GND | 1PETp7       | 1PETn7       | GND |

| 10  | RSV          | RSV          | GND | RSV           | RSV           | GND | 1PERp7       | 1PERn7       | GND |

Table 11. XP4 Connector Pinout for the System Timing Slot

| Pin | z   | A              | В         | С         | D            | Е         | F   |

|-----|-----|----------------|-----------|-----------|--------------|-----------|-----|

| 1   | GND | GA4            | GA3       | GA2       | GA1          | GA0       | GND |

| 2   | GND | 5Vaux          | GND       | SYSEN#    | WAKE#        | ALERT#    | GND |

| 3   | GND | 12V            | 12V       | GND       | GND          | GND       | GND |

| 4   | GND | GND            | GND       | 3.3V      | 3.3V         | 3.3V      | GND |

| 5   | GND | PXI_TRIG3      | PXI_TRIG4 | PXI_TRIG5 | GND          | PXI_TRIG6 | GND |

| 6   | GND | PXI_TRIG2      | GND       | ATNLED    | PXI_CLK10_IN | PXI_CLK10 | GND |

| 7   | GND | PXI_TRIG1      | PXI_TRIG0 | ATNSW#    | GND          | PXI_TRIG7 | GND |

| 8   | GND | PXIe_SYNC_CTRL | GND       | RSV       | PXI_LBL6     | PXI_LBR6  | GND |

# **Hybrid Slot Pinouts**

Table 12. P1 Connector Pinout for the Hybrid Slot

| Pin   | Z   | A        | В        | С        | D       | E        | F   |

|-------|-----|----------|----------|----------|---------|----------|-----|

| 25    | GND | 5V       | REQ64#   | ENUM#    | 3.3V    | 5V       | GND |

| 24    | GND | AD[1]    | 5V       | V(I/O)   | AD[0]   | ACK64#   | GND |

| 23    | GND | 3.3V     | AD[4]    | AD[3]    | 5V      | AD[2]    | GND |

| 22    | GND | AD[7]    | GND      | 3.3V     | AD[6]   | AD[5]    | GND |

| 21    | GND | 3.3V     | AD[9]    | AD[8]    | M66EN   | C/BE[0]# | GND |

| 20    | GND | AD[12]   | GND      | V(I/O)   | AD[11]  | AD[10]   | GND |

| 19    | GND | 3.3V     | AD[15]   | AD[14]   | GND     | AD[13]   | GND |

| 18    | GND | SERR#    | GND      | 3.3V     | PAR     | C/BE[1]# | GND |

| 17    | GND | 3.3V     | IPMB_SCL | IPMB_SDA | GND     | PERR#    | GND |

| 16    | GND | DEVSEL#  | GND      | V(I/O)   | STOP#   | LOCK#    | GND |

| 15    | GND | 3.3V     | FRAME#   | IRDY#    | BD_SEL# | TRDY#    | GND |

| 12–14 |     |          |          | Key Area |         |          |     |

| 11    | GND | AD[18]   | AD[17]   | AD[16]   | GND     | C/BE[2]# | GND |

| 10    | GND | AD[21]   | GND      | 3.3V     | AD[20]  | AD[19]   | GND |

| 9     | GND | C/BE[3]# | IDSEL    | AD[23]   | GND     | AD[22]   | GND |

| 8     | GND | AD[26]   | GND      | V(I/O)   | AD[25]  | AD[24]   | GND |

| 7     | GND | AD[30]   | AD[29]   | AD[28]   | GND     | AD[27]   | GND |

| 6     | GND | REQ#     | GND      | 3.3V     | CLK     | AD[31]   | GND |

| 5     | GND | BRSVP1A5 | BRSVP1B5 | RST#     | GND     | GNT#     | GND |

| 4     | GND | IPMB_PWR | HEALTHY# | V(I/O)   | INTP    | INTS     | GND |

| 3     | GND | INTA#    | INTB#    | INTC#    | 5V      | INTD#    | GND |

| 2     | GND | TCK      | 5V       | TMS      | TDO     | TDI      | GND |

| 1     | GND | 5V       | -12V     | TRST#    | +12V    | 5V       | GND |

Table 13. XP3 Connector Pinout for the Hybrid Slot

| Pin | A            | В            | ab  | С             | D             | cd  | Е            | F            | ef  |

|-----|--------------|--------------|-----|---------------|---------------|-----|--------------|--------------|-----|

| 1   | PXIe_CLK100+ | PXIe_CLK100- | GND | PXIe_SYNC100+ | PXIe_SYNC100- | GND | PXIe_DSTARC+ | PXIe_DSTARC- | GND |

| 2   | PRSNT#       | PWREN#       | GND | PXIe_DSTARB+  | PXIe_DSTARB-  | GND | PXIe_DSTARA+ | PXIe_DSTARA- | GND |

| 3   | SMBDAT       | SMBCLK       | GND | RSV           | RSV           | GND | RSV          | RSV          | GND |

| 4   | MPWRGD*      | PERST#       | GND | RSV           | RSV           | GND | 1RefClk+     | 1RefClk-     | GND |

| 5   | 1PETp0       | 1PETn0       | GND | 1PERp0        | 1PERn0        | GND | 1PETp1       | 1PETn1       | GND |

| 6   | 1PETp2       | 1PETn2       | GND | 1PERp2        | 1PERn2        | GND | 1PERp1       | 1PERn1       | GND |

| 7   | 1PETp3       | 1PETn3       | GND | 1PERp3        | 1PERn3        | GND | 1PETp4       | 1PETn4       | GND |

| 8   | 1PETp5       | 1PETn5       | GND | 1PERp5        | 1PERn5        | GND | 1PERp4       | 1PERn4       | GND |

| 9   | 1PETp6       | 1PETn6       | GND | 1PERp6        | 1PERn6        | GND | 1PETp7       | 1PETn7       | GND |

| 10  | RSV          | RSV          | GND | RSV           | RSV           | GND | 1PERp7       | 1PERn7       | GND |

Table 14. XP4 Connector Pinout for the Hybrid Slot

| Pin | Z   | A         | В         | С         | D        | E         | F   |

|-----|-----|-----------|-----------|-----------|----------|-----------|-----|

| 1   | GND | GA4       | GA3       | GA2       | GA1      | GA0       | GND |

| 2   | GND | 5Vaux     | GND       | SYSEN#    | WAKE#    | ALERT#    | GND |

| 3   | GND | 12V       | 12V       | GND       | GND      | GND       | GND |

| 4   | GND | GND       | GND       | 3.3V      | 3.3V     | 3.3V      | GND |

| 5   | GND | PXI_TRIG3 | PXI_TRIG4 | PXI_TRIG5 | GND      | PXI_TRIG6 | GND |

| 6   | GND | PXI_TRIG2 | GND       | ATNLED    | PXI_STAR | PXI_CLK10 | GND |

| 7   | GND | PXI_TRIG1 | PXI_TRIG0 | ATNSW#    | GND      | PXI_TRIG7 | GND |

| 8   | GND | RSV       | GND       | RSV       | PXI_LBL6 | PXI_LBR6  | GND |

National Instruments, NI, ni.com, and LabVIEW are trademarks of National Instruments Corporation. Refer to the *Terms of Use* section on ni.com/legal for more information about National Instruments trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies. For patents covering National Instruments products/technology, refer to the appropriate location: **Help»Patents** in your software, the patents.txt file on your media, or the *National Instruments Patent Notice* at ni.com/patents.