# INTERBUS

User Manual

Device Driver Development Kit for Controller Boards in PC Systems With PCI Bus

Designation: IBS PCI DDK UM E Order No.: 26 98 16 4

onlinecomponents.com

# INTERBUS

## User Manual

# Device Driver Development Kit for Controller Boards in PC Systems With PCI Bus

20

Designation: IBS PCI DDK UM E

Revision: A

Order No.: 26 98 16 4

This user manual is valid for: IBS PCI SC/I-T IBS PCI SC/RI/I-T IBS PCI SC/RI-LK

Order No. 27 25 26 0 Order No. 27 30 08 0 Order No. 27 30 18 7

© Phoenix Contact 08/2001

6189A

onlinecomponents.com

# Please Observe the Following Notes:

In order to guarantee the safe use of your device, we recommend that you read this manual carefully. The following notes give you information on how to use this manual.

#### **Requirements of the User Group**

The use of products described in this manual is oriented exclusively to qualified application programmers and software engineers, who are familiar with automation safety concepts and applicable national standards. Phoenix Contact assumes no liability for erroneous handling or damage to products from Phoenix Contact or external products resulting from disregard of information contained in this manual.

#### **Explanation of Symbols Used**

The *attention* symbol refers to an operating procedure which, if not carefully followed, could result in damage to equipment or personal injury.

The *note* symbol informs you of conditions that must strictly be observed to achieve error-free operation. It also gives you tips and advice on hardware and software optimization to save you extra work.

The *text* symbol refers to detailed sources of information (manuals, data sheets, literature, etc.) on the subject matter, product, etc. This text also provides helpful information for the orientation in the manual.

#### We Are Interested in Your Opinion

We are constantly attempting to improve the quality of our manuals.

Should you have any suggestions or recommendations for improvement of the contents and layout of our manuals, we would appreciate it if you would send us your comments. Please use the universal fax form at the end of the manual for this.

#### Statement of Legal Authority

This manual, including all illustrations contained herein, is copyright protected. Use of this manual by any third party in departure from the copyright provision is forbidden. Reproduction, translation, or electronic or photographic archiving or alteration requires the express written consent of Phoenix Contact. Violations are liable for damages.

Phoenix Contact reserves the right to make any technical changes that serve the purpose of technical progress.

All product names used are trademarks of the respective organizations.

#### Internet

<text> Up-to-date information on Phoenix Contact products can be found on the

#### Terms of Delivery and Payment for Software

Using the DDK sources indicates your acceptance of the following Terms and Conditions. If you do not wish to accept these Terms and Conditions, please send the complete unopened diskette package and all accompanying material (including written material and packing) against reimbursement of the payment made. Phoenix Contact points out that no General Terms of Contract of the customer (hereinafter referred to as the Registered User) can be recognized. The inclusion of such General Terms of Contract is hereby explicitly contradicted.

#### Terms of Contract

#### § 1 Subject matter

The subject matter of this contract is the program stored on the data carrier including the written material also supplied (program description, operating instructions etc.), hereinafter referred to as "Software".

#### § 2 Scope of the license

1.In the event of acquisition of a single license, the following paragraph regulates the scope of the license.

- Phoenix Contact grants the Registered User the single, non-exclusive right (hereinafter referred to as license) to use the Software on one single computer. The Registered User may also install the Software on more than one computer. However, the Software may only be used on one computer at a time. Any use exceeding this scope is not permitted unless agreements have been reached concerning the acquisition of supplementary licenses or a company license (cf. Items 2 and 3). The license is a single license if described as such in acknowledgement of order and invoice.

- 2. In the event of acquisition of supplementary licenses, the following paragraph regulates the scope of the license.

The Registered User is granted the right to make copies of previously acquired Software (single license) and to use these copies. The number of permitted copies is derived from the number of supplementary licenses acquired by the Registered User. The Registered User undertakes to identify the Software products placed at his disposal and put into circulation by him. To identify the data carriers, the Registered User shall receive a set of appropriate serial numbers. The number of serial numbers corresponds to the number of permitted copies. Each copy may only be used once at a time (cf. § 2 Item 1). Supplementary licenses may only be acquired by Registered Users that are in possession of a basic license for the Software in question. The Registered User is obliged to keep records of the whereabouts of all copies and to allow Phoenix Contact to inspect these records on request.

The license is a supplementary license if described as such in acknowledgement of order and invoice. 3. In the event of acquisition of a company license, the following paragraph regulates the scope of the license.

Registered Users that have acquired a company license are granted the right to make any number of copies of the Software placed at their disposal in their own company, and to use it on any number of computers at the same time.

The license is a company license if described as such in acknowledgement of order and invoice. Use is only permitted in one location.

#### § 3 Copyright

The Software is the property of Phoenix Contact. The acquisition of rights to the Software itself going beyond the license regulated in this contract is not associated with this. In particular, Phoenix Contact reserves all rights to copying, publication, processing and exploitation.

The Registered User recognizes that he acquires no rights whatsoever to the Software products described going beyond this agreement, in particular that he acquires no commercial rights to source code.

2. The Software is legally protected against copying. The Registered User may make up to three backup copies for archiving purposes. No alphanumerical identification marks, brand names, trademarks or copyright notices may be removed; these must be transferred to the copies. Neither manuals nor written materials may be copied, unless Phoenix Contact has explicitly authorized the Registered User to do so within the framework of a supplementary or company license. With the exception of the provisions stated in the following paragraph, the Software may be neither loaned, hired nor otherwise passed on to third parties.

- 3. The rights ensuing from this licensing agreement may be transferred to a third party on condition that the terms and conditions of this licensing agreement are explicitly recognized in writing and that the Registered User hands over the complete program package including all diskettes (and including any backup copies made) and written materials, and that the Registered User completely deletes the program version from all hard disks in his computer. The transfer must comprise the current version (update) and all previous versions. Phoenix Contact must be notified of the transfer of the licensing rights, with the name and address of the recipient. A copy of the declaration of acceptance must be enclosed with the notification. Insofar as no other written agreement has been reached, this obligation also extends to subsidiary companies, other locations, other places of business and other companies of the Registered User.

- The Registered User must not make any information of a technical or commercial nature obtained from Phoenix Contact, hereinafter referred to as "Information", or any development results accessible to third parties.

Documentation supplied by Phoenix Contact, as well as the Software and the products derived from said Software may only be passed on within the framework of the above licensing agreement. The confidentiality obligation also applies after termination of the contract. However, it does not apply to information which is generally known or which on receipt could be proved to be part of the internal state of technology of the Registered User or which became incorporated later in this internal state of technology, irrespective of the present contract.

#### § 4 Decompilation and modifications to the program

- 1. The decompilation of the program code provided into other code forms as well as other means of retracing the various programming stages of the Software (reverse engineering), including a program modification, are permitted for the Registered User's own use, in particular for purposes of fault correction, for establishing the interoperability and compatibility or expansion of the range of functions. Within the meaning of this provision, own use includes in particular private use by the Registered User. Own use, however, also includes use for professional or profit-making purposes, insofar as this is restricted to the Registered User's or his employees' own use and is not commercially exploited externally in any way.

- 2. The appropriate actions may only be carried out by commercial third parties in potential competition with Phoenix Contact if Phoenix Contact does not wish to carry out the required program modifications against reasonable compensation. Phoenix Contact must be given an adequate period of time to check the acquisition of the order by the third party, and must be informed of the name of the third party.

- 3. Insofar as the stated actions are carried out for commercial reasons, they are only permitted if they are essential for the creation, maintenance or proper functioning of an independently created interoperable

- program and the necessary information has not yet been published and is not otherwise accessible.

Under no circumstances may copyright notices, serial numbers or other characteristics for identifying the program be removed or modified.

#### § 5 Guarantee

- 1. This Software has been produced with the greatest possible care. It is, however, known to the Registered User that with the present state of technology it is not possible to produce Software in such a way that it works without errors in all applications and combinations.

- 2. The guarantee period is six months, beginning with the delivery of the Software.

- 3. Phoenix Contact guarantees that at the time of delivery, the material of the data carriers on which the Software is stored and the documentation supplied are free from faults. Should the data carriers or the documentation supplied be faulty, the Registered User can demand a replacement delivery during the agreed guarantee period as stated above, on condition that he returns the defective material, including any backup copies made, and the written material.

- 4. If during the use of the Software by the Registered User for the contractually agreed and intended purpose considerable deviations from the performance description prepared by Phoenix Contact should result, Phoenix Contact has, at its own discretion, the right to rectify faults twice or to provide replacements twice. If Phoenix Contact does not succeed in eliminating the considerable deviations from the performance description within a reasonable period of time through rectification or replacement, or in avoiding them in such a way that the Registered User can use the Software in accordance with the contract, the Registered User can demand a reduction of payment (price reduction) or cancellation of this contract (rescission). In the latter case the Registered User must hand back any copies he may have made. \_Failure of the rectification or oreplacement can only be presumed if the Registered User provides Phoenix Contact with verifiable documentation concerning the type and occurrence of deviations from the performance description (reproducible fault log) and if in spite of this documentation rectification is not possible, is refused by Phoenix Contact or is unreasonably delayed, if there are justified doubts concerning the prospects of success or if unacceptability prevails for other reasons.

- 5. Fault diagnosis and rectification within the framework of the guarantee shall be effected on the premises of the Registered User or of Phoenix Contact, at the discretion of Phoenix Contact. If a repair or service agreement has been reached between the Registered User and Phoenix Contact, the fault diagnosis and rectification may also be effected at the installation site of the computer on which the Software is being run in accordance with § 2 and § 3, by arrangement with the Registered User.\_Phoenix Contact shall be given the documentation and information which is in the possession of the Registered User and which is required to rectify the fault. If Phoenix Contact is to rectify the fault on the premises of the Registered User, the Registered User shall provide, free of charge, the necessary hardware and software as well as the other necessary operating conditions together with suitable operating personnel in such a way that the work can be carried out quickly. If no repair or service agreement has been reached, the Registered User shall reimburse Phoenix Contact for expenses for travelling and board for personnel sent to the installation site of the computer on which the licensed Software is being run.\_No other guarantee claims can be accepted.

- 6. Notwithstanding the above agreements, it is agreed that software identified as "BETA" or "ALPHA" is completely excluded from the guarantee, since this is only a preliminary or test version which does not correspond to the final product.

#### § 6 Liability

- 1. Phoenix Contact accepts no liability for the Software meeting the requirements of the Registered User or working together with other programs selected by him.

- 2. Phoenix Contact accepts unlimited liability for damage due to deficiencies in title and absence of warranted qualities. Liability for initial inability is restricted to the purchase price as well as to such damage, which can typically be expected within the framework of a software transfer. In other respects, Phoenix Contact only accepts liability for intention and gross negligence, unless an obligation whose observance is of particular importance for the achievement of the contractual purpose (cardinal obligation) is violated. In the event of violation of a cardinal obligation, the limitation of liability for initial inability is applicable.

If damage has been caused intentionally or through gross negligence, the amount of our liability is limited to the damage foreseeable under normal circumstances as a consequence of this obligation violation.

Notwithstanding the above agreements, it is agreed that no liability whatsoever can be accepted for software identified as "BETA" or "ALPHA" (cf. § 5.6)

#### § 7 Prices

- 1. In accordance with its current price list, Phoenix Contact shall charge separately for

- support in commissioning the Software

- support in the analysis and rectification of faults arising through improper handling or for other reasons not arising from the Software.

#### § 8 Compensation

The Registered User is fully liable to Phoenix Contact for all damage resulting from violations of this licensing agreement or of copyright.

#### § 9 Termination

- 1. The Registered User can terminate the contract, insofar as it is unlimited in time, in whole or in part, with a period of notice of six months as from the end of each month. If a single license fee was paid for the transfer of the Software, this is not returnable.

- 2. On termination of the contract, the Registered User is obliged to return to Phoenix Contact the original as well as all copies and part-copies, as well as modified copies and copies combined with other program material, or verifiably to destroy them. The same applies for the program documentation and other documents provided.

- 3. The retention of an archive copy for backup purposes requires a separate written agreement.

#### § 10 Export

1

The export of software, including the relevant data and documents, may require official approval - e.g. because of its type or its intended purpose. In the event of the sale of software to third parties, the Registered User shall in each case obtain the required export authorization on his own responsibility and effect delivery only in accordance with such authorization.

#### § 11 Ancillary agreements

Ancillary agreements and alterations to the licensing conditions must be made in writing.

#### § 12 Place of jurisdiction, choice of applicable law

- 1. For all disputes arising from the contractual relationship, the court at the headquarters of Phoenix Contact is competent if the Registered User is a merchant registered in the Commercial Register, a legal person under public law or if a special fund under public law is concerned.

- 2. The law of the Federal Republic of Germany applies for all legal relationships between the parties

<text>

# Table of Contents

| 1 Introduction             |                                                 | 1-3     |

|----------------------------|-------------------------------------------------|---------|

| 1.1                        | Files on the Disk                               | 1-4     |

| 1.2                        | Conditions of Support                           | 1-7     |

|                            | 1.2.1 Chargeable Support Services               | 1-8     |

| 2 Structure and Interfaces | s of INTERBUS Controller Boards                 | 2-3     |

| 2.1                        | PCI Register                                    | 2-4     |

| 2.2                        | Host Interface for INTERBUS Controller Boards   | 2-6     |

|                            | 2.2.1 Hardware Settings of Controller Boards    | 2-6     |

|                            | 2.2.2 I/O Register                              | 2-8     |

| 2.3                        | Multi-Port Memory (MPM)                         | 2-16    |

|                            | 2.3.1 MPM Address Area                          | 2-19    |

|                            | 2.3.2 Segmentation of the SRAM in the MPM       | 2-20    |

|                            | 2.3.3 MPM Communication Options                 | 2-21    |

|                            | 2.3.4 MPM Hardware Register                     | 2-24    |

|                            | 2.3.5 MPM Software Register                     | 2-48    |

| 3 Data Exchange via the I  | Data Area                                       | 3-3     |

| 3.1                        | Operating Modes                                 |         |

|                            | 3.1.1 Asynchronous Mode                         | 3-5     |

|                            | 3.1.2 Asynchronous Mode With Synchronization Pu | ılse3-5 |

| 4 Communication via the    | Mailbox Interface                               | 4-3     |

| 5 Architecture and Structu | ure of a Device Driver                          | 5-3     |

| 5.1                        | General                                         | 5-3     |

| 5.2                        | Basic Structure of the Driver                   | 5-4     |

| 5.3                        | Description of Functions                        | 5-8     |

|                            | 5.3.1 Initialization (initBoard)                |         |

|                           |       | 5.3.2    | Open Data Channel (openDevice)5-11                  |

|---------------------------|-------|----------|-----------------------------------------------------|

|                           |       | 5.3.3    | Close Data Channel (closeDevice)5-12                |

|                           |       | 5.3.4    | Write Process Data (writeDTI)5-13                   |

|                           |       | 5.3.5    | Read Process Data (readDTI)5-14                     |

|                           |       | 5.3.6    | Send Message (writeMXI)5-15                         |

|                           |       | 5.3.7    | Read Message (readMXI)5-16                          |

|                           |       | 5.3.8    | Interrupt Service Routine (intrServiceFunction)5-18 |

|                           |       | 5.3.9    | Device IO Control (devIOCtrl)5-19                   |

|                           |       | 5.3.10   | Utilities5-21                                       |

|                           |       | 5.3.11   | Data Structures Used5-29                            |

|                           |       |          |                                                     |

| <b>6</b> ToDo (Adaptation | to Op | erating  | Systems)                                            |

|                           | 6.1   | File Str | uctures in the Driver 6-3                           |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

|                           |       |          |                                                     |

# Section 1

This section informs you about

|              |         | ,       | ives and structure of this user manual. |  |

|--------------|---------|---------|-----------------------------------------|--|

| Introduction | <br>1.1 | Files c | on the Disk                             |  |

|              | 1.2     |         | tions of Support                        |  |

|              |         | 1.2.1   | Chargeable Support Services             |  |

|              |         |         | Chargeable Support Services             |  |

|              |         |         |                                         |  |

|              |         |         |                                         |  |

|              |         |         |                                         |  |

|              |         |         |                                         |  |

|              |         |         |                                         |  |

DPHŒNIX CONTACT

6189A

minecomponents.com

## **1** Introduction

This manual and the associated C driver source code can be used to develop specific device drivers to link Generation 4 INTERBUS controller boards to any PC operating system. IBS PCI SC/I-T, IBS PCI SC/RI/I-T, and IBS PCI SC/RI-LK controller boards (referred to as IBS PCI controller boards in the following) are used to interface the open fieldbus system (standardized as IEC 61158) to PC systems (referred to as host system in the following) with PCI bus.

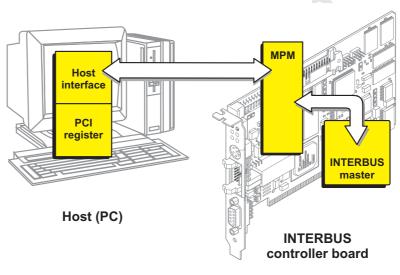

The host system and INTERBUS are coupled by means of a shared memory area designed as a 2-device Multi-Port Memory (MPM). An independent INTERBUS master, based on a MC68332 microcontroller and a protocol chip, is incorporated on the controller board.

This document first explains the basic, specific functions of the controller boards, and goes on to explain the general architecture of the MPM. It concludes with some notes on creating a device driver.

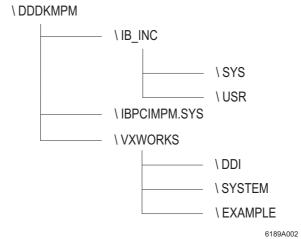

## 1.1 Files on the Disk

The disk contains the following directories:

| Table 1-1 | Directory contents |

|-----------|--------------------|

|-----------|--------------------|

| Directory Name | Contents                                              |

|----------------|-------------------------------------------------------|

| IBPCIMPM.SYS   | Contains the C source code for the driver.            |

| SYS            | Contains adaptations to various systems               |

| USR            | Contains include files for various systems            |

| DDI            | Contains the Device Driver Interface for VxWorks      |

| SYSTEM         | VxWorks system initialization for the IBS PCI SC/     |

| EXAMPLE        | Contains example programs that use a finished driver. |

#### Introduction

| File Name  | Contents                                                          |

|------------|-------------------------------------------------------------------|

| startup.c  | Initialization of hardware and software                           |

| drvinits.c | Driver initialization routines                                    |

| vxwsys.c   | Operating system functions/routines for VxWorks                   |

| lbpcidrv.c | Functions/routines for PCI access                                 |

| evthndg.c  | Functions/routines for event handling                             |

| drvlimit.h | Limitation constants (maximum values, etc.)                       |

| errlog.h   | Macros, constants, etc. for error logging and debugging           |

| lbpcidrv.c | Functions/routines for PCI access                                 |

| os_adapt.h | Operating system-dependent data structures, macros, and constants |

| os_inc.h   | Load operating system-dependent headers                           |

| pci_drv.h  | Constants and structures for working with PCI devices             |

| pcimsg.h   | Constants for error messages                                      |

| vxw_data.h | Constants and data structures for VXWorks tasks and priorities    |

#### Files in the "IBPCIMPM.SYS" directory Table 1-2

# Table 1-3 Files in the "IB\_INC\SYS" directory

| Table 1-3 Files in the "IB_INC\SYS" directory |                                                               |  |

|-----------------------------------------------|---------------------------------------------------------------|--|

| File Name                                     | Contents                                                      |  |

| compiler.h                                    | Compiler setting definitions                                  |  |

| mpm40.h                                       | Definitions of the MPM register addresses and their bit masks |  |

| loctl40.h                                     | Definitions for the devIOCtrl driver function                 |  |

| drv_dbg.h                                     | Defines, typedef, and prototypes for DriverDebugInfo commands |  |

| File Name  | Contents                                                                                      |

|------------|-----------------------------------------------------------------------------------------------|

| stdtypes.h | Generally valid standard type definitions                                                     |

| ddi_err.h  | Definitions of possible driver error messages                                                 |

| ddi_usr.h  | Defines, typedef, prototypes for DDI basic functions (without I/O control and management)     |

| ibs_util.h | Declarations of the additional DDI functions, e.g., watchdog, read diagnostic registers, etc. |

| ibddivxw.h | DDI for VxWorks                                                                               |

| ddi_macr.h | Macros for messages/data conversion                                                           |

| Svc_code.h | IBS service codes (send/receive)                                                              |

#### Table 1-4 Files in the "IB\_INC\USR" directory

#### Table 1-5 Files in the "VXWORX\EXAMPLE" directory

| File Name | Contents                                         |

|-----------|--------------------------------------------------|

| simple.c  | Example program for application of DDI functions |

#### Table 1-6 Files in the "VXWORX\SYSTEM" directory

| File Name    | Contents                      |

|--------------|-------------------------------|

| ibspciinit.c | VxWorks system initialization |

#### Table 1-7 Files in the "VXWORX\DDI" directory

| File Name  | Contents                                  |

|------------|-------------------------------------------|

| ibddivxw.c | Device Driver Interface (DDI) for VxWorks |

## 1.2 Conditions of Support

Upon purchasing this product, you are entitled to comprehensive support during implementation. This support is available to you free of charge, if required, for 30 days following registration of the product. This free support will only be provided via a personal e-mail address, which will be created for you.

#### How Can You Obtain This Support?

- 1. Register at the following Internet address: http://request.phoenixcontact.com/req\_eldo/pciddk\_d/ddkreg.htm

- 2. Please complete the registration form in full.

- 3. As soon as we receive your registration, you will receive confirmation together with your personal support e-mail address via e-mail.

#### Points to Note

Our free support is available during normal office hours (Germany) and only via your personal e-mail address.

Free support is available for 30 calendar days, commencing on the date of the confirmation of your registration. The support period may be extended for a fee. For details, please refer to Section "Chargeable Support Services" on page 1-8.

Please ensure that you only register the product when you wish to work continuously on the implementation.

In general, a fee is charged for telephone and on-site support. For details, please refer to Section "Chargeable Support Services" on page 1-8.

In some individual cases, it may be necessary for Phoenix Contact to telephone you, however, you will not be charged for this.

Our support can only be provided for sources supplied by Phoenix Contact. As we are not familiar with, and generally do not have access to, your development environment, Phoenix Contact does not accept any responsibility or liability for any implementation work affected by this environment.

Phoenix Contact only accepts liability for products supplied within the scope of legal requirements for product liability or according to the general delivery and payment conditions. Phoenix Contact does not accept any liability for driver implementation developed by you or by a third party.

Phoenix Contact does not accept any responsibility for development, testing, validation, release, and support of your driver implementation.

#### 1.2.1 Chargeable Support Services

Using the free support service available via your personal e-mail address, you can, if necessary, take advantage of other support services. A fee is charged for these services and we require you to place a written or verbal order.

Please contact the relevant person in the sales department or your representative. A direct order cannot be made via your e-mail address.

Extension of the e-mail account for an additional 30 days

Order No. 27 10 26 2

Order Designation IBS PCI DDK SUPPORT EXT

If necessary, we can offer you additional support services tailored to your requirements. Please contact the relevant person in the sales department or your representative. We will then be happy to supply you with a personal quotation.

# Section 2

This section informs you about

- the PCI register,

- the host interface and

- the MPM for INTERBUS controller boards. \_

| Structure and Interfaces of | INTEF           | RBUS Controller Boards2-3                 |  |

|-----------------------------|-----------------|-------------------------------------------|--|

| 2.1                         | PCI Register2-4 |                                           |  |

| 2.2                         | Host In         | terface for INTERBUS Controller Boards2-6 |  |

|                             | 2.2.1           | Hardware Settings of Controller Boards2-6 |  |

|                             | 2.2.2           | I/O Register2-8                           |  |

| 2.3                         | Multi-P         | ort Memory (MPM)2-16                      |  |

|                             | 2.3.1           | MPM Address Area2-19                      |  |

|                             | 2.3.2           | Segmentation of the SRAM in the MPM2-20   |  |

|                             | 2.3.3           | MPM Communication Options2-21             |  |

|                             | 2.3.4           | MPM Hardware Register2-24                 |  |

|                             | 2.3.5           | MPM Software Register2-48                 |  |

|                             |                 |                                           |  |

|                             |                 |                                           |  |

|                             |                 |                                           |  |

|                             |                 |                                           |  |

|                             |                 |                                           |  |

|                             |                 |                                           |  |

|                             |                 |                                           |  |

|                             |                 |                                           |  |

|                             |                 |                                           |  |

|                             |                 |                                           |  |

DPHŒNIX CONTACT

6189A

minecomponents.com

# 2 Structure and Interfaces of INTERBUS Controller Boards

PCI controller boards are directly connected with the host system using PCI connectors. This hardware interface has (according to the PCI bus specification 2.2) a 32-bit address and data bus. It has control lines in addition to the address and data lines. The controller boards support interrupt operation.

A detailed description of the controller board hardware and its installation in the host system can be found in the *IBS PCI SC QS UM E* Quick Start Guide (Order No. 26 98 14 8).

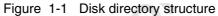

The software interface of the controller boards to the host system consists of a 16-byte window in the I/O area and a 256-kbyte window in the standard address area (memory area). The base addresses of both windows are specified by the system BIOS.

Figure 2-1 Controller board address windows in the host system

6189A

## 2.1 PCI Register

PCI registers integrate the controller boards into a PCI bus system. The following table shows the arrangement of the PCI registers and their controller board-specific settings.

| Contact)<br>ster<br>ision ID<br>W Rev)<br>che line<br>size |  |  |  |  |  |  |

|------------------------------------------------------------|--|--|--|--|--|--|

| ster<br>ision ID<br>V Rev)<br>che line                     |  |  |  |  |  |  |

| <mark>ision ID</mark><br><mark>V Rev)</mark><br>che line   |  |  |  |  |  |  |

| <mark>V Rev)</mark><br>che line                            |  |  |  |  |  |  |

| che line                                                   |  |  |  |  |  |  |

|                                                            |  |  |  |  |  |  |

| size                                                       |  |  |  |  |  |  |

|                                                            |  |  |  |  |  |  |

| Base address register 0                                    |  |  |  |  |  |  |

| (here: I/O address for the host interface register)        |  |  |  |  |  |  |

| Base address register 1                                    |  |  |  |  |  |  |

| (here: addresses for MPM and NV-RAM, 256 kbytes)           |  |  |  |  |  |  |

| Base address register 2 (not used)                         |  |  |  |  |  |  |

| Base address register 3 (not used)                         |  |  |  |  |  |  |

| Base address register 4 (not used)                         |  |  |  |  |  |  |

| Base address register 5 (not used)                         |  |  |  |  |  |  |

| Reserved (not used)                                        |  |  |  |  |  |  |

| Reserved (not used)                                        |  |  |  |  |  |  |

| Base address expansion memory (expansion ROM)              |  |  |  |  |  |  |

| (not used)                                                 |  |  |  |  |  |  |

| Reserved (not used)                                        |  |  |  |  |  |  |

|                                                            |  |  |  |  |  |  |

| rupt line                                                  |  |  |  |  |  |  |

| •                                                          |  |  |  |  |  |  |

|                                                            |  |  |  |  |  |  |

Comments for the table

The **vendor ID**  $1442_{hex}$  is the approved manufacturer identifier for Phoenix Contact.

The device ID of boards with the file designation IBS PCI SC... is  $0002_{hex}$ .

**PHŒNIX** CONTACT

#### Structure and Interfaces of INTERBUS Controller Boards

The revision ID indicates the hardware revision of the controller board.

Class code 0C<sub>hex</sub> indicates a serial bus controller.

The PCI interface uses two base address registers:

Base address register 0 contains the I/O addresses for the host interface register. The length of the I/O address area is 16 bytes.

Base address register 1 is used for the MPM address area of the master and NV-RAM. A 128-kbyte memory address area is provided for the MPM and NV-RAM respectively.

<text><text> The MPM acts as a data interface between the host system and the INTERBUS master (see also Section 2.3, "Multi-Port Memory (MPM)").

## 2.2 Host Interface for INTERBUS Controller Boards

The host interface forms the interface between the host system and the controller board MPM. The host interface also contains several registers.

### 2.2.1 Hardware Settings of Controller Boards

IBS PCI controller boards have DIP switches for setting controller board numbers (board number) and the test mode (ON/OFF). The transmission rate (500 kbaud/2 Mbaud) can also be set for the IBS PCI SC/RI-LK controller board.

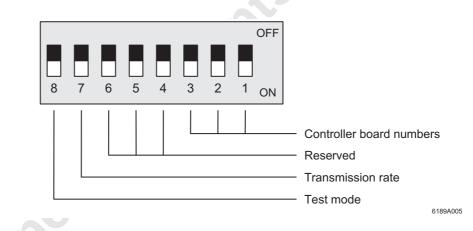

Figure 2-2 DIP switch assignment

As default upon delivery, all DIP switches are in the OFF position. DIP switches 4 to 6 are reserved for later function expansions and should be left in the OFF position.

#### Structure and Interfaces of INTERBUS Controller Boards

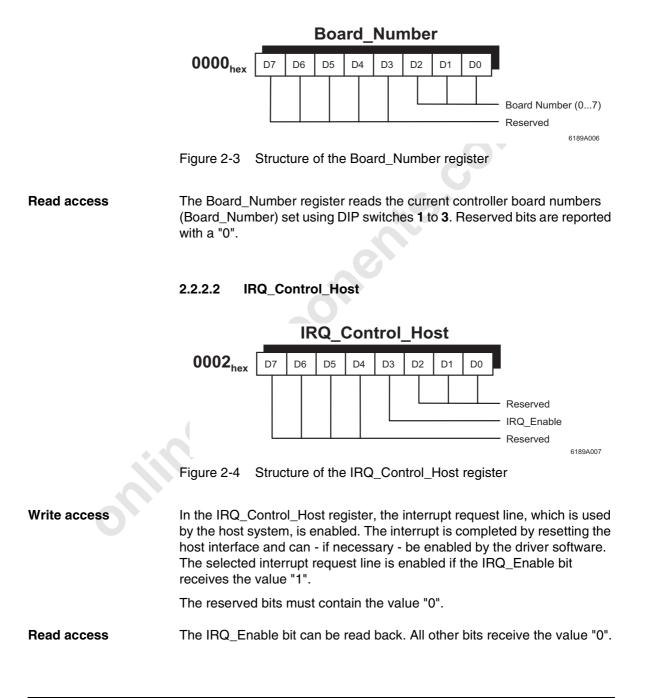

# **Board number** The controller board number (board number) is specified using DIP switches **1** to **3**. Table 2-2 indicates possible settings:

| Board Number | DIP Switch 1 | DIP Switch 1 DIP Switch 2 |     |  |

|--------------|--------------|---------------------------|-----|--|

| 1            | 1 OFF OFF    |                           | OFF |  |

| 2            | OFF          | OFF                       | ON  |  |

| 3            | OFF          | ON                        | OFF |  |

| 4            | OFF          | ON                        | ON  |  |

| 5            | 5 ON OFF     |                           | OFF |  |

| 6            | 6 ON OFF     |                           | ON  |  |

| 7            | ON           | ON                        | OFF |  |

| 8            | 8 ON         |                           | ON  |  |

Table 2-2

Possible settings for controller board numbers

Test mode

If DIP switch **8** is in the ON position, after startup the controller board will automatically switch to test mode and start up any connected bus. In test mode, data exchange is not possible in either direction between the host system and the MPM. No outputs are set.

Test mode may only be used for checking the INTERBUS system connected to the controller board. Test mode should not be used in normal system operation.

#### For the IBS PCI SC/RI-LK only:

Transmission rate

The transmission rate of the INTERBUS system is set, during operation via optical fiber cable, using DIP switch **7**. If the DIP switch is in the OFF position, the transmission rate is 500 kbaud. If the DIP switch is in the ON position, INTERBUS data is transmitted at 2 Mbaud.

This switch has no significance for controller boards IBS PCI SC/I-T and IBS PCI SC/RI/I-T and should remain in the OFF position. The baud rate setting is made automatically.

6189A

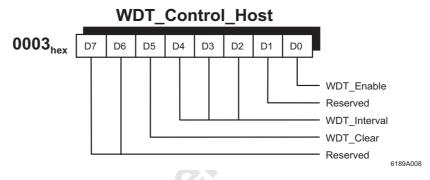

## 2.2.2 I/O Register

The controller board occupies 16 I/O addresses of the host system. The first eight addresses are occupied with control registers, which can be both read and written. After the control registers come the I/O registers for direct inputs and outputs.

Table 2-3 Addresses of the I/O registers

| Offset | Name               | Function                                             |

|--------|--------------------|------------------------------------------------------|

| 0      | Board_Number       | Read current set controller board number             |

| 1      | Not_Used           | Reserved                                             |

| 2      | IRQ_Control_Host   | Interrupt enable                                     |

| 3      | WDT_Control_Host   | Status, enabling, and reset of the watchdog timer    |

| 4      | Reset_Control_Host | Master software reset                                |

| 5      | Not_Used           | Reserved                                             |

| 6      | Not_Used           | Reserved                                             |

| 7      | Status             | Read and write status register                       |

| 8      | Direct_IN          | Read inputs Direct IN 1 to Direct IN 6               |

| 9      | Direct_OUT         | Read and write outputs Direct OUT 1 and Direct OUT 2 |

| 10     | Not_Used           | Reserved                                             |

| 11     | Not_Used           | Reserved                                             |

| 12     | Not_Used           | Reserved                                             |

| 13     | Not_Used           | Reserved                                             |

| 14     | Not_Used           | Reserved                                             |

| 15     | Not_Used           | Reserved                                             |

#### Structure and Interfaces of INTERBUS Controller Boards

#### 2.2.2.1 Board\_Number

**PHŒNIX** CONTACT

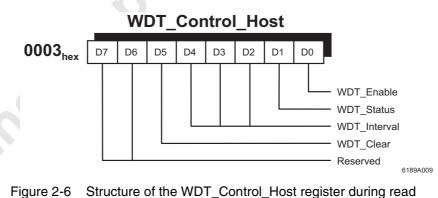

#### 2.2.2.3 WDT\_Control\_Host

Write access

The host interface watchdog timer can be switched on, operated, and reset using the WDT\_Control\_Host register. The reserved bits must contain the value "0".

Figure 2-5 Structure of the WDT\_Control\_Host register during write access

Setting the WDT\_Enable bit activates the watchdog timer. This timer is active and runs until it overflows or is switched off by a hardware reset of the host system. It **cannot** be deactivated by resetting the WDT\_Enable bit. The monitoring time is determined by a bit combination in the "WDT\_interval" (D2 to D4). The contents of this field are saved when the watchdog timer is switched on and can be modified while the timer is active. The watchdog timer is triggered by the read and write access of the WDT\_Control\_Host register. The WDT\_Clear status is not saved, i.e., the watchdog timer cannot be switched off by setting this bit. WDT\_Clear only resets the WDT\_Status bit and the HF LED on the controller board after a watchdog timer has been triggered.

#### Structure and Interfaces of INTERBUS Controller Boards

In the WDT\_Interval (data bits 2 to 4) the following monitoring times can be set:

| Table 2-4 |    | WDT_Interval |                 |  |

|-----------|----|--------------|-----------------|--|

| D4        | D3 | D2           | Monitoring Time |  |

| 0         | 0  | 0            | 8.2 ms          |  |

| 0         | 0  | 1            | 16.4 ms         |  |

| 0         | 1  | 0            | 32.8 ms         |  |

| 0         | 1  | 1            | 65.5 ms         |  |

| 1         | 0  | 0            | 131.1 ms        |  |

| 1         | 0  | 1            | 262.1 ms        |  |

| 1         | 1  | 0            | 524.3 ms        |  |

| 1         | 1  | 1            | 1048.6 ms       |  |

2-6 Structure of the WDT\_Control\_Host register during read access

During a read access, the WDT\_Enable bit indicates whether the watchdog timer is running. This bit cannot be reset by a write access. The WDT\_Status bit indicates the status of the monitoring output. If the bit has the value "0", the watchdog timer has always been triggered appropriately since power up. If the bit has the value "1", the watchdog timer was not reset in the specified time. In this case, the interrupt SRQ2L(0) is

6189A

generated. The HF LED on the controller board indicates a SysFail of the host system. This bit remains set until WDT\_Clear is set or the timer is restarted. The set time interval WDT\_Interval can be read back.

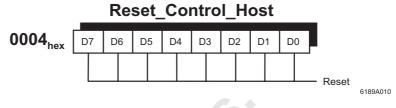

#### 2.2.2.4 Reset\_Control\_Host

Write access

A reset of the controller board master is triggered by writing the reset bit field using the bit pattern in Table 2-5. This means that both the firmware and INTERBUS are reset. After a reset the master starts a selftest with a "power on". The MPM is not immediately reset with a reset. The data remains in the MPM until the master checks the MPM during its test routine. Only then will the data be cleared and the register reset.

|  | Table 2-5 | Bit pattern for the master reset |

|--|-----------|----------------------------------|

|--|-----------|----------------------------------|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  |

#### Structure and Interfaces of INTERBUS Controller Boards

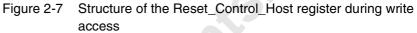

#### **Read access**

Write access

During read access, data bit D0 indicates that the master is currently in the selftest mode and therefore cannot enable the MPM. If the bit is set to "0", the master is again ready to operate.

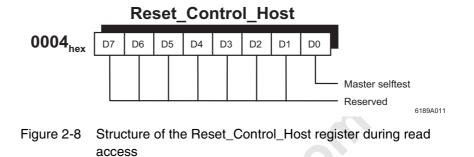

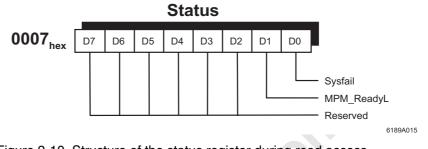

#### 2.2.2.5 Status

Setting the SysFail bit indicates to the MPM and the INTERBUS master that an error has occurred in the host system.

This bit is set after startup. If the bit is set, no output data can be sent to the bus. Therefore this bit must be reset by the driver software.

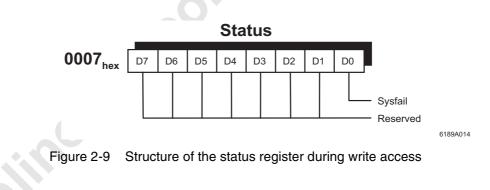

#### **Read access**

Figure 2-10 Structure of the status register during read access

The SysFail bit and MPM\_ReadyL bit can be read back. All other bits are reserved and reported with a "0".

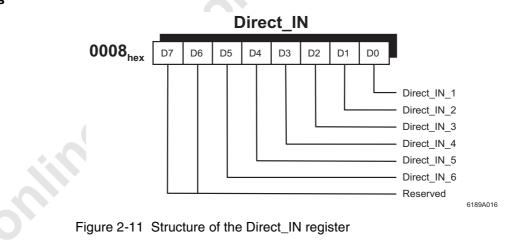

2.2.2.6 Direct\_IN

The status of the direct inputs can be read back using this register.

Read access

#### Structure and Interfaces of INTERBUS Controller Boards

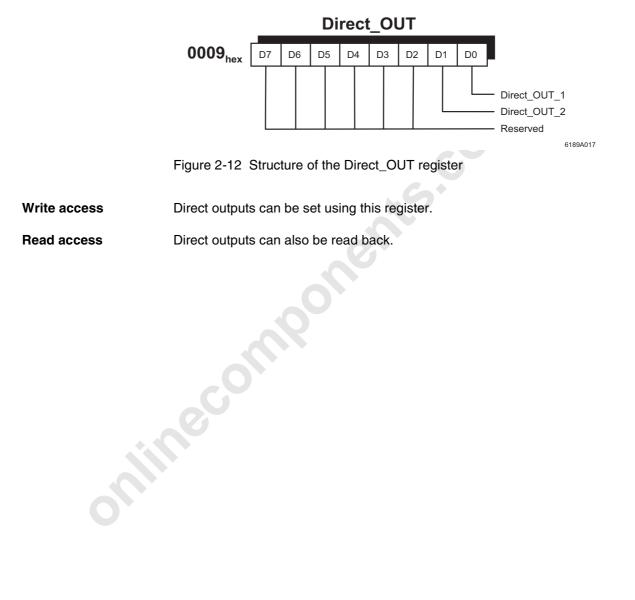

#### 2.2.2.7 Direct\_OUT

6189A

## 2.3 Multi-Port Memory (MPM)

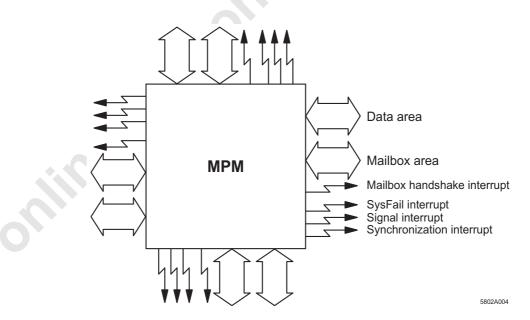

Along with the INTERBUS master and the host interface, the multi-port memory (MPM) is a central component of INTERBUS controller boards. As described above, all information exchanged between the host system and the INTERBUS master is routed through the MPM.

6189A012

Figure 2-13 The MPM as the central interface of the controller board

The MPM control logic ensures prioritized assignment of access to the MPM. Time monitoring is started in parallel with accessing of the MPM. If a device takes too long to access or fails to access, a timeout is generated. This is indicated in an MPM register and access to the MPM is simultaneously re-enabled for other devices.

All data in the MPM is stored in Intel format ("little-endian" or "low-high" format). Appropriate conversion is therefore required on host system access.

|                             | <ul> <li>In addition to the hardware registers, the MPM has a series of software registers, which are used specifically to control mailbox communication between the individual devices. The number and location of these registers are not predetermined by the hardware.</li> <li>From the viewpoint of the user, the MPM therefore consists of the following functional components: <ul> <li>Static RAM (SRAM)</li> <li>Memory manager</li> <li>Status and control register</li> <li>Serial data channel</li> </ul> </li> </ul>                                                                     |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

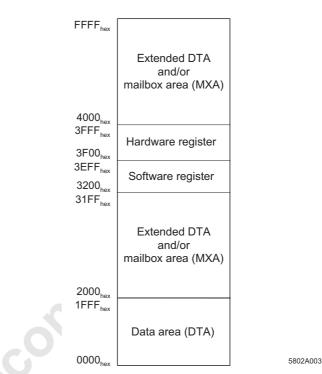

| Static RAM                  | The static RAM (SRAM) uses MPM address area 0000hex through FFFFhex<br>and therefore occupies a special position within the MPM. This area is<br>always available and cannot be blocked by the MPM memory manager.<br>The SRAM contains the data area (DTA) and the mailbox area (MXA), i.e.,<br>all data exchanged between the individual nodes is routed via the SRAM.<br>The segmentation and size of the individual areas is specified by the MPM<br>firmware manager rather than being predetermined by the hardware.                                                                             |

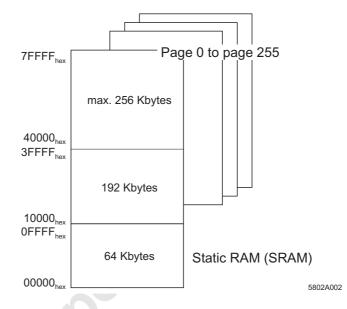

| Memory manager              | The entire MPM address area is a maximum of 512 kbytes. Address area 00000hex through 0FFFhex (64 kbytes) occupies a special position. This area contains the static RAM (SRAM) and the hardware registers. Up to 256 pages of any size can be displayed in the remaining area (10000hex –7FFFhex). It is possible to switch between the individual pages using a special hardware register in the MPM. Each node can display the relevant page independently of the other nodes. Address area 0000hex through FFFFhex (64 kbytes) is not switched with the rest and is thus available for every page. |

| Status and control register | MPM address area 3F90hex through 3FFFhex (i.e., within the SRAM area) contains a series of hardware registers. These registers contain, for example, MPM status information or are used to evaluate and generate signals (interrupts) between the individual nodes. The registers are available to all nodes. Registers that present the same contents to all nodes are distinguished from those that are dedicated to each individual node. However, the same number of registers at the same addresses are always available to all nodes.                                                            |

6189A

# Serial data channel

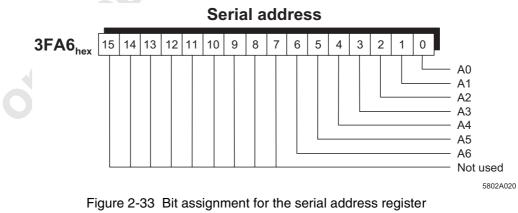

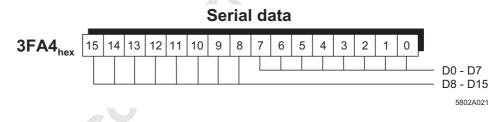

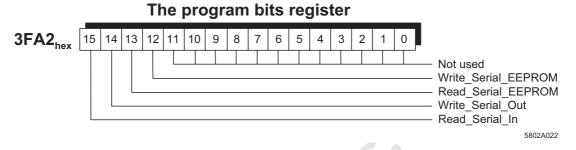

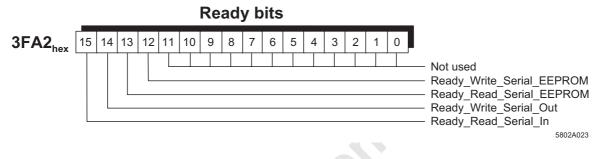

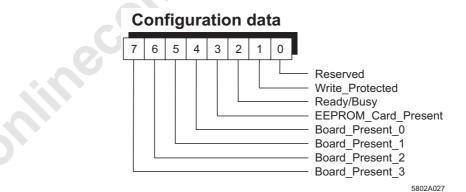

I/O shift registers and a serial EEPROM can be connected to the MPM serial data channel. The serial data channel is used to read and save or , etc. , output configuration data. A distinction is made between access to the serial EEPROM and access to the shift registers. For example, the switches, the motherboard ID, and the MPM configuration are read via the shift registers. The serial data channel is accessed using four hardware

# 2.3.1 MPM Address Area

Figure 2-14 MPM address area

The diagnostic registers, for example, have the following addresses:

| Register                           | Address             |

|------------------------------------|---------------------|

| Diagnostic status register         | 3520 <sub>hex</sub> |

| Diagnostic parameter register      | 3522 <sub>hex</sub> |

| Ext. diagnostic parameter register | 37E6 <sub>hex</sub> |

| Slave diagnostic status register   | 37EC <sub>hex</sub> |

| E  |  |

|----|--|

| Ш  |  |

| Ш  |  |

| Ш  |  |

| Ш  |  |

| 24 |  |

For additional information on the diagnostic registers, please refer to the *Firmware Services and Error Messages* User Manual *IBS SYS FW G4 UM E, Order No. 27 45 18 5*.

# 2.3.2 Segmentation of the SRAM in the MPM

The SRAM is located from address  $\rm 0000_{hex}$  through address  $\rm FFFF_{hex}$  in the MPM.

Figure 2-15 Segmentation of the SRAM

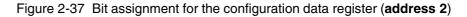

This document provides a general description of the MPM, i.e., the registers and MPM functions of a complete MPM with **four** nodes are described.

The IBS PCI controller board MPM is only designed for two nodes:

| Node 0: | Host CPU (application program) |

|---------|--------------------------------|

| Node 1: | INTERBUS master (firmware)     |

All MPM registers and bits are only available to nodes 0 and 1. Accessing the registers for nodes 2 and 3 has no effect.

# 2.3.3 MPM Communication Options

The MPM is used to exchange information between devices (nodes). This communication can be related to the exchange of data or notification of an event. Both options are offered by the MPM and are supported by corresponding mechanisms. The MPM SRAM is available for exchanging data. For exchanging events, there are four sources of interrupts for each node, which can be evaluated independently of each other. It is also possible for both forms to be used in combination, as, for example, in the mailbox interface.

#### **Communication Methods Used:**

- Data interface

- Mailbox interface

- SysFail requests

- Signal interface

- Synchronization requests

Figure 2-16 Diagram of the various MPM communication options

#### 2.3.3.1 Data Interface (DTI)

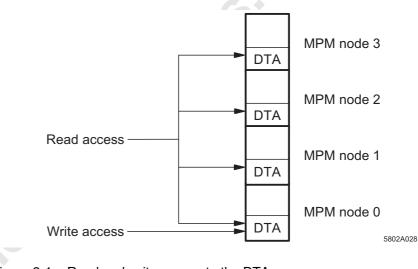

Process data is exchanged with the INTERBUS master via the data interface.

Various areas are defined within the data area (DTA). The data interface (DTI) consists of both the "normal" data area, which contains process data and the extended data area, in which user-specific data can be stored.

No handshake is specified for exchanging data via the DTI. This means that in contrast to message exchange via the mailbox interface, data may be overwritten by one node while it is being read by another. The user must use their own transmission protocol. For IBS PCI controller boards, a protocol of this type is activated by default by the firmware, and is supported by the driver.

A detailed description of the data interface can be found in Section 3, "Data Exchange via the Data Area".

#### 2.3.3.2 Mailbox Interface (MXI)

The mailbox interface (MXI) is a protocol-oriented interface via which messages can be exchanged between the nodes.

The mailbox interface consists of the mailbox area (MXA) and a number of hardware and software registers for each node. The area occupied by the mailbox area and the register addresses is predefined and must not be changed by the user. The size and location of the mailbox area and the software registers are specified in the MPM descriptor, which is created by the MPM master for each node (see Section "Structure of the MPM Descriptor" on page 2-49).

The mailbox area in turn is divided into a number of blocks ("mailboxes"). Each of these can take one message. When sending, the address of the mailbox containing the message is placed in a software register in the MPM and the receiving node is notified (see also Section 4, "Communication via the Mailbox Interface"). The mailbox is managed by the node driver. The length of one mailbox is 1 kbyte.

MPM registers used:

- Set HS Ax/Bx register

- Status register 1

- Handshake register A / handshake register B

- Send vector and acknowledge vector registers (software registers)

A detailed description of the mailbox interface and the handshake protocol used can be found in Section 4, "Communication via the Mailbox Interface".

#### 2.3.3.3 SysFail Request

The SysFail logic can be used to immediately notify other nodes of serious system errors. The SysFail signal can be triggered either by hardware, via the corresponding MPM control lines or by software, by writing to a special MPM register. An interrupt is always generated at all nodes (apart from the initiating one) and indicated in an MPM register (status register 1). In the case of a SysFail initiated by the hardware, the logical status of the initiating line is indicated in a different MPM register (status SysFail register). The response to a SysFail interrupt depends on the particular node. In the event of a SysFail interrupt, the INTERBUS master, for example, sets all output data to zero. A node must acknowledge that it has detected a SysFail interrupt by writing to an MPM register (clear status bit register). This resets the corresponding bit in status register 1.

MPM registers used:

- Status register 1

- Status SysFail register

- Clear-status-bit register

- Set SysFail request register

# 2.3.4 MPM Hardware Register

MPM hardware registers are displayed in the MPM SRAM address area in  $3F90_{hex}$  through  $3FFF_{hex}$ . A distinction is made between read and write hardware registers.

**Write registers** The write registers are word registers that can initiate or pass on information or actions. The contents of the write registers can only be read back in summarized form in the read registers.

**Read registers** The read registers are word registers. They can be used to read both the written data in the write registers and additional status and configuration data.

|                     | -                        | -    |                     |            |      |

|---------------------|--------------------------|------|---------------------|------------|------|

| Address             | Register                 | Page | Address             | Register   | Page |

| 3F90 <sub>hex</sub> | Set MPM node par ready 0 | 2-31 | 3FCA <sub>hex</sub> | Set HS A15 | 2-37 |

| 3F92 <sub>hex</sub> | Set MPM node par ready 1 | 2-31 | 3FCC <sub>hex</sub> | Set HS B7  | 2-37 |

| 3F94 <sub>hex</sub> | Set MPM node par ready 2 | 2-31 | 3FCE <sub>hex</sub> | Set HS B15 | 2-37 |

| 3F96 <sub>hex</sub> | Set MPM node par ready 3 | 2-31 | 3FD0 <sub>hex</sub> | Set HS A2  | 2-37 |

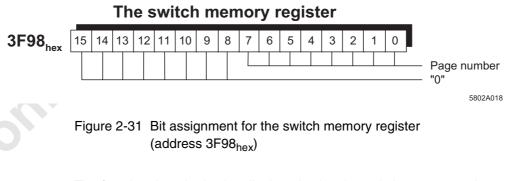

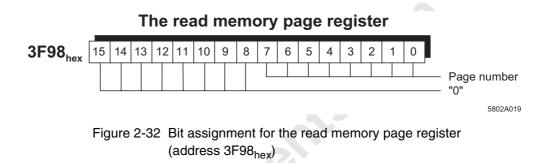

| 3F98 <sub>hex</sub> | Switch memory            | 2-42 | 3FD2 <sub>hex</sub> | Set HS A10 | 2-37 |

| 3F9C <sub>hex</sub> | Set sync req             | 2-41 | 3FD4 <sub>hex</sub> | Set HS B2  | 2-37 |

| 3FA0 <sub>hex</sub> | Set SysFail req          | 2-33 | 3FD6 <sub>hex</sub> | Set HS B10 | 2-37 |

| 3FA2 <sub>hex</sub> | Program bits             | 2-45 | 3FD8 <sub>hex</sub> | Set HS A6  | 2-37 |

| 3FA4 <sub>hex</sub> | Serial data              | 2-44 | 3FDA <sub>hex</sub> | Set HS A14 | 2-37 |

| 3FA6 <sub>hex</sub> | Serial address           | 2-43 | 3FDC <sub>hex</sub> | Set HS B6  | 2-37 |

| 3FA8 <sub>hex</sub> | Clear status bit 0       | 2-34 | 3FDE <sub>hex</sub> | Set HS B14 | 2-37 |

| 3FAA <sub>hex</sub> | Clear status bit 1       | 2-34 | 3FE0 <sub>hex</sub> | Set HS A1  | 2-37 |

| 3FAC <sub>hex</sub> | Clear status bit 2       | 2-34 | 3FE2 <sub>hex</sub> | Set HS A9  | 2-37 |

| 3FAE <sub>hex</sub> | Clear status bit 3       | 2-34 | 3FE4 <sub>hex</sub> | Set HS B1  | 2-37 |

| 3FB0 <sub>hex</sub> | Set MPM node SG int 0    | 2-38 | 3FE6 <sub>hex</sub> | Set HS B9  | 2-37 |

Table 2-6 Write register addresses in the MPM

| Structure and Interfaces of INTERBUS Controller Be | oards |

|----------------------------------------------------|-------|

|----------------------------------------------------|-------|

| Address             | Register              | Page | Address             | Register   | Page |

|---------------------|-----------------------|------|---------------------|------------|------|

| 3FB2 <sub>hex</sub> | Set MPM node SG int 1 | 2-38 | 3FE8 <sub>hex</sub> | Set HS A5  | 2-37 |

| 3FB4 <sub>hex</sub> | Set MPM node SG int 2 | 2-38 | 3FEA <sub>hex</sub> | Set HS A13 | 2-37 |

| 3FB6 <sub>hex</sub> | Set MPM node SG int 3 | 2-38 | 3FEC <sub>hex</sub> | Set HS B5  | 2-37 |

| 3FB8 <sub>hex</sub> | Set MPM node ready0   | 2-30 | 3FEE <sub>hex</sub> | Set HS B13 | 2-37 |

| 3FBA <sub>hex</sub> | Set MPM node ready1   | 2-30 | 3FF0 <sub>hex</sub> | Set HS A0  | 2-37 |

| 3FBC <sub>hex</sub> | Set MPM node ready2   | 2-30 | 3FF2 <sub>hex</sub> | Set HS A8  | 2-37 |

| 3FBE <sub>hex</sub> | Set MPM node ready3   | 2-30 | 3FF4 <sub>hex</sub> | Set HS B0  | 2-37 |

| 3FC0 <sub>hex</sub> | Set HS A3             | 2-37 | 3FF6 <sub>hex</sub> | Set HS B8  | 2-37 |

| 3FC2 <sub>hex</sub> | Set HS A11            | 2-37 | 3FF8 <sub>hex</sub> | Set HS A4  | 2-37 |

| 3FC4 <sub>hex</sub> | Set HS B3             | 2-37 | 3FFA <sub>hex</sub> | Set HS A12 | 2-37 |

| 3FC6 <sub>hex</sub> | Set HS B11            | 2-37 | 3FFC <sub>hex</sub> | Set HS B4  | 2-37 |

| 3FC8 <sub>hex</sub> | Set HS A7             | 2-37 | 3FFE <sub>hex</sub> | Set HS B12 | 2-37 |

Table 2-6 Write register addresses in the MPM

Table 2-7

Read register addresses in the MPM

| Address             | Register          | Page | Address             | Register             | Page |

|---------------------|-------------------|------|---------------------|----------------------|------|

| 3F90 <sub>hex</sub> | MPM configuration | 2-26 | 3FB2 <sub>hex</sub> | Status SysFail       | 2-32 |

| 3F98 <sub>hex</sub> | Read memory page  | 2-43 | 3FB4 <sub>hex</sub> | Status node SG inf   | 2-40 |

| 3FA2 <sub>hex</sub> | RDY bits          | 2-46 | 3FB6 <sub>hex</sub> | Status register 2    | 2-29 |

| 3FA4 <sub>hex</sub> | Serial data       | 2-44 | 3FC0 <sub>hex</sub> | Handshake register A | 2-35 |

| 3FB0 <sub>hex</sub> | Status register 1 | 2-27 | 3FC2 <sub>hex</sub> | Handshake register B | 2-35 |

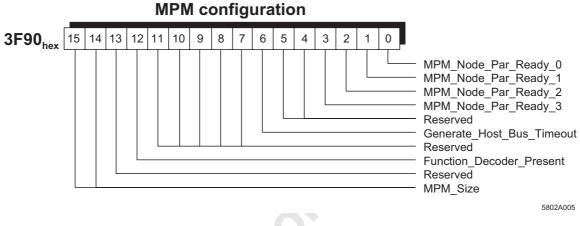

## 2.3.4.1 MPM Configuration Register

The MPM configuration register enables the nodes to read the board configuration. The register contains information about the size of the MPM and the status of the nodes.

Figure 2-17 Bit assignment for the MPM configuration register (address 3F90<sub>hex</sub>)

MPM\_Size

Bits 14 and 15 in the MPM configuration register indicate the size of the SRAM available for the MPM:

Table 2-8Setting the MPM size

| Address Area | Bit 14 | Bit 15 |

|--------------|--------|--------|

| 16 kbytes    | 0      | 0      |

| 64 kbytes    | 0      | 1      |

| 256 kbytes   | 1      | 0      |

| 512 kbytes   | 1      | 1      |

MPM\_Node\_Par\_-Ready\_x The *MPM\_Node\_Ready\_x* bit indicates that the node has successfully completed its selftest (bit = 1: selftest successful). These bits are set by the nodes by writing the value  $8000_{hex}$  to the set MPM node ready x register and reset with the value  $0000_{hex}$ .

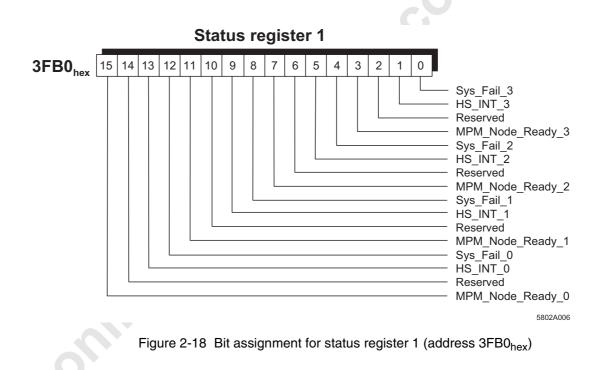

#### 2.3.4.2 Status Register 1

Status register 1 contains information about the status of the individual nodes. It contains four bits for each node:

| Node 0: | Bit 12 - bit 15 |

|---------|-----------------|

| Node 1: | Bit 8 - bit 11  |

| Node 2: | Bit 4 - bit 7   |

| Node 3: | Bit 0 - bit 3   |

MPM\_Node\_Ready\_x The MPM\_Node\_Ready\_x bit indicates that the node has successfully

completed its selftest (bit = 1: selftest successful). These bits are set by the

nodes by writing the value 8000<sub>hex</sub> to the set MPM node ready x register

and reset with the value 0000<sub>hex</sub>.

6189A

**DPHŒNIX** CONTACT

HS\_Int\_x Setting the HS\_Int\_x bit in status register 1 indicates to the node that there is a message ready for it in the MPM (see Section 4, "Communication via the Mailbox Interface"). The bit can be used in polling mode or in an interrupt routine to locate the cause of the interrupt more precisely and is a summary of the handshake bits for the node.

Sys\_Fail\_x The Sys\_Fail\_x bit is used to indicate a serious malfunction of a node. The Sys\_Fail\_x bit is set by the hardware or the set SysFail register and has to . system er. . ot indicate the s be reset by the nodes by writing the value 0000<sub>hex</sub> to the clear status SysFail x registers. The status SysFail register can be used to determine

The Sys\_Fail\_x bits do not indicate the status of the line that has initiated

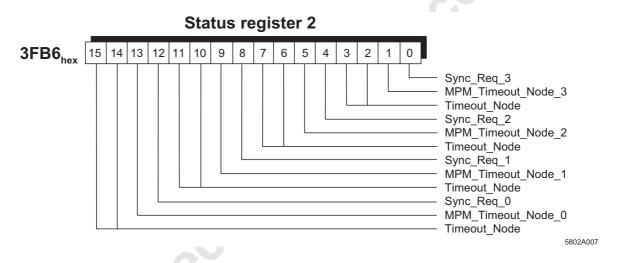

#### 2.3.4.3 Status Register 2

Status register 2 contains additional information about the status of the individual nodes. For each node, four bits are provided in the register:

| Node 0: | Bit 12 - bit 15 |

|---------|-----------------|

| Node 1: | Bit 8 - bit 11  |

| Node 2: | Bit 4 - bit 7   |

| Node 3: | Bit 0 - bit 3   |

Figure 2-19 Bit assignment for status register 2 (address 3FB6hex)

Sync\_Req\_x

Setting the  $Sync\_Req\_x$  bit (bit = 1) in status register 2 indicates that the sync interrupt has been generated for the associated node. It is not possible to determine which node has caused the sync interrupt. The sync\\_req bit is reset by writing set bit 14 to the clear status bit register. Each node can only clear its own bit, i.e., node 1, for example, can only reset the  $Sync\_Req\_1$  bit.

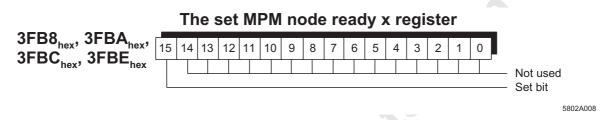

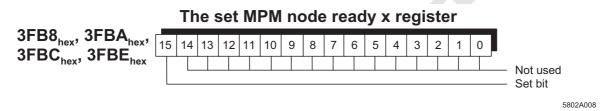

### 2.3.4.4 The Set MPM Node Ready x Register

Writing the value  $8000_{hex}$  (most significant bit = 1) to a Set MPM node ready x register sets the corresponding *MPM\_Node\_Ready\_x* bit in MPM status register 1. The bit is reset by writing the value  $0000_{hex}$  (most significant bit = 0) to the register. By setting the bit, the node signals that it is ready to operate. Each node has its own set MPM node ready x register.

Figure 2-20 Bit assignment for the set MPM node ready x register

| Address             | Register             |

|---------------------|----------------------|

| 3FB8 <sub>hex</sub> | Set MPM node ready 0 |

| 3FBA <sub>hex</sub> | Set MPM node ready1  |

| 3FBC <sub>hex</sub> | Set MPM node ready2  |

| 3FBE <sub>hex</sub> | Set MPM node ready3  |

|                     |                      |

#### Table 2-9The set MPM node ready x register addresses

#### 2.3.4.5 The Set MPM Node Par Ready x Register

After successful parameterization, a node sets the corresponding *MPM\_Node\_Par\_Ready\_x* bit in the MPM configuration register. This is achieved by writing a value with a set most significant bit, e.g., the value 8000<sub>hex</sub>, to the set MPM node par ready x register. Writing a reset bit 15 (bit = 0) to the register also resets the corresponding *MPM\_Node\_Par\_Ready\_x* bit in the MPM configuration register. Each node has its own register, which corresponds to the node number (for example, node 1 uses the set MPM node par ready 1 register).

#### Figure 2-21 Bit assignment for the set MPM node par ready x register

| Address             | Register                 |

|---------------------|--------------------------|

| 3F90 <sub>hex</sub> | Set MPM node par ready 0 |

| 3F92 <sub>hex</sub> | Set MPM node par ready 1 |

| 3F94 <sub>hex</sub> | Set MPM node par ready 2 |

| 3F96 <sub>hex</sub> | Set MPM node par ready 3 |

|                     |                          |

Table 2-10 The set MPM node par ready x register addresses

**PHŒNIX** CONTACT

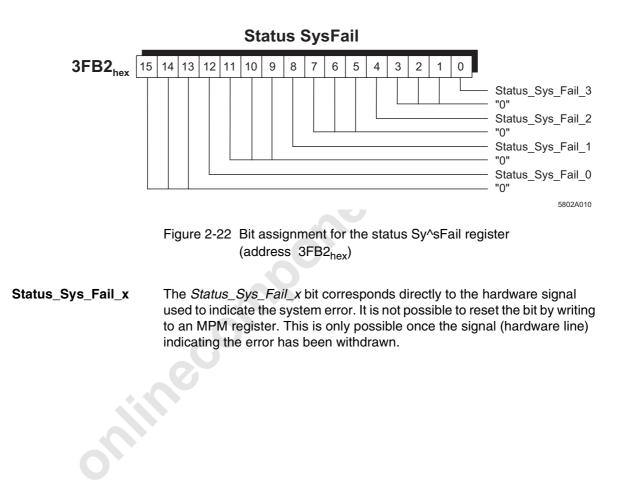

### 2.3.4.6 Status SysFail Register

The status SysFail register can be used to determine which node has signaled a system error (bit = 1: node system error). The bits in the register correspond to the status of the corresponding SysFail line.

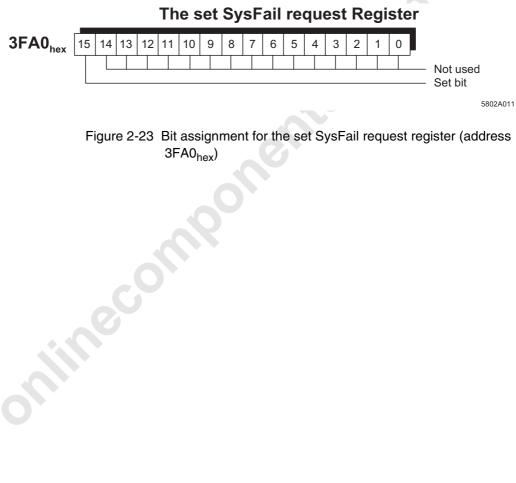

#### 2.3.4.7 The Set SysFail Request Register

The SysFail signal can be generated in two different ways: a hardware signal to the MPM control logic or the software writing to the set SysFail request register. As with other registers, writing with bit 15 (the most significant bit) set initiates the signal. This generates a SysFail interrupt on all other nodes.

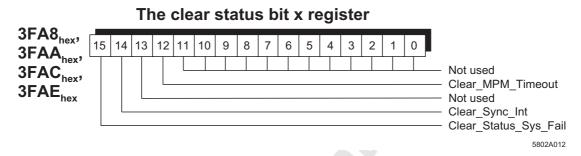

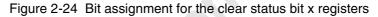

#### 2.3.4.8 The Clear Status Bit x Registers

The clear status bit x registers are used to reset certain signals sent between the nodes. Each node has its own clear status bit x register, i.e., for a complete MPM there are four clear status bit x registers.

| Address             | Register           |  |

|---------------------|--------------------|--|

| 3FA8 <sub>hex</sub> | Clear status bit 0 |  |

| 3FAA <sub>hex</sub> | Clear status bit 1 |  |

| 3FAC <sub>hex</sub> | Clear status bit 2 |  |

Clear status bit 3

Table 2-11 Clear status bit x register addresses

As can be seen in Figure 2-24, the following signals can be reset using the clear status bit x register:

MPM timeout

3FAE<sub>hex</sub>

- Sync signal

- Status SysFail signal

For each signal to be reset, enter a "1" in the corresponding bit position. This enables the signals to be reset individually or simultaneously.

#### 2.3.4.9 Handshake Register A and Handshake Register B

32 handshake bits are defined for exchanging acknowledged messages between the nodes. The handshake bits are used by the mailbox handshake protocol for sending, receiving, and acknowledging messages between the nodes.

By evaluating handshake registers A and B, a node can determine which other node has caused which handshake interrupt (see also Section 4, "Communication via the Mailbox Interface").

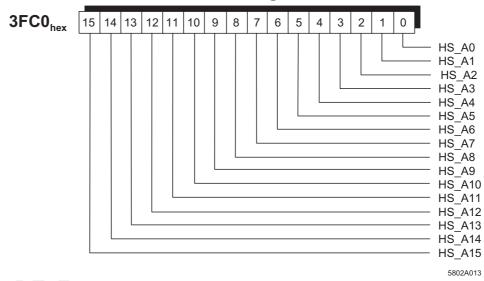

Handshake register A

Figure 2-25 Bit assignment for handshake register A (address 3FC0<sub>hex</sub>)

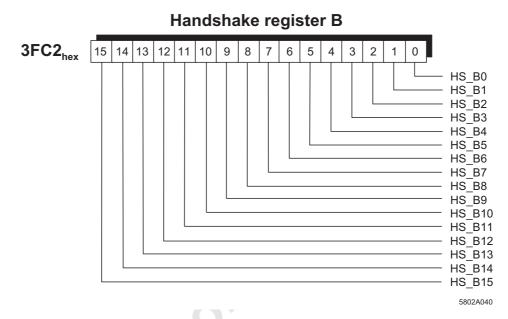

Figure 2-26 Bit assignment for handshake register B (address 3FC2<sub>hex</sub>)

minecon

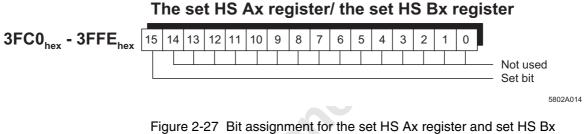

### 2.3.4.10 The Set HS Ax Register and the Set HS Bx Register

These 32 registers are used for implementing the mailbox handshake protocol. The assignment and meaning of the registers are described in detail in the mailbox handshake protocol. Writing set bit 15 (bit = 1) to a set HS Ax/Bx register activates an interrupt at the corresponding node, the  $HS\_INT\_x$  bit in status register 1 changes to "1", and the associated bit is set in one of the two handshake registers. Writing reset bit 15 (bit = 0) to a set HS Ax/Bx register resets the associated bit in the handshake register and terminates the interrupt request.

Figure 2-27 Bit assignment for the set HS Ax register and set HS register

| Table 2-12 | The set HS Ax registe | r and the set HS | Bx register | addresses |

|------------|-----------------------|------------------|-------------|-----------|

|            |                       |                  |             |           |

| Address             | Register   | Address             | Register   | Address             | Register   | Address             | Register   |

|---------------------|------------|---------------------|------------|---------------------|------------|---------------------|------------|

| 3FC0 <sub>hex</sub> | Set HS A3  | 3FD0 <sub>hex</sub> | Set HS A2  | 3FE0 <sub>hex</sub> | Set HS A1  | 3FF0 <sub>hex</sub> | Set HS A0  |

| 3FC2 <sub>hex</sub> | Set HS A11 | 3FD2 <sub>hex</sub> | Set HS A10 | 3FE2 <sub>hex</sub> | Set HS A9  | 3FF2 <sub>hex</sub> | Set HS A8  |

| 3FC4 <sub>hex</sub> | Set HS B3  | 3FD4 <sub>hex</sub> | Set HS B2  | 3FE4 <sub>hex</sub> | Set HS B1  | 3FF4 <sub>hex</sub> | Set HS B0  |

| 3FC6 <sub>hex</sub> | Set HS B11 | 3FD6 <sub>hex</sub> | Set HS B10 | 3FE6 <sub>hex</sub> | Set HS B9  | 3FF6 <sub>hex</sub> | Set HS B8  |

| 3FC8 <sub>hex</sub> | Set HS A7  | 3FD8 <sub>hex</sub> | Set HS A6  | 3FE8 <sub>hex</sub> | Set HS A5  | 3FF8 <sub>hex</sub> | Set HS A4  |

| 3FCA <sub>hex</sub> | Set HS A15 | 3FDA <sub>hex</sub> | Set HS A14 | 3FEA <sub>hex</sub> | Set HS A13 | 3FFA <sub>hex</sub> | Set HS A12 |

| 3FCC <sub>hex</sub> | Set HS B7  | 3FDC <sub>hex</sub> | Set HS B6  | 3FEC <sub>hex</sub> | Set HS B5  | 3FFC <sub>hex</sub> | Set HS B4  |

| 3FCE <sub>hex</sub> | Set HS B15 | 3FDE <sub>hex</sub> | Set HS B14 | 3FEE <sub>hex</sub> | Set HS B13 | 3FFE <sub>hex</sub> | Set HS B12 |

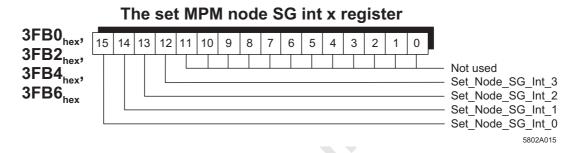

# 2.3.4.11 The Set MPM Node SG Int x Register

The set MPM node SG int x registers can be used to send a signal (interrupt) to any other nodes. The meaning of this signal is left entirely to the user. Each node has its own register, which corresponds to the node number (for example, node 1 uses the set MPM node par ready 1 register).

Figure 2-28 Bit assignment for the set MPM node SG int x register

| Address             | Register              |  |

|---------------------|-----------------------|--|

| 3FB0 <sub>hex</sub> | Set MPM node SG int 0 |  |

| 3FB2 <sub>hex</sub> | Set MPM node SG int 1 |  |

| 3FB4 <sub>hex</sub> | Set MPM node SG int 2 |  |

| 3FB6 <sub>hex</sub> | Set MPM node SG int 3 |  |

Table 2-13The set MPM node SG int x register addresses

The nodes to which a signal is to be sent are selected by the bit pattern written to the register. A set bit (bit = 1) activates an interrupt at the corresponding node and sets the associated bit in the status node SG inf register (see also Section 2.3.4.12, "Status Node SG Inf Register"). A signal can be sent to one or more nodes simultaneously.

The bits in the status node SG int x register are reset and the interrupt request cleared by writing a reset bit (bit = 0) to the bit position of the required node.

| Bit        | Function Executed       |  |

|------------|-------------------------|--|

| Bit 15 = 1 | Signal to node 0        |  |

| Bit 14 = 1 | Signal to node 1        |  |

| Bit 13 = 1 | Signal to node 2        |  |

| Bit 12 = 1 | Signal to node 3        |  |

| Bit 15 = 0 | Delete signal to node 0 |  |

| Bit 14 = 0 | Delete signal to node 1 |  |

| Bit 13 = 0 | Delete signal to node 2 |  |

| Bit 12 = 0 | Delete signal to node 3 |  |

Table 2-14 Assignment of register bits to nodes

A node cannot send a signal to itself.

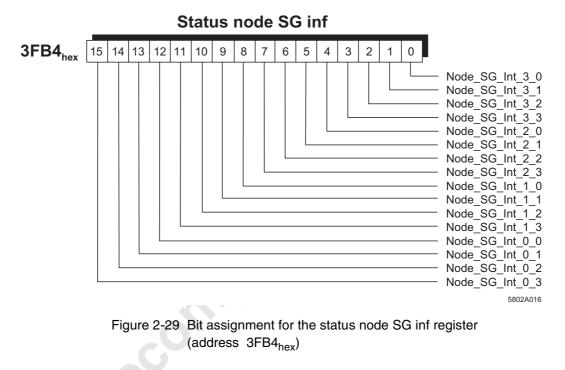

# 2.3.4.12 Status Node SG Inf Register

The status node SG inf register (status node signal interface register), can be used to determine from the bit(s) set which node has sent the MPM node SG int signal to which other node(s).

B

In Figure 2-29 the data bits are "Node SG int x y", where "y" designates the originator and "x" the receiver of the MPM node SG int signal.

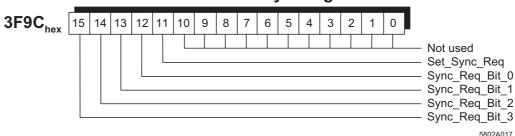

#### 2.3.4.13 The Set Sync Register

The set sync register can be used to send a further signal (interrupt) to any other nodes. The meaning of this signal is left entirely to the user. One possible application, as implied by the name, is synchronization during data exchange between the nodes. (In firmware version 4.x this signal is already used for synchronous mode.) In addition to activating an interrupt, the corresponding *Sync\_Req\_x* bits in status register 2 are set. The *Sync\_Req\_x* bits in status register 2 are reset using the clear status bit x registers.

There is only one register of this type in the MPM. The nodes are, therefore, always accessed through the same register.

The set sync register

Figure 2-30 Bit assignment for the set sync register (address 3F9C<sub>hex</sub>)

#### Set\_Sync\_Req

Setting this bit to "1" causes the sync signal (interrupt) to be sent to the nodes according to the sync req bit mask set. The *Set\_Sync\_Req* bit can be set at the same time as the selection bit pattern, i.e., one write access to the register is sufficient. When the signal is initiated the *Set\_Sync\_Req* bit is automatically withdrawn, whereas the selection mask (bit 15 - bit 12) remains unchanged.

**Sync\_Req\_Bit\_x** The nodes to which a signal is to be sent are selected by the bit pattern in the four most significant bits of the register. A set bit (bit = 1) activates a sync interrupt at the corresponding node and sets the associated bit in status register 2 (see also Section 2.3.4.3). A signal can be sent to one or more nodes simultaneously.

| Bit        | Function Executed |

|------------|-------------------|

| Bit 12 = 1 | Signal to node 0  |

| Bit 13 = 1 | Signal to node 1  |

| Bit 14 = 1 | Signal to node 2  |

| Bit 15 = 1 | Signal to node 3  |

| Table 2-15 | Assignment of the sync req bits to the nodes |

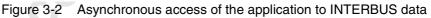

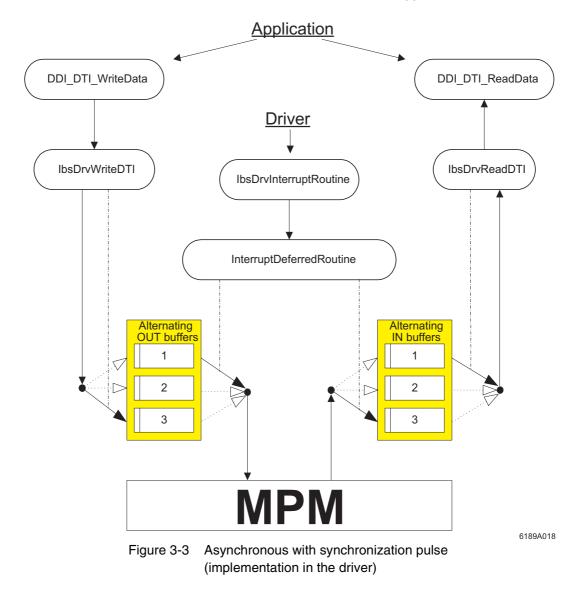

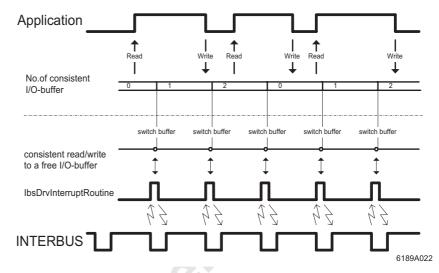

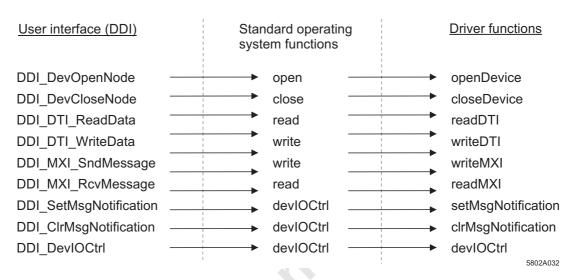

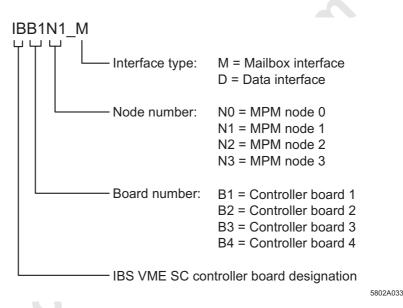

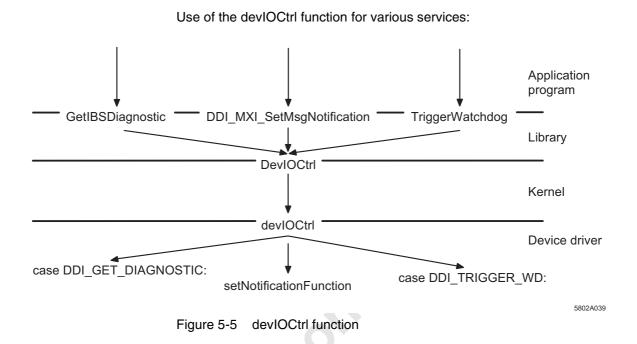

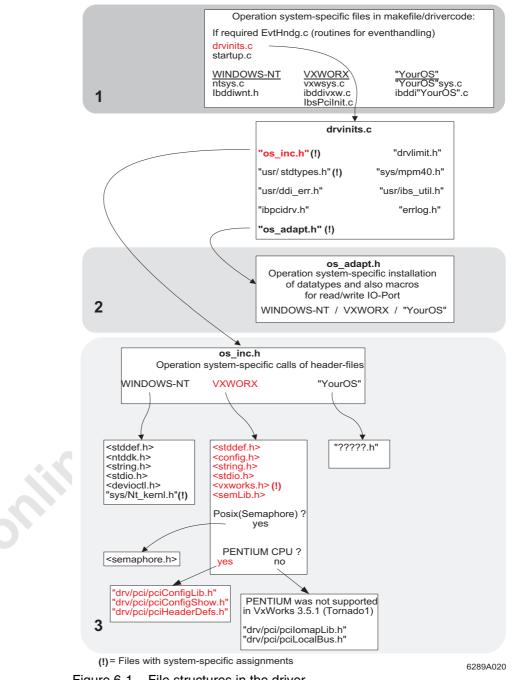

|------------|----------------------------------------------|