NPMC-860-4S0 CPU PMC Module Technical Reference Manual V1.6 HW Revision 2.0

The NPMC-860-4S0 has been designed by:

N.A.T. GmbH Kamillenweg 22 D-53757 Sankt Augustin

Phone: ++49/2241/3989-0 Fax: ++49/2241/3989-10

E-Mail: support@nateurope.com Internet: http://www.nateurope.com

### Disclaimer

The following documentation, compiled by N.A.T. GmbH (henceforth called N.A.T.), represents the current status of the product's development. The documentation is updated on a regular basis. Any changes which might ensue, including those necessitated by updated specifications, are considered in the latest version of this documentation. N.A.T. is under no obligation to notify any person, organization, or institution of such changes or to make these changes public in any other way.

We must caution you, that this publication could include technical inaccuracies or typographical errors.

N.A.T. offers no warranty, either expressed or implied, for the contents of this documentation or for the product described therein, including but not limited to the warranties of merchantability or the fitness of the product for any specific purpose.

In no event will N.A.T. be liable for any loss of data or for errors in data utilization or processing resulting from the use of this product or the documentation. In particular, N.A.T. will not be responsible for any direct or indirect damages (including lost profits, lost savings, delays or interruptions in the flow of business activities, including but not limited to, special, incidental, consequential, or other similar damages) arising out of the use of or inability to use this product or the associated documentation, even if N.A.T. or any authorized N.A.T. representative has been advised of the possibility of such damages.

The use of registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations (patent laws, trade mark laws, etc.) and therefore free for general use. In no case does N.A.T. guarantee that the information given in this documentation is free of such third-party rights.

Neither this documentation nor any part thereof may be copied, translated, or reduced to any electronic medium or machine form without the prior written consent from N.A.T. GmbH.

This product (and the associated documentation) is governed by the N.A.T. General Conditions and Terms of Delivery and Payment.

## Note:

The release of the Hardware Manual is related to a certain HW board revision given in the document title. For HW revisions earlier than the one given in the document title please contact N.A.T. for the corresponding older Hardware Manual release.

# **Table of Contents**

| LI              | LIST OF TABLES                                                                                                                |     |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------|-----|--|

| LIST OF FIGURES |                                                                                                                               |     |  |

| CO              | CONVENTIONS                                                                                                                   |     |  |

| 1               | INTRODUCTION                                                                                                                  | 7   |  |

| 2               | INSTALLATION                                                                                                                  | .10 |  |

|                 | <ul> <li>2.1 SAFETY NOTE</li></ul>                                                                                            |     |  |

|                 | 2.2 INSTALLATION PREREQUISITES AND REQUIREMENTS                                                                               |     |  |

|                 | 2.2.1 Requirements                                                                                                            |     |  |

|                 | 2.2.3 Location Overview                                                                                                       |     |  |

|                 | 2.3 AUTOMATIC POWER UP                                                                                                        |     |  |

|                 | 2.4 STATEMENT ON ENVIRONMENTAL PROTECTION                                                                                     | .13 |  |

|                 | 2.4.1 Compliance to RoHS Directive                                                                                            |     |  |

|                 | 2.4.2 <i>Compliance to WEEE Directive</i>                                                                                     | .14 |  |

| 3               | HARDWARE DETAILS                                                                                                              | .15 |  |

|                 | 3.1 Memory Map                                                                                                                | 15  |  |

|                 | 3.2 POWERQUICC PORT PINS USAGE                                                                                                |     |  |

|                 | 3.3 INTERRUPT STRUCTURE                                                                                                       |     |  |

|                 | 3.4 CONTROL / STATUS REGISTERS                                                                                                |     |  |

|                 | 3.4.1 Status Register 1                                                                                                       | .19 |  |

|                 | 3.4.2 Control/Status Register 2                                                                                               | .19 |  |

|                 | 3.4.3 Status Register 3                                                                                                       |     |  |

|                 | 3.5 IDL BUS OPERATION                                                                                                         |     |  |

|                 | 3.6 TIME DIVISION MULTIPLEX BUS STRUCTURE                                                                                     |     |  |

|                 | 3.7 S/T PORT SETUP                                                                                                            | .22 |  |

| 4               | CONNECTORS                                                                                                                    | .23 |  |

|                 | 4.1 CONNECTOR OVERVIEW                                                                                                        | .23 |  |

|                 | 4.2 Switch Settings                                                                                                           | .23 |  |

|                 | 4.3 PMC CONNECTOR P11                                                                                                         | .24 |  |

|                 | 4.4 PMC CONNECTOR P12                                                                                                         |     |  |

|                 | 4.5 PIN ASSIGNMENT OF THE PMC CONNECTOR P14 (PMC I/O)                                                                         |     |  |

|                 | 4.5.1 Description P14 Signals                                                                                                 |     |  |

|                 | 4.5.2 SCbus IDs                                                                                                               |     |  |

|                 | <ul> <li>4.6 The Front Panel Connectors (S1 - S4)</li> <li>4.7 Connector JP1: Motorola Background Debug Mode (BDM)</li> </ul> |     |  |

|                 | 4.7 CONNECTOR JP1: MOTOROLA BACKGROUND DEBUG MODE (BDM)<br>4.8 CONNECTOR JP2: LATTICE PROGRAMMING PORT                        |     |  |

|                 |                                                                                                                               |     |  |

| 5               | SOFTWARE APPLICATION NOTES                                                                                                    |     |  |

|                 | 5.1 HOST SETUP OF THE QSPAN II PCI BRIDGE                                                                                     | .30 |  |

|                 | 5.2 Q-Bus Configuration                                                                                                       |     |  |

|                 | 5.3 EEPROM CONFIGURATION                                                                                                      | .32 |  |

| ANNEX A | POWERQUICC CPU                    | 33 |

|---------|-----------------------------------|----|

| ANNEX B | QSPAN II <sup>TM</sup> BUS BRIDGE | 35 |

| ANNEX C | RAM/ROM                           | 36 |

| ANNEX D | DOCUMENTATION REFERENCE           | 37 |

| ANNEX E | DOCUMENT'S HISTORY                | 38 |

## List of Tables

| TABLE 1:  | LIST OF USED ABBREVIATIONS                                  | 6  |

|-----------|-------------------------------------------------------------|----|

| TABLE 2:  | <b>NPMC-860-4S0</b> MEMORY MAP                              | 15 |

| TABLE 3:  | POWERQUICC PORT PIN USAGE (PORT A)                          | 16 |

| TABLE 4:  | POWERQUICC PORT PIN USAGE (PORT B)                          | 16 |

| TABLE 5:  | POWERQUICC PORT PIN USAGE (PORT C)                          | 17 |

| TABLE 6:  | POWERQUICC PORT PIN USAGE (PORT D)                          | 17 |

| TABLE 7:  | NPMC-860-4S0 INTERRUPT STRUCTURE                            |    |

| TABLE 8:  | STATUS REGISTER 1                                           | 19 |

| TABLE 9:  | CONTROL/STATUS REGISTER 2                                   | 20 |

| TABLE 10: | STATUS REGISTER 3                                           | 20 |

| TABLE 11: | PMC CONNECTOR P11                                           |    |

| TABLE 12: | PMC CONNECTOR P12                                           |    |

| TABLE 13: | PIN ASSIGNMENT OF THE PMC CONNECTOR P14                     | 26 |

| TABLE 14: | DESCRIPTION P14 SIGNALS                                     | 27 |

| TABLE 15: | GENERAL PIN ASSIGNMENT OF THE FRONT-PANEL CONNECTORS S1 - 4 |    |

| TABLE 16: | JP1 BDM AND IEEE 1149.1 CONNECTOR PINOUT OPTIONS            | 29 |

| TABLE 17: | LATTICE PROGRAMMING PORT                                    | 29 |

| TABLE 18: | NPMC-860-4S0 MEMORY MAP IN THE CONFIGURATION SPACE          | 30 |

| TABLE 19: | NPMC-860-4S0 MEMORY MAP IN THE PCI MEMORY SPACE             | 31 |

## **List of Figures**

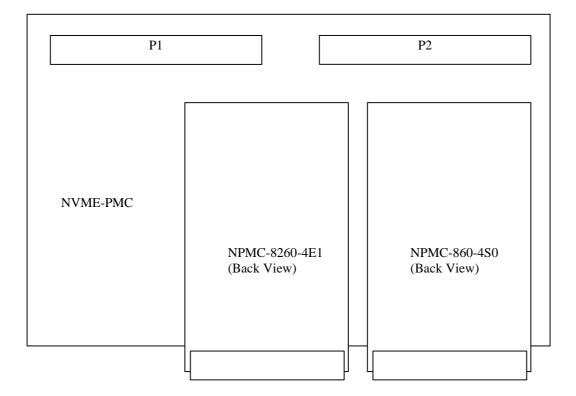

| FIGURE 1: | NPMC-860-4S0 ON A VMEBUS CARRIER                 | 7  |

|-----------|--------------------------------------------------|----|

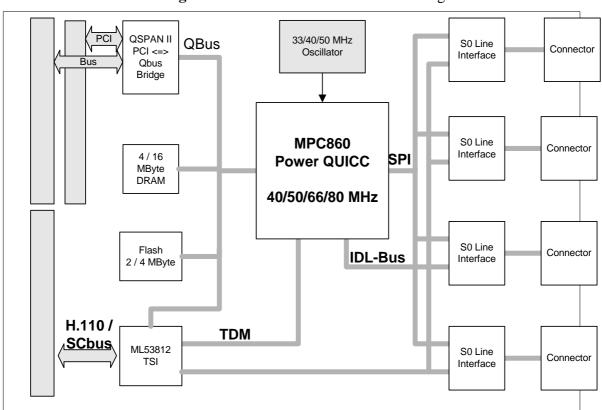

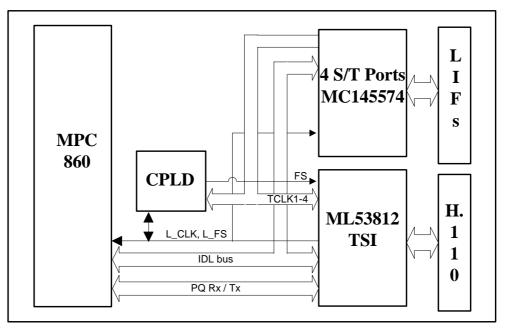

| FIGURE 2: | NPMC-860-4S0 BLOCK DIAGRAM                       | 8  |

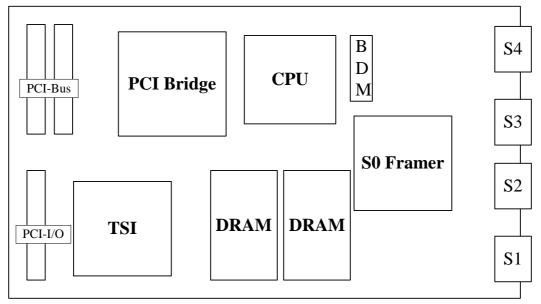

| FIGURE 3: | LOCATION DIAGRAM OF THE NPMC-860-4S0 (SCHEMATIC) | 12 |

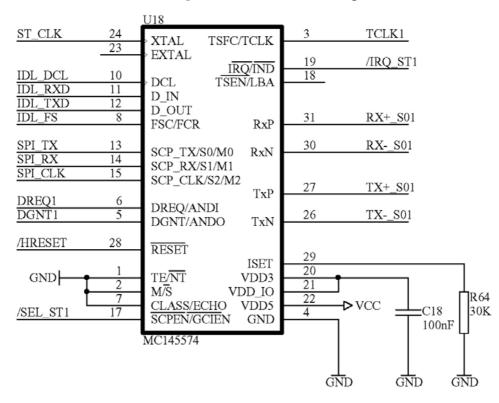

| FIGURE 4: | TDM BUS ORGANISATION AND SYNCHRONISATION         | 21 |

| FIGURE 5: | S/T Port Setup                                   | 22 |

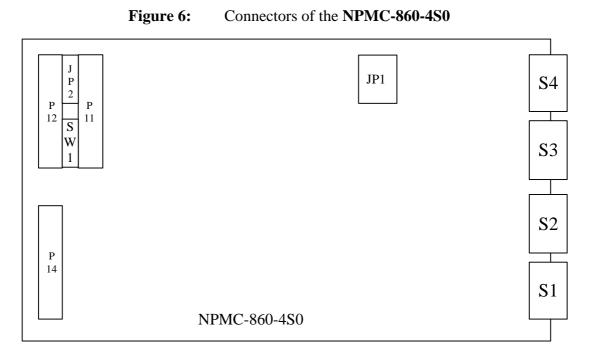

| FIGURE 6: | CONNECTORS OF THE NPMC-860-4S0                   | 23 |

|           |                                                  |    |

## Conventions

If not otherwise specified, addresses and memory maps are written in hexadecimal notation, identified by 0x.

Table 1 gives a list of the abbreviations used in this document:

| Abbreviation                                      | Description                                                |  |

|---------------------------------------------------|------------------------------------------------------------|--|

|                                                   |                                                            |  |

| b                                                 | Bit, binary                                                |  |

| В                                                 | byte                                                       |  |

| CPU                                               | Central Processing Unit                                    |  |

| DMA                                               | Direct Memory Access                                       |  |

| Flash                                             | Programmable ROM                                           |  |

| H.110                                             | Time-Slot Interchange Bus                                  |  |

| ISDN                                              | Integrated Services Digital Network                        |  |

| Κ                                                 | kilo (factor 400 in hex, factor 1024 in decimal)           |  |

| LIU                                               | Line Interface Unit                                        |  |

| М                                                 | mega (factor 10,0000 in hex, factor 1,048,576 in dec)      |  |

| MHz                                               | 1,000,000 Herz                                             |  |

| ML53812                                           | Oki H.110 Controller                                       |  |

| MPC860                                            | Embedded processor from Motorola                           |  |

| PowerQUICC MPC860                                 |                                                            |  |

| Qbus                                              | PowerPC processor bus                                      |  |

| QSpan II                                          | Tundra PCI $\rightarrow$ 60x bus interface device          |  |

| RAM                                               | Random Access Memory                                       |  |

| ROM                                               | Read Only Memory                                           |  |

| SCbus                                             | Time-Slot Interchange Bus of the SCSA, subset of H.110 bus |  |

| SCC                                               | Serial Communication Controller of the MPC860              |  |

| SCSA                                              | Signal Computing System Architecture                       |  |

| SDRAM                                             | Synchronous Dynamic RAM                                    |  |

| SMC Serial Communication Controller of the MPC860 |                                                            |  |

| SRAM Static RAM                                   |                                                            |  |

| S/T port                                          | framer and line interface for basic rate ISDN              |  |

| TDM                                               | Time Division Multiplex                                    |  |

| TSA                                               | Time Slot Assigner                                         |  |

| TSI                                               | Time Slot Interchange                                      |  |

|                                                   |                                                            |  |

**Table 1:**List of used Abbreviations

## **1** Introduction

The **NPMC-860-4S0** is a high performance standard CPU PCI Mezzanine Card Type 1. It can be plugged onto any carrier board supporting PMC standards:

Figure 1: NPMC-860-4S0 on a VMEbus carrier

The NPMC-860-4S0 has the following mayor features on-board:

- PowerQUICC MPC860 based Embedded PowerPC Architecture

- Front-panel I/O

- PCI Bus interface

- Single Slot VME/cPCI solution together with the PMC carrier board

Figure 2: NPMC-860-4S0 Block Diagram

The onboard devices are in detail as follows:

#### • Memory

| DRAM:       | The <b>NPMC-860-4S0</b> provides 4 or 16 MByte EDO DRAM onboard.<br>The DRAM is 32 bit wide. |

|-------------|----------------------------------------------------------------------------------------------|

| Flash PROM: | The 8 bit boot Flash PROM provides a maximum capacity of 4 MByte.                            |

| Interfaces  |                                                                                              |

• Interfaces

PCI: The **NPMC-860-4S0** includes a 32 bit 33 MHz PCI bus interface.

• I/O

The 4 S0 line interfaces are connected to the front panel connectors. The SCbus is connected to the PCI I/O connector.

T. C.

### • CPU

Depending on the assembled CPU type the PowerQUICC runs with a minimum frequency of 50 MHz. (40 MHz, 66 MHz, or 80 MHz versions are optionally available)

## **1.1 Specification**

| Processor                                                                            | PowerQUICC MPC860                                           |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------|

| PMC-Module                                                                           | Standard PCI Mezzanine Card Type 1                          |

| PCI to QBUS bridge                                                                   | QSPAN II                                                    |

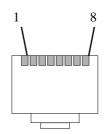

| I/O                                                                                  | 4 RJ45 connectors                                           |

| Main Memory                                                                          | 4 / 16 MByte EDO DRAM                                       |

| Flash PROM                                                                           | 2 / 4 MByte Flash PROM, on-board programmable               |

| Firmware                                                                             | OK1, PSOS BSP, VxWorks BSP (on request)                     |

| Power consumption                                                                    | 3.3V 0,8A<br>5.0V 0,5A                                      |

| Environm. conditions<br>Temperature (operating)<br>Temperature (storage)<br>Humidity | 0°C to +50°C<br>-40°C to +85°C<br>5 % to 95 % noncondensing |

| Standards compliance                                                                 | PCI Rev. 2.2<br>P1386.1 / Draft 2.4                         |

### **2** Installation

### 2.1 Safety Note

To ensure proper functioning of the **NPMC-860-4S0** during its usual lifetime take the following precautions before handling the board.

### CAUTION

Malfunction or damage to the board or connected components

Electrostatic discharge and incorrect board installation and uninstallation can damage circuits or shorten their lifetime.

- Before installing or uninstalling the board read this installation section

- Before installing or uninstalling the **NPMC-860-4S0**, read the Installation Guide and the User's Manual of the **NPMC-860-4S0** carrier board

- Before installing or uninstalling the **NPMC-860-4S0** on a carrier board or both in a VME/cPCI rack:

- Check all installed boards and modules for steps that you have to take before turning on or off the power.

- Take those steps.

- Finally turn on or off the power.

- Before touching integrated circuits ensure to take all require precautions for handling electrostatic devices.

- Ensure that the **NPMC-860-4S0** is connected to the carrier board via all PMC connectors and that the power is available on both PMC connectors (GND, +5V, and +3,3V).

- When operating the board in areas of strong electromagnetic radiation ensure that the module

- is bolted the front panel or VME/cPCI rack

- and shielded by closed housing.

### 2.2 Installation Prerequisites and Requirements

#### IMPORTANT

Before powering up

• check this section for installation prerequisites and requirements

#### 2.2.1 Requirements

The installation requires only

- a carrier board for connecting the **NPMC-860-4S0**

- power supply

#### 2.2.2 Power supply

The power supply for the NPMC-860-4S0 must meet the following specifications:

- required for the module:

- +3,3V / 0,8A typical

- +5,0V / 0,5A typical

### 2.2.3 Location Overview

Figure 3 highlights the position of the important components. Depending on the board type it may be that your board does not include all components shown in the location diagram.

Figure 3: Location diagram of the NPMC-860-4S0 (schematic)

Top View

Bottom View

### 2.3 Automatic Power Up

In the following situations the **NPMC-860-4S0** will automatically be reset and proceed with a normal power up.

Voltage sensor

The voltage sensor generates a reset

- when +5V voltage level drops below 4,6V

- when +5V voltage level rises above 5,4V

- or when the carrier board signals a PCI Reset

#### Watchdog timer

Per factory default the watchdog timer of the PowerQUICC is disabled. If the watchdog timer is enabled, it generates an non-maskable interrupt (NMI) followed by a reset when it is not retriggered by software (see the PowerQUICC users manual).

### 2.4 Statement on Environmental Protection

### 2.4.1 Compliance to RoHS Directive

Directive 2002/95/EC of the European Comission on the "Restriction of the use of certain Hazardous Substances in Electrical and Electronic Equipment" (RoHS) predicts that all electrical and electronic equipment being put on the European market after June 30th, 2006 must contain lead, mercury, hexavalent chromium, polybrominated biphenyls (PBB) and polybrominated diphenyl ethers (PBDE) and cadmium in maximum concentration values of 0.1% respective 0.01% by weight in homogenous materials only.

As these harzadous substances are currently used with semiconductors, plastics (i.e. semiconductor packages, connectors) and soldering tin any hardware product is affected by the RoHS directive if it does not belong to one of the groups of products exempted from the RoHS directive.

Although many of hardware products of N.A.T. are exempted from the RoHS directive it is a declared policy of N.A.T. to provide all products fully compliant to the RoHS directive as soon as possible. For this purpose since January 31st, 2005 N.A.T. is requesting RoHS compliant deliveries from its suppliers. Special attention and care has been payed to the production cycle, so that whereever and whenever possible RoHS components are used with N.A.T. hardware products already.

### 2.4.2 Compliance to WEEE Directive

Directive 2002/95/EC of the European Comission on "Waste Electrical and Electronic Equipment" (WEEE) predicts that every manufacturer of electrical and electronical equipment which is put on the European market has to contribute to the reuse, recycling and other forms of recovery of such waste so as to reduce disposal. Moreover this directive refers to the Directive 2002/95/EC of the European Comission on the "Restriction of the use of certain Hazardous Substances in Electrical and Electronic Equipment" (RoHS).

Having its main focus on private persons and households using such electrical and electronic equipment the directive also affects business-to-business relationships. The directive is quite restrictive on how such waste of private persons and households has to be handled by the supplier/manufacturer, however, it allows a greater flexibility in business-to-business relationships. This pays tribute to the fact with industrial use electrical and electronical products are commonly intergrated into larger and more complex envionments or systems that cannot easily be split up again when it comes to their disposal at the end of their life cycles.

As N.A.T. products are solely sold to industrial customers, by special arrangement at time of purchase the customer agreed to take the responsibility for a WEEE compliant disposal of the used N.A.T. product. Moreover, all N.A.T. products are marked according to the directive with a crossed out bin to indicate that these products within the European Community must not be disposed with regular waste.

If you have any questions on the policy of N.A.T. regarding the Directive 2002/95/EC of the European Comission on the "Restriction of the use of certain Hazardous Substances in Electrical and Electronic Equipment" (RoHS) or the Directive 2002/95/EC of the European Comission on "Waste Electrical and Electronic Equipment" (WEEE) please contact N.A.T. by phone or e-mail.

### 2.4.3 Compliance to CE Directive

Compliance to the CE directive is declared. A 'CE' sign can ce found on the PCB.

### 2.4.4 Product Safety

The board complies to EN60950 and UL1950.

## **3** Hardware Details

### 3.1 Memory Map

All addresses are set up by programming the corresponding Chip-Select Decoder of the PowerQUICC.

| Device     | CS   | Function                 | Notes                                   |

|------------|------|--------------------------|-----------------------------------------|

|            | Line |                          |                                         |

| Flash-PROM | CS0  | CS for FLASH             | 2/4 MByte Flash-Prom (8 Bit wide)       |

| DRAM       | CS1  | CS for DRAM              | 4/16 MByte EDO DRAM (32 Bit wide)       |

|            | CS2  | not used                 |                                         |

| PCI        | CS3  | CS for PMC $\rightarrow$ | there are two PCI images available      |

|            |      | PCI bus access           | selected by the IMS-Signal. This Signal |

|            |      |                          | is generated by the Port D Bit 15       |

| QSPAN      | CS4  | Qbus access to           |                                         |

|            |      | the QSPAN II             |                                         |

|            |      | Registers                |                                         |

| TSI        | CS5  | CS for theTSI            |                                         |

|            | CS6  | not used                 |                                         |

| I/O        | CS7  | CPLD Registers,          | a number of control/status registers is |

|            |      | SCbus ID                 | implemented in a CPLD                   |

### 3.2 PowerQUICC Port Pins Usage

| Signal Function | <b>PowerQUICC Port A Pin</b> | Description                                                                                                                |

|-----------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| DGNT1           | PA15                         | GNT signal for S/T port 1                                                                                                  |

| DREQ4           | PA14                         | REQ signal for S/T port 4                                                                                                  |

| MC TxD          | PA13                         | Message Channel Transmit                                                                                                   |

| MC RxD          | PA12                         | Message Channel Receive                                                                                                    |

| IDL RxD         | PA11                         | IDL Channel Receive                                                                                                        |

| IDL TxD         | PA10                         | IDL Channel Transmit                                                                                                       |

| TSI LSI1        | PA9                          | Time Slot Assigner Bus data bit 1, output<br>of MPC860, input to ML53812 H.110<br>controller (Time Slot Interchange (TSI)) |

| TSI LSO1        | PA8                          | Time Slot Assigner Bus data bit 1, input<br>to MPC860, output of ML53812 H.110<br>controller (Time Slot Interchange (TSI)) |

| IDL DCL         | PA7                          | IDL bus clock                                                                                                              |

| MC CLK          | PA6                          | Message Channel clock                                                                                                      |

| IDL DCL         | PA5                          | IDL bus clock                                                                                                              |

| DREQ3           | PA4                          | REQ signal for S/T port 3                                                                                                  |

| DREQ2           | PA3                          | REQ signal for S/T port 2                                                                                                  |

| IDL DCL         | PA2                          | IDL bus clock                                                                                                              |

| DREQ1           | PA1                          | REQ signal for S/T port 1                                                                                                  |

| IDL DCL         | PA0                          | IDL bus clock                                                                                                              |

### **Table 3:**PowerQUICC Port Pin Usage (Port A)

Table 4:

PowerQUICC Port Pin Usage (Port B)

| Signal Function | <b>PowerQUICC Port B Pin</b> | Description                    |

|-----------------|------------------------------|--------------------------------|

| not used        | PB31                         | not used                       |

| SPI CLK         | PB30                         | SPI bus clock                  |

| SPI RX          | PB29                         | SPI bus Receive                |

| SPI TX          | PB28                         | SPI bus Transmit               |

| SDA_PQ          | PB27                         | I <sup>2</sup> C data          |

| SCL_PQ          | PB26                         | I <sup>2</sup> C clock         |

| SMC1 TxD        | PB25                         | SMC1 Channel Transmit          |

| SMC1 RxD        | PB24                         | SMC1 Channel Receive           |

| /SDACK1         | PB23                         | DMA Ack to QSpan II            |

| not used        | PB22                         | not used                       |

| PZMP4*          | PB21                         | Point-to-Multi-Point channel 4 |

| PZMP3*          | PB20                         | Point-to-Multi-Point channel 3 |

| PZMP2*          | PB19                         | Point-to-Multi-Point channel 2 |

| PZMP1*          | PB18                         | Point-to-Multi-Point channel 1 |

| NT4*            | PB17                         | TE/NT selection channel 4      |

| NT3*            | PB16                         | TE/NT selection channel 3      |

| NT2*            | PB15                         | TE/NT selection channel 2      |

| NT1*            | PB14                         | TE/NT selection channel 1      |

Signals with asterisk (\*) are described in detail below.

| Signal Function | PowerQUICC Port C Pin | Description               |

|-----------------|-----------------------|---------------------------|

| /DREQ1          | PC15                  | DMA REQ from QSpan II     |

| DGNT4           | PC14                  | GNT signal for S/T port 4 |

| DGNT3           | PC13                  | GNT signal for S/T port 3 |

| DGNT2           | PC12                  | GNT signal for S/T port 2 |

| /IRQST4         | PC11                  | Interrupt S/T port 4      |

| /IRQST3         | PC10                  | Interrupt S/T port 3      |

| /IRQST2         | PC9                   | Interrupt S/T port 2      |

| /IRQST1         | PC8                   | Interrupt S/T port 1      |

| IDL FS          | PC7                   | IDL bus frame sync        |

| IDL FS          | PC6                   | IDL bus frame sync        |

| IDL FS          | PC5                   | IDL bus frame sync        |

| IDL FS          | PC4                   | IDL bus frame sync        |

|                 |                       |                           |

#### **Table 5:**PowerQUICC Port Pin Usage (Port C)

| Table 6: | PowerQUICC Port Pin Usage ( | Port D) |

|----------|-----------------------------|---------|

|----------|-----------------------------|---------|

| Signal Function | PowerQUICC Port D Pin | Description               |

|-----------------|-----------------------|---------------------------|

| IMSEL           | PD15                  | Image Select for QSpan II |

| LED4*           | PD14                  | Front Panel LED           |

| LED3*           | PD13                  | Front Panel LED           |

| LED2*           | PD12                  | Front Panel LED           |

| LED1*           | PD11                  | Front Panel LED           |

| not used        | PD10                  |                           |

| not used        | PD9                   |                           |

| not used        | PD8                   |                           |

| not used        | PD7                   |                           |

| SEL ST4*        | PD6                   | enable S/T port 4         |

| SEL ST3*        | PD5                   | enable S/T port 3         |

| SEL ST2*        | PD4                   | enable S/T port 2         |

| SEL ST1*        | PD3                   | enable S/T port 1         |

|                 |                       |                           |

All port signals are tristate after Power-Up, until programmed differently. Output signals marked with an asterisk (\*) are described below in their (active) low state:

- PZMP1 4 selection of point-to-point or point-to-multi-point connection, low = point-to-point, high = point-to-multi-point

- NT1 4 selection of TE/NT interface, low = TE (default), high = NT

- LED1 4 lit when set low

- SEL ST1 4 enable S/T ports, low = enabled

### **3.3** Interrupt Structure

The **NPMC-860-4S0** has the following interrupt structure:

| Interrupt source | PowerQUICC Interrupt level  |

|------------------|-----------------------------|

| NC               | IRQ-Level 0 (highest level) |

| for future use   | IRQ-Level 1                 |

| QSPAN II         | IRQ-Level 2                 |

| TSI              | IRQ-Level 3                 |

| NC               | IRQ-Level 4                 |

| NC               | IRQ-Level 5                 |

| NC               | IRQ-Level 6                 |

| for future use   | IRQ-Level 7 (lower level)   |

The interrupt pins of the 4 S0 interface chips are routed to the port pins PC8 - PC11 of the PowerQUICC, which are capable of generating interrupts. They are not routed to dedicated IRQ-pins.

### 3.4 Control / Status Registers

MPC860 CS7 (CSIO) selects the Control / Status Registers. The address range decoded by hardware is 4 bytes. Larger address ranges mirror every 4 bytes. Pure Status Registers are read-only, Status / Control Registers are read/write.

### 3.4.1 Status Register 1

Status Register 1 is accessed with address offset 0x0 to the CSIO base address programmed for CS7. By means of this register the SCbus slot address is readable.

| Bit    | <b>Read/Write</b> | Status Information          |

|--------|-------------------|-----------------------------|

| Number |                   |                             |

|        |                   |                             |

| Bit 7  | R                 | not used, reads as 0        |

| Bit 6  | R                 | not used, reads as 0        |

| Bit 5  | R                 | not used, reads as 0        |

| Bit 4  | R                 | SCbus slot address bit SL_4 |

| Bit 3  | R                 | SCbus slot address bit SL_3 |

| Bit 2  | R                 | SCbus slot address bit SL_2 |

| Bit 1  | R                 | SCbus slot address bit SL_1 |

| Bit 0  | R                 | SCbus slot address bit SL_0 |

**Table 8:**Status Register 1

### 3.4.2 Control/Status Register 2

Control/Status Register 2 is accessed with address offset 0x4 to the CSIO base address programmed for CS7. By means of this register the status of the Timeout bits is readable.

The Timeout bits are generated in a CPLD and mirror the activity of a TE port. If a TE port is active, i.e. generates a SYNC signal to the logic, the corresponding Timeout bit will read 0. If there is no (more) activity on this port, hence it is no longer suitable to be source of local synchronisation, the corresponding Timeout bit will read 1.

These bits are implemented for applications where there is no TSI device assembled. Additional information on this is available on request. As by default the TSI device is assembled, the Timeout bits are not used in a standard application.

Also, for NT mode the FIX pins of the MC145574 S/T framers are settable/readable. By means of these bits fixed / adaptive timing can be selected. Refer to the MC145574 manual for further details.

| Bit    | Read/Write | Status Information                            |

|--------|------------|-----------------------------------------------|

| Number |            |                                               |

| Bit 7  | R          | TIMEOUT bit of the MC145574 S/T framer port 4 |

| Bit 6  | R          | TIMEOUT bit of the MC145574 S/T framer port 3 |

| Bit 5  | R          | TIMEOUT bit of the MC145574 S/T framer port 2 |

| Bit 4  | R          | TIMEOUT bit of the MC145574 S/T framer port 1 |

| Bit 3  | R/W        | FIX bit of the MC145574 S/T framer port 4     |

| Bit 2  | R/W        | FIX bit of the MC145574 S/T framer port 3     |

| Bit 1  | R/W        | FIX bit of the MC145574 S/T framer port 2     |

| Bit 0  | R/W        | FIX bit of the MC145574 S/T framer port 1     |

### 3.4.3 Status Register 3

Status Register 3 is accessed with address offset 0x8 to the CSIO base address programmed for CS7. By means of this register the status of the TSEN pins of the framers are readable. Refer to the MC145574 manual for further details.

| Bit    | <b>Read/Write</b> | Status Information   |

|--------|-------------------|----------------------|

| Number |                   |                      |

|        |                   |                      |

| Bit 7  | R                 | not used, reads as 0 |

| Bit 6  | R                 | not used, reads as 0 |

| Bit 5  | R                 | not used, reads as 0 |

| Bit 4  | R                 | not used, reads as 0 |

| Bit 3  | R                 | TSEN pin framer 4    |

| Bit 2  | R                 | TSEN pin framer 3    |

| Bit 1  | R                 | TSEN pin framer 2    |

| Bit 0  | R                 | TSEN pin framer 1    |

| <b>Table 10:</b> Status Register 3 |

|------------------------------------|

|------------------------------------|

### 3.5 IDL Bus Operation

The four S/T ISDN framers, the MPC860 CPU TDM port, and the ML52812 H.110 TSI device are interconnected by an IDL bus. This IDL bus is mastered either by one of the framers, or by the TSI device. The IDL bus master provides a Sync signal to a LREF input of the TSI device, which generates local sync and clock for the IDL bus from it. Any framer and the TSI device (if SCbus/H.110 bus slave) can be sync source for the IDL bus. This is either decided be software, or by hardware implemented in a CPLD, which choses an active TE port to be master, and switches to another active one, if the one it is locked to goes inactive. If there is no active port at all, a free running mode may be selected. Which port is sourcing a valid sync can also be read from Control/Status Register 2 described above. The TIMEOUT bits for each port read 1, if there is no carrier detected by the S/T chip, and reads 0, if the S/T chip locks to the line.

#### 3.6 Time Division Multiplex Bus Structure

The TDM bus structure connects the IDL bus of the framers to the local TDM bus between CPU and TSI device, and to the backplane SCbus/H.110 bus. Timeslot assignment is done within the framers and the CPU, switching of timeslots between the different devices and the backplane is done by the TSI device. The TDM interconnect structure is shown below:

**Figure 4:** TDM Bus Organisation and Synchronisation

### 3.7 S/T Port Setup

The following figure shows the connections of a S/T port device. All 4 port devices are connected alike.

Figure 5:S/T Port Setup

The IDL bus (described above) connects the framers to the TSI device. The S/T port devices are programmed by the SPI port of the MPC860. DREQ, DGNT, SCP-/GCIEN are connected to CPU port pins and thus programmable for any application's needs. The TCLK signal may fulfill different tasks: clock output, sync output in TE mode, or FIX input in NT mode. Hence, the CPLD pins the TCLKx signals are connected to may be programmed as input or output. This depends on the setting of the NTx inputs connected to CPU port pins. If a channel is set to be NT (and the corresponding CPU port pin NTx is set accordingly), the CPLD TCLKx pin will be an output and drive the logic state programmed in the FIXx bits of the Control/Status Register 2 described above.

Please refer to the MC145574 User's Manual for additional information. Sample driver code is available from N.A.T..

### 4 Connectors

### 4.1 Connector Overview

### 4.2 Switch Settings

Switch No. 1 of DIL Switch SW1 is used for a Background Debug Mode Tool. This is a Power-Up option. If a BDM tool is to be used, Switch No. 1 of DIL Switch SW1 needs to be set to ON **before** powering up the module.

Default: Switch No. 1 of DIL Switch SW1 is set to OFF

Switch No. 2 of DIL Switch SW1 is used for factory test and its setting should not be altered by the user.

Default: Switch No. 2 of DIL Switch SW1 is set to OFF

### 4.3 PMC Connector P11

| Ext. Signal | Pin No. | <b>PCI-Signal</b> | <b>PCI-Signal</b> | Pin No. | Ext. Signal |

|-------------|---------|-------------------|-------------------|---------|-------------|

|             |         |                   |                   |         |             |

| N.C.        | 1       | TCK               | -12V              | 2       | N.C.        |

| GND         | 3       | GND               | /INT A            | 4       | /IRQ-       |

|             |         |                   |                   |         | QSPAN       |

| N.C.        | 5       | /INT B            | /INT C            | 6       | N.C.        |

| N.C.        | 7       | bus mode 1        |                   | 8       | +5V         |

| N.C.        | 9       | /INT D            | PCI_RSV1          | 10      | N.C.        |

| GND         | 11      | GND               | PCI_RSV2          | 12      | N.C.        |

| CLK         | 13      | CLK               | GND               | 14      | N.C.        |

| GND         | 15      | GND               | /GNT              | 16      | /GNT        |

| /REQ        | 17      | /REQ              | +5V               | 18      | +5V         |

| N.C.        | 19      | V (I/O)           | AD31              | 20      | PCI_AD31    |

| PCI_AD28    | 21      | AD28              | AD27              | 22      | PCI_AD22    |

| PCI_AD25    | 23      | AD25              | GND               | 24      | GND         |

| GND         | 25      | GND               | CBE3              | 26      | /CBE3       |

| PCI_AD22    | 27      | AD22              | AD21              | 28      | PCI_AD21    |

| PCI_AD19    | 29      | AD19              | +5V               | 30      | +5V         |

| N.C.        | 31      | V (I/O)           | AD17              | 32      | PCI_AD17    |

| /FRAME      | 33      | /FRAME            | GND               | 34      | GND         |

| GND         | 35      | GND               | /IRDY             | 36      | /IRDY       |

| /DEVSEL     | 37      | /DEVSEL           | +5V               | 38      | +5V         |

| GND         | 39      | GND               | /LOCK             | 40      | N.C.        |

| N.C.        | 41      | /SDONE            | /SB0              | 42      | N.C.        |

| PAR         | 43      | PAR               | GND               | 44      | GND         |

| N.C.        | 45      | V (I/O)           | AD15              | 46      | PCI_AD15    |

| PCI_AD12    | 47      | AD12              | AD11              | 48      | PCI_AD11    |

| PCI_AD09    | 49      | AD09              | +5V               | 50      | +5V         |

| GND         | 51      | GND               | /CBE0             | 52      | /CBE0       |

| PCI_AD06    | 53      | AD06              | AD05              | 54      | PCI_AD05    |

| PCI_AD04    | 55      | AD04              | GND               | 56      | GND         |

| N.C.        | 57      | V (I/O)           | AD03              | 58      | PCI_AD03    |

| PCI_AD02    | 59      | AD02              | AD01              | 60      | PCI_AD01    |

| PCI_AD00    | 61      | AD00              | +5V               | 62      | +5V         |

| GND         | 63      | GND               | /REQ64            | 64      | N.C.        |

### **Table 11:**PMC Connector P11

### 4.4 PMC Connector P12

| Ext. Signal | Pin No. | PCI-Signal | PCI-Signal | Pin No. | Ext. Signal |

|-------------|---------|------------|------------|---------|-------------|

| N.C.        | 1       | +12V       | /TRST      | 2       | N.C.        |

| N.C.        | 3       | TMS        | TDO        | 4       | N.C.        |

| N.C.        | 5       | TDI        | GND        | 6       | GND         |

| GND         | 7       | GND        | PCI_RSV3   | 8       | N.C.        |

| N.C.        | 9       | PCI_RSV    | PCI RSV4   | 10      | N.C.        |

| N.C.        | 11      | BUS-MODE 2 | +3.3V      | 12      | +3.3V       |

| /RST        | 13      | /RTS       | BUS-MODE 3 | 14      | N.C.        |

| +3.3V       | 15      | +3.3V      | BUS-MODE 4 | 16      | N.C.        |

| N.C.        | 17      | PCI_RSV    | GND        | 18      | GND         |

| PCI_AD30    | 19      | AD30       | AD29       | 20      | PCI_AD29    |

| GND         | 21      | GND        | AD26       | 22      | PCI_AD26    |

| PCI_AD24    | 23      | AD24       | +3.3V      | 24      | +3.3V       |

| /IDSEL      | 25      | IDSEL      | AD23       | 26      | PCI_AD23    |

| +3.3V       | 27      | +3.3V      | AD20       | 28      | PCI_AD20    |

| PCI_AD18    | 29      | AD18       | GND        | 30      | GND         |

| PCI_AD16    | 31      | AD16       | /CBE2      | 32      | /CBE2       |

| GND         | 33      | GND        | PCI_RESVD  | 34      | N.C.        |

| /TRDY       | 35      | /TRDY      | +3.3V      | 36      | +3.3V       |

| GND         | 37      | GND        | /STOP      | 38      | /STOP       |

| /PERR       | 39      | /PERR      | GND        | 40      | GND         |

| +3.3V       | 41      | +3.3V      | /SERR      | 42      | /SERR       |

| /CBE1       | 43      | /CBE1      | GND        | 44      | GND         |

| PCI_AD14    | 45      | AD14       | AD13       | 46      | PCI_AD13    |

| GND         | 47      | GND        | AD10       | 48      | PCI_AD10    |

| PCI_AD08    | 49      | AD08       | +3.3V      | 50      | +3.3V       |

| PCI_AD07    | 51      | AD07       | PCI_RESV   | 52      | N.C.        |

| +3.3V       | 53      | +3.3V      | PCI_RESV   | 54      | N.C.        |

| N.C.        | 55      | PCI_RESV   | GND        | 56      | GND         |

| N.C.        | 57      | PCI_RESV   | PCI_RESV   | 58      | N.C.        |

| GND         | 59      | GND        | PCI_RESV   | 60      | N.C.        |

| N.C.        | 61      | ACK64      | +3.3V      | 62      | +3.3V       |

| GND         | 63      | GND        | PCI_RESV   | 64      | N.C.        |

### **Table 12:**PMC Connector P12

## 4.5 Pin Assignment of the PMC Connector -- P14 (PMC I/O)

| Pin No. | <b>PCI-Signal</b>                                                                                                                                                                                                                               | <b>PCI-Signal</b>                                                                                                                                                                                                                    | Pin No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ext. Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | L/O                                                                                                                                                                                                                                             | I/O                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CT D15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CT_D13<br>CT_D13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CT_D10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| -       |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CT_D8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CT_D5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CT_D3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -       |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CT_D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CT_D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21      | I/O                                                                                                                                                                                                                                             | I/O                                                                                                                                                                                                                                  | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | /FSYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23      | I/O                                                                                                                                                                                                                                             | I/O                                                                                                                                                                                                                                  | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 25      | I/O                                                                                                                                                                                                                                             | I/O                                                                                                                                                                                                                                  | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | /SCLKx2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27      | I/O                                                                                                                                                                                                                                             | I/O                                                                                                                                                                                                                                  | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | /C16+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |