# **Emperational Connecting Silicon, Software, and Strategies for Intelligent Systems**

$\bigcirc$

# LOCKING DOWN Iot EDGE PROCESSORS PG. 24

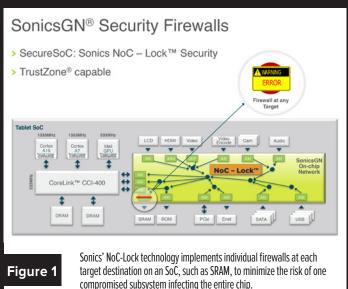

$\begin{array}{c} + CPU2 + + PCle \\ + GPU + + Enet + \\ + LCD + + Cam + \\ + HDMI + + SATA + \\ + SRAM + + USB + \\ + ROM + + Audio \\ + VIDEO + + \end{array}$

$\overline{\mathbf{O}}$

PU

**NOVEMBER 2015**

**VOLUME 13**

EMBEDDED-COMPUTING.COM

#7

PLUS Research Review An industry-university dev tools collaboration PG. 5

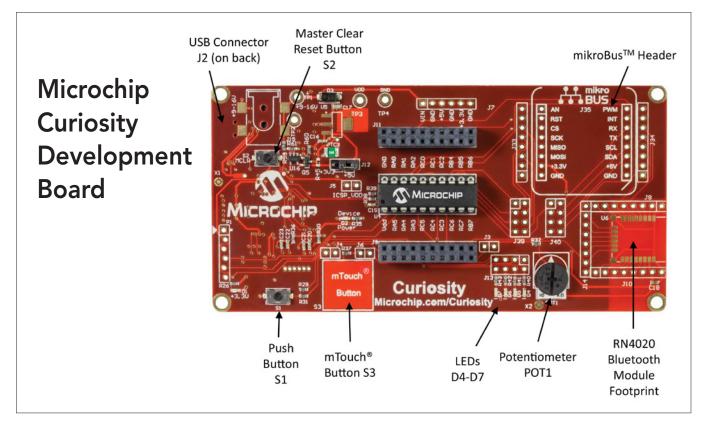

> **HOW-TO GUIDE** PWM CONTROL WITH MICROCHIP'S CURIOSITY DEV BOARD PG. 16

## **Annapolis Micro Systems** The FPGA Systems Performance Leader

# WILDSTAR OpenVPX Ecosystem

FPGA Processing Boards 1 to 3 Altera Stratix V or Xilinx Virtex 6 or 7 FPGAs per Slot

Input/Output Modules Include: **Quad 130** MSps thru **Quad 550** MSps A/D 1.5 GSps thru 5.0 GSps A/D **Quad 600** MSps D/A **Dual 1.5** GSps thru 4.0 GSps D/A

1 to 40 Gbit Ethernet SDR to FDR Infiniband

Open VPX Storage Up to 8 TBytes Per Slot 4 - 8 GBytes Per Second

> GEOINT. Ground Stations. SDR, Radar, Sigint, COMINT, ELINT, DSP, Network Analysis, Encryption, Image Processing, Pattern Matching, Oil & Gas Exploration, **Financial and** Genomic Algorithms,

Open VPX Switch 1 to 40 Gbit Ethernet SDR to FDR Infiniband

Chassis 4, 6 or 12 Slot Up to 14G

## High Performance Signal and Data Processing in Scalable COTS FPGA Computing Fabric

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com USA (410) 841-2514 www.annapmicro.com

# Why companies should focus on their core competency

By Rory Dear, Technical Contributor

rdear@opensystemsmedia.com

## When something is outside a company's core competency it's time to outsource in order to save time, money, and risk.

"To outsource, or not to outsource?" is the key dilemma facing decision makers from start-ups to SMEs to corporate behemoths. In smaller scale organisations, the temptation to want to do everything themselves may well stem from their inception; when startup funds were tight the last burden the fledgling CEO wanted to incur were additional expenses. The attraction of taking on learning a new task himself or delegating internal staff to do the same was naturally strong, and I speak from personal experience in describing how hard it can be to move away from that mindset.

I started in the embedded industry on the bottom rung of the proverbial ladder. As time progressed I quickly earned numerous promotions, and whilst performing new tasks I continued to simultaneously undertake my (technically) previous roles. Additionally, as new responsibilities were generated – tasks well outside my primary remit – I foolishly, enthusiastically, blindly volunteered myself. I describe this not as some nostalgic self-contemplation, but to draw you to the undeniable parallel this dilemma has at both the individual and organisational level. I eventually found myself working unsustainably long hours to encompass this unmanageable workload I had thrust upon myself. Far more importantly than the overall volume of work was the increasing detraction from my own core competency, which began to impact my personal success and has a parallel effect at the organisational level.

One poignant example I come across daily is companies involved in electronics often blindly insist on undertaking electronic design in-house. This may well stem from the same "we'll do everything" attitude of the earlier cited start-up CEO, and in fairness this is understandable – after all, he set out to create an electronics company and this is an electronics task, isn't it? Perhaps once upon a time, when the technology and tools were that much simpler, this would hold true. The reality today is electronics has exploded into an unfathomable number of highly specialist areas, most notably (for us) an entire ecosystem of embedded computing. The danger comes when those outside of that specific skills sphere, through lack of understanding of the complexities involved, have the temptation to attempt to undertake such design alone. Doing so necessitates pushing inexperienced personnel up a very sharp learning curve and leaving them to the wolves to overcome the numerous challenges long since understood and resolved by existing specialists with decades of training and experience. It involves significant cost – be that for hiring new employees or training existing ones and buying the latest tools – time, and, of course, risk. With project competition greater than ever these are the three fundamental aspects one rarely has room to play with. Interestingly, the primary objection to outsourcing such work, sometimes alongside pride, is cost.

The cost differential of outsourcing may appear vast due to those evaluating not including their employees' time as cost, nor appreciating that if internal staff take twice as long, they effectively cost twice as much – and a factor of two is usually understating the difference. It's also easy to exclude the costs of financing that learning curve and investing in the latest tools that may well only be for a single project. Far more importantly, what if it all goes wrong?

A comparison I like to use is your family vehicle's braking system. Most of us won't mechanically touch our cars at all, myself included, but some fancy themselves as budding hobbyist mechanics. Very few have such confidence in their success that they're willing to place their family's lives at risk by undertaking work on the brakes. I've no doubt that my cognitive abilities could eventually learn how to successfully undertake brake repair, but the issue is that I can't commit to the time to become an expert, and unless I was I would never place my family's lives at risk through failure. Replace "brake repair" with "electronic design" and "family" with "project" and I hope I've made my point.

Beyond avoiding the risk of losing important customers, outsourcing frees up employees to focus on their own core competencies. Maximum benefit and success at individual and company level is derived from dedicating time to your strengths. Trying to save your business money by avoiding outsourcing may end up costing you far more than that project ever would.

## Embedded computing D E S I G N

## Silicon

Microcontroller-based FPGAs hit the mark By Ted Marena, Microsemi

## Software

- **3** The theory behind product line engineering *By Curt Schwaderer, Editorial Director*

- **16** Look Ma, no code! PWM control in under five minutes with Microchip Curiosity development board *By Brandon Lewis, Assistant Managing Editor*

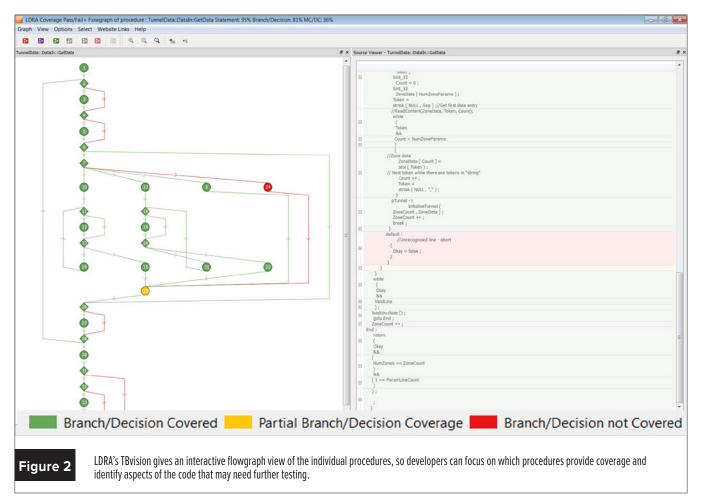

- 20 Testing the test: How to use coverage metrics for more effective embedded software testing *By John Thomas, LDRA Ltd.*

## **Strategies**

24 Ensuring trust in IoT with Trusted Platform Modules and Trusted Brokered IO *Q&A with Steve Hanna, Infineon and Trusted Computing Group; Stefan Thom, Microsoft and Trusted Computing Group*

## Departments

3

6

6

G

6

## Tracking Trends

Rory Dear, Technical Contributor

embedded-computing.com

Why companies should focus on their core competency

- **Research Review**

- Monique DeVoe, Managing Editor

An industry-university development tools collaboration

## loT Insider

Brandon Lewis, Assistant Managing Editor

So, how do you make money in IoT?

## 31 Editor's Choice

## Web Extras

Amazon launches IoT platform, embedded responds with off-the-shelf dev kits *By Brandon Lewis, Assistant Managing Editor opsy.st/AmazonIoT*

The search for a simpler, more cost-effective way to implement USB 3.0 functionality By Gordon Lunn and Lee Chee Ee, FTDI Chip opsy.st/USB3FTDI

## DOWNLOAD THE APP

Download the Embedded Computing Design app: iTunes: itun.es/iS67MQ Magzter: opsy.st/ecd-magzter

#### By Monique DeVoe, Managing Editor

mdevoe@opensystemsmedia.com

Development tools are important in all stages of the embedded design process, and research is no exception. Limited budgets can create extra challenges for universities, and the lack of inexpensive, but high-quality tools is a challenge faced by many researchers, including Dr. Luciano Ost, University of Leicester (http://le.ac.uk) Lecturer, Embedded Systems and Communications Research Group.

"The lack of electronic design automation (EDA) tools combining model flexibility, and fast and accurate evaluation of performance, power, and reliability is one of the major challenges currently faced by embedded researchers," Ost says, adding that even expensive, commercially available tools don't often meet modeling and simulation needs for emerging technologies.

Free, open source tools – especially those available to the research community – can be highly beneficial for students learning the embedded ropes and for researchers looking to advance the field. When companies and universities work together to share tools and knowledge in an open source format, good things can happen for the future of embedded computing.

Imperas (www.imperas.com) provides tools and solutions for embedded software development, debug and test, and has been working with universities around the world with its Imperas University Program, which provides academic and research institutions access to tools and virtual platform models.

"The Imperas University Program encourages participation in the embedded systems community in three ways: use on research projects, use in the classroom, and sharing of virtual platform models through the Open Virtual Platforms (OVP) Library," says Duncan Graham, University Program Manager at Imperas.

The OVP initiative (www.ovpworld.org) provides researchers access to a library of more than 150 CPU models and more than 200 peripheral and platform models, as well as Extendable Platform Kits (EPKs) – all open source and distributed using the Apache open source license. Libraries like this are very helpful to researchers like Ost who are working with the cutting edge of processing technology.

"The description of processors – i.e., register or gate-level – is rarely available to universities, and commercial licenses are

quite expensive," Ost says. "Having free tools with different state-of-the-art processor models allows the exploration of new system architectures."

Imperas launched OVP in 2008, providing free access for academic users to the model libraries in addition to APIs, the OVPsim simulator, and to the OVP Forum for technical questions and discussions for academic users. Users can also share their models, platforms, and tools they develop. In 2010, the Imperas University Program formalized and expanded the OVP program, providing access to Imperas' Multiprocessor/ Multicore Software Design Kits (M\*SDK) and QuantumLeap Parallel Simulation Accelerator tools.

Ost has found the tools provided through the Imperas University Program to be helpful for his research. He and his research team focus on multi- and many-core embedded systems, specifically runtime management techniques for performance, energy efficiency, and reliability improvement that must be conducted at the application, operating system, or architectural level. He uses system modeling tools and languages like SystemC as well as virtual platform simulation tools like Imperas' OVPsim, which help Ost and his team work with increasingly complex processors and software architectures.

"The high-speed simulation and debugging capabilities of Imperas tools facilitate us to extend FreeRTOS to support novel runtime techniques as well as to promote instructiondriven performance and power models," Ost says.

Ost also notes that free tools also facilitate collaborative projects between universities and external industry partners. In collaboration with the Federal University of Rio Grande do Sul (UFRGS) in Brazil, a fast and flexible fault injector framework, called OVPSim-FIM, was developed on the basis of OVPsim and presented at DFT 2015 (www.dfts.org). OVPSim-FM enables users to identify and critical soft errors in multi- and many-core systems at an early design phase. **ECD**

Read about the FlexTiles project developed through Imperas University Program and Imperas's future plans at opsy.st/ImperasUniversity.

## ADVERTISER INDEX

- 9 Anaren – Join the evolution

- 2 Annapolis Micro Systems, Inc. – WILDSTAR OpenVPX ecosystem

- 21 ATP Electronics, Inc. ATP Ruggedized IoT NAND flash storage solutions

- 19 COMMELL Systems Corporation 5th gen Intel Core i7/i5/i3 SBC

- 23 Digital Voice Systems, Inc. AMBE+2 Vocoder chip delivers high quality voice at low cost

- 12 Embedded World Get up to speed with the latest developments in your industry

- 29 Sheldon Instruments Improving inter-processor communication with software framework

- 27 Technologic Systems Superior embedded solutions

- 25 Toradex Engineering resources at your finger tips

- 32 WinSystems, Inc. Thinking beyond the board

- 30 WITTENSTEIN HighIntegrity Systems Watchdog strategies for RTOS enabled embedded systems

Get your free digital edition at embedded-computing.com/emag

Subscriptions: embedded-computing.com/subscribe subscriptions@opensystemsmedia.com

#### OpenSystems media.

2015 OpenSystems Media ® © 2015 Embedded Computing Design All registered brands and trademarks within Embedded Computing Design magazine are the property of their respective owners. iPad is a trademark of Apple Inc., registered in the U.S. and other countries. App Store is a service mark of Apple Inc. ISSN: Print 1542-6408, Online: 1542-6459

ENVIROINK body of this publicat

## Embedded COMPUTING

#### Embedded Computing Design Editorial/Creative Staff

Rich Nass, Brand Director rnass@opensystemsmedia.com Curt Schwaderer, Editorial Director cschwaderer@opensystemsmedia.com

Monique DeVoe, Managing Editor mdevoe@opensystemsmedia.com

Brandon Lewis, Assistant Managing Editor blewis@opensystemsmedia.com

#### Sales Group

Tom Varcie, Sales Manager tvarcie@opensystemsmedia.com (586) 415-6500 Rebecca Barker, Strategic Account Manager rbarker@opensystemsmedia.com (281) 724-8021 Eric Henry, Strategic Account Manager ehenry@opensystemsmedia.com (541) 760-5361 Kathleen Wackowski, Strategic Account Manager kwackowski@opensystemsmedia.com (978) 888-7367

Asia-Pacific Sales Elvi Lee, Account Manager elvi@aceforum.com.tw

#### **Reprints and PDFs**

Contact: Wyndell Hamilton, Wright's Media, wHamilton@wrightsmedia.com, 281-419-5725

#### **EMEA**

Rory Dear, Technical Contributor rdear@opensystemsmedia.com

James Rhoades-Brown – Europe james.rhoadesbrown@husonmedia.com Christian Hoelscher, Account Manager - Europe christian.hoelscher@husonmedia.com

Gerry Rhoades-Brown, Account Manager - Europe gerry.rhoadesbrown@husonmedia.com

Twyla Sulesky, Strategic Account Manager California

#### **OpenSystems Media Editorial/Creative Staff**

Military PROCESSING INDUSTRIAL PROVED IN TRACE PROCESSING INDUSTRIAL PROVED IN TRACE PROVED INTERPORT PROVED IN TRACE PROVED IN TRACE PROVED INTERPORT PROVED INTERPO Embedded syrme 🔥

John McHale, Group Editorial Director Military Embedded Systems PC/104 and Small Form Factors PICMG Systems & Technology VITA Technologies Signal Processing Design jmchale@opensystemsmedia.com

Joe Pavlat, Editorial Director PICMG Systems & Technology jpavlat@opensystemsmedia.com

Jerry Gipper, Editorial Director VITA Technologies jgipper@opensystemsmedia.com Steph Sweet, Creative Director Joann Toth, Contributing Designer Lisa Daigle, Assistant Managing Editor

Military Embedded Systems

#### Corporate

Patrick Hopper, Publisher phopper@opensystemsmedia.com Rosemary Kristoff, President rkristoff@opensystemsmedia.com John McHale, Executive Vice President jmchale@opensystemsmedia.com Rich Nass, Executive Vice President rnass@opensystemsmedia.com

PC/104 and Small Form Factors

ldaigle@opensystemsmedia.com Sally Cole, Senior Editor Military Embedded Systems

scole@opensystemsmedia.com Brandon Lewis, Assistant Managing Editor Industrial Embedded Systems PICMG Systems & Technology

Signal Processing Design blewis@opensystemsmedia.com

Jennifer Hesse, Managing Editor VITA Technologies

Joy Gilmore, E-cast Manager jgilmore@opensystemsmedia.com

Mariana Iriarte, Associate Editor Military Embedded Systems miriarte@opensystemsmedia.com

#### opensystemsmedia.com

Wayne Kristoff, CTO Emily Verhoeks, Financial Assistant Headquarters - ARIZONA: 16626 E. Avenue of the Fountains, Ste. 201 Fountain Hills, AZ 85268 Tel: (480) 967-5581 MICHIGAN: 30233 Jefferson, St. Clair Shores, MI 48082 Tel: (586) 415-6500

OpenSystems media.

Rory Dear, Technical Contributor

rdear@opensystemsmedia.com

kwitte@opensystemsmedia.com

Chris Rassiccia, Graphic Designer

**Regional Sales Managers**

Barbara Quinlan, Southwest bquinlan@opensystemsmedia.com

Denis Seger, Southern California dseger@opensystemsmedia.com

Svdele Starr. Northern California

sstarr@opensystemsmedia.com

tsulesky@opensystemsmedia.com

(480) 236-8818

(760) 518-5222

(775) 299-4148

(408) 779-0005

crassiccia@opensystemsmedia.com

David Diomede, Creative Services Director

ddiomede@opensystemsmedia.com

Konrad Witte, Senior Web Developer

By Brandon Lewis, Assistant Managing Editor

blewis@opensystemsmedia.com

A recent InfoWorld article proclaims "The Internet of Things is not paying the rent." In it, Adobe's VP of Mobile Matt Asay cites data from VisionMobile and McKinsey & Co. to point out that "less than 10 percent of IoT developers are making enough to support a reasonably sized team," and that "developers need to get real about what they're selling and to whom," which "probably involves a 'dull' enterprise-facing business." This begs the question, how do you make money in the IoT?

In a column last year on hardware commoditization I discussed the idea of "IoT-as-a-Service," wherein Internet of Things companies could potentially transition away from one-off IoT platform sales and into business models that allow for accretive growth by means of data and feature monetization. In this cloud-based approach, companies could establish service plans or provide additional features to end users similar to how your cell phone or cable company operate, generating recurring streams of income

## **Business Model Versatility**

#### Traditional Sales Models

- × Product Sale

- × Update/upgrade sale

- × Maintenance

- Consumable re-fill

- × Renewal

Traditional product-centric business models limit the earning capacity of Internet of Things (IoT) solutions as they are typically earmarked by a single income phase followed by extended periods of service and maintenance costs.

that continue to flow after the initial platform sale (or perhaps, giveaway) to help offset ongoing maintenance, service, and support costs. Furthermore, this paradigm permits a new way of thinking about the product development life cycle, as rather than offering a portfolio of hardware platforms each with different features engineered into individual SKUs, software can be utilized to enhance or reduce functionality on a given platform (or set of platforms) by turning capabilities on or off.

However, one setback of this model is that it relies on services and licensing fees as the primary source of revenue generation. With the Internet breeding a generation of developers and consumers that expect things for free or nearly free, how do you ensure ROI? In addition, while the smartphone, cable, and utilities markets have matured to the point where providers can afford front-end revenue hits on hardware in lieu of lucrative service payouts over time, in the fledgling IoT it's hard to

rely on commitments to long- or even short-term commitments at the expense of a large upfront payday. Especially if you're a small IoT startup, asking a group of angel investors to risk bankrolling today's IoT devices in exchange for the uncertain promise of tomorrow's data- and software-driven dollars seems like a prayer.

This leaves IoT developers at a crossroads, as although the increasing amount of value and a more economic approach to electronic system design is now rooted in software, capitalizing on that value has largely been restricted to traditional, hardwarecentric ROI models (Figure 1).

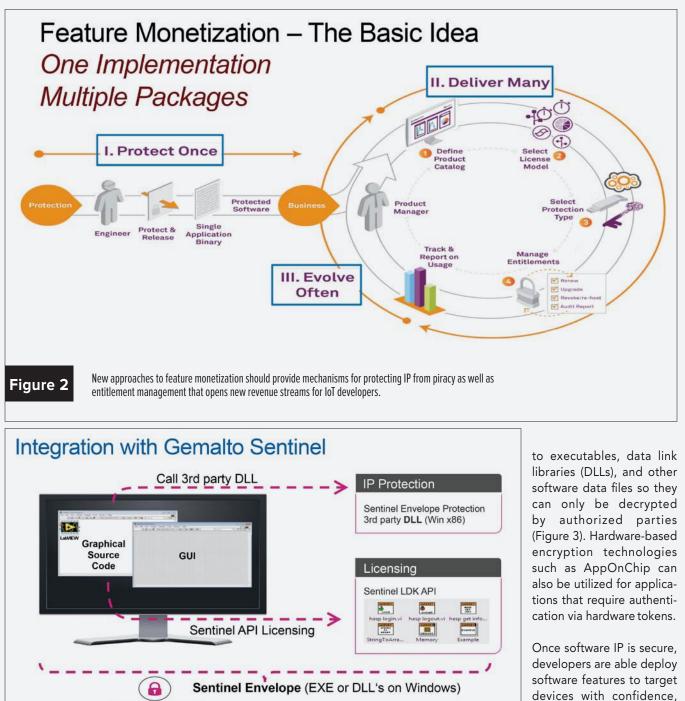

## Management and control are key to monetizing IoT

By its very nature, the IoT is based on the realtime or near-real-time delivery of software and services, so getting capabilities to the end user is not the issue. Rather, the problem is one of control and management – control that ensures IP can't be stolen or reverse engineered so potential users are able to take advantage of features for free, and management that facilitates the distribution of software and services in such a manner that data or feature utilization can be monitored for appropriate billing (Figure 2).

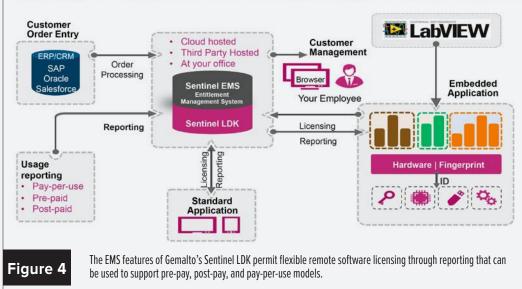

In a meeting with Aurelius Wosylus, Director of Business Development at Gemalto (www.gemalto.com) earlier this summer I was introduced to the company's Sentinel Licensing Development Kit (LDK) that addresses these challenges in multiple ways. From a security and IP protection perspective, the Sentinel LDK represents an evolution of Gemalto's licensing protection products into a single "Cross-Locking" technology suite that allows developers to implement a combination of hardware and/or software-based encryption. In software, keys are exchanged using the Sentinel Envelope, a wrapper that uses code obfuscation and system-level antidebugging, among additional features, to control access

Gemalto's Sentinel Envelope, part of the Sentinel LDK, provides an encryption wrapper around embedded software products to prevent tampering and theft of valuable IP.

**IP** Protection

enabled by the Entitlement

Management System (EMS)

built into the Sentinel LDK.

A web-based solution built on an SAP backend, the

Figure 3

#### Topology of Monetization of Features using Remote Activation

National Instruments' LabVIEW application.

With control and management technologies serving as the foundation, developers can take a new approach to product definition that reduces hardware dependency and enables innovative software packaging and licensing models, many of which can provide recurring revenue streams.

#### A pragmatic approach to the bottom line

In my travels around the

EMS allows software updates to be remotely pushed to target users and devices while also retrieving usage metrics that make flexible licensing models possible, including pay-per-use, prepay, and post pay. In addition, usage data can also provide insight into the behavior users exhibit when interacting with various products, which in turn can be leveraged for future R&D, marketing, and so on. Figure 4 shows an example software monetization architecture using the Sentinel LDK and embedded industry the general consensus is that while consumer IoT is currently driving about 80 percent of IoT's hype, the "enterprise/industrial IoT" will amount to 80 percent of its actual value. However, nebulous projections like this don't answer the core question of how IoT companies will survive, whatever the flavor. Software monetization strategies are a big step toward getting black figures on the bottom line sooner rather than later. **ECD**

# Microcontroller-based FPGAs hit the mark

By Ted Marena

FPGA vendors have been purposely pushing a growing divide in FPGA architectures. The main suppliers have gravitated to either SoC FPGAs with high-performance application processors or offer low-end FPGAs with no processor. Applications such as server farms and high-performance computing require ever-growing increases in performance. To address this, many SoC FPGAs are incorporating ARM A-class application processors, which are wellsuited for those applications. The reality for a multitude of other applications is that these processors are more than what is required. A-class SoC FPGAs are often too expensive, require too much software support burden because of the required operating system, and feature higher power consumption. Additionally, the raw compute performance is often not required.

On the other end of the spectrum, low-end FPGAs with no hard microcontroller or processor can be limiting for numerous designs. Low-end FPGAs only offer soft microcontrollers and there is no accompanying peripherals or subsystem. If peripherals are required then

they must be created by using FPGA gates. Low-end FPGAs with a soft microcontroller run very slow, are inefficient due to the FPGA gates needed to create the microcontroller and subsystem, offer no security, and are developed on proprietary architectures.

For a broad class of applications, a hardened microcontroller-based SoC FPGA is often the more effective solution. A large amount of 32-bit microcontroller architectures are produced each year because there are numerous applications that can use them. Imagine if there was a microcontroller with a common subsystem of components and it also included a configurable block that could implement hardware acceleration tasks or other logic functions? An ARM Cortex-M3 SoC FPGA can be viewed as a microcontroller with configurable hardware acceleration. The hardware acceleration and implementation of logic functions are two key features where the FPGA fabric excels. Combined, an ARM Cortex-M3 and an FPGA fabric allow an ideal division of labor for many tasks in a wide variety of applications.

#### Partitioning design examples with processor and FPGA fabric

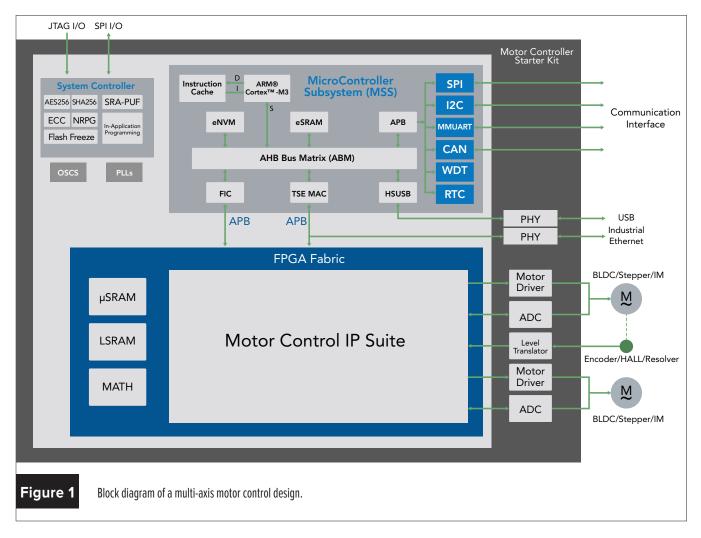

A microcontroller is ideal for slowerspeed serial tasks because of the architecture and requirement to access memory for instructions. An FPGA fabric is ideal for parallel-processed functions that are more time critical. When partitioning a design in this manner, it becomes clear which functions each component should implement. For example, one of the main challenges of controlling multiple motors is the requirement for a deterministic response of the motor control loops. To ensure a reliable design, each motor must be serviced within a tight, deterministic time with no wide timing variation. Because the multi-axis motor control algorithm is a time-critical function, it should reside in the FPGA fabric. The FPGA is ideal to implement the control loops with tight deterministic timing. Figure 1 is a block diagram of a multi-axis motor control design. The bulk of the motor control algorithm is in the FPGA fabric, while the slower speed interfaces are connected to the ARM Cortex-M3.

The motor control algorithm is not the only required function. Often one or more communications interface and control I/Os are required for a complete motor control design. These interfaces are not high-performance oriented and are ideal for a microcontroller such as the Cortex-M3 to implement. The communication interfaces could be CAN bus, SPI, UART, or other control buses.

#### Adding data security to a design

The addition of data security requires a certificate and key exchange, as well as implementing encryption and decryption algorithms on the data. There are multiple data security handshake exchanges and support for multiple formats is often required. The exchange handshake is typically not time-critical, but each exchange algorithm has different strings that need to be parsed, various verification protocols, and multiple rounds of certificate checking. With all of these procedures and the lack of time criticality, it is ideal to implement the certificate and key exchange in a microcontroller such as a Cortex-M3. The appropriate code can be called and executed depending on

the handshake exchange requested. Once the keys are exchanged and both devices are trusted, the data communication will need to be encrypted and decrypted. There are many wired and wireless communication speeds and protocols, and, depending on the link speed, performance is usually needed for the data encryption and decryption. When performance throughput is needed, it is recommended to implement it in the FPGA fabric. The transmitting device would implement an encryption algorithm such as AES 256, triple DES, RSA, or similar, and the receiving device would implement the same decryption algorithm. If the data link performance is not critical, the Cortex-M3 could implement the encryption and decryption. However, the FPGA fabric is ideally suited when higher throughput is needed.

## Adding custom peripherals to a design

Although processors and microcontrollers offer common peripherals, numerous designs require custom interfaces. Many medical, industrial, and embedded designs often need to

add additional interfaces, and open bus interface connectors address this issue. Two of the more popular peripheral bus connectors are the peripheral module (Pmod) and the Arduino shield. There are many peripheral designs that leverage these connectors and a SoC FPGA is ideal to bridge between these custom peripherals and the rest of the design. A microcontroller-based SoC FPGA can be uniquely leveraged when additional peripherals are required. The combination of the microcontroller and the FPGA fabric can implement bridging, acceleration functions, communication protocol management, I/O expansion, and control logic. One example is a design that needs to add a custom display. To interface to the display will require interface control logic, image manipulation and also register configurations. The ARM Cortex-M3 can address the latter and do other housekeeping tasks, while the FPGA is best suited for interfacing to the display and modifying the image as necessary.

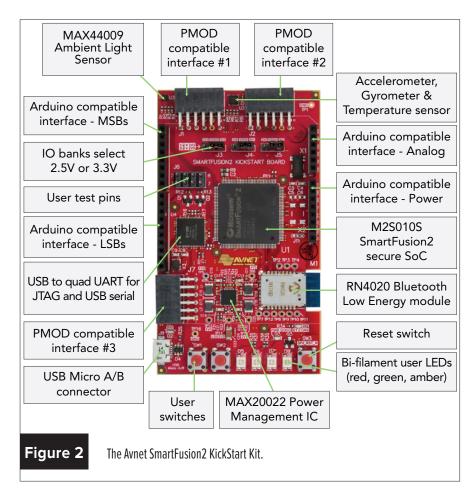

Avnet Electronics recently created a hardware kit to demonstrate the power that a microcontroller-based SoC can bring to the broad market (Figure 2). A number of peripheral options can be used with this board because it has both Pmod connectors and an Arduino shield connector set. Other key features include onboard peripherals, Bluetooth Low Energy (BLE), USB, and a host of sensors and switches. The board features the Microsemi SmartFusion2 SoC FPGA, which includes a hard ARM Cortex-M3 microcontroller and comprehensive subsystem. An HDL and C-code reference design, Windowsbased software GUI, and Android app are included with the architecture for added flexibility. The Windows GUI can interface to all of the onboard components, and the reference design examples enable the ability to add on an Arduino shield or Pmod peripherals. When connecting to an Android phone using the Windows GUI, a full data security demonstration can be seen. This data security design implements the key

exchange as well as encrypting the data between the SmartFusion2 FPGA and an Android smartphone.

There are a wide variety of general purpose applications that are ideally implemented in a microcontroller-based SoC FPGA that enables solutions such as bridging, I/O expansion, hardware acceleration, protocol management, and board initialization to be addressed. Using a hardware solution with a reference design and a software GUI allows design ideas to quickly become reality.

Ted Marena is Director of SoC/FPGA Products at Microsemi.

#### Microsemi

- www.microsemi.com

- @MicrosemiSoC

- in www.linkedin.com/company/ microsemi

- www.youtube.com/user/ MicrosemiCorp

# The theory behind product line engineering

By Curt Schwaderer, Editorial Director

cschwaderer@opensystemsmedia.com

At first glance, product development may seem like the most complex component of the product life cycle. However, everything developed from the silicon, circuit boards, and software have features, options, and derivatives that need to be identified, productized, and maintained. Managing the myriad of variations within a product line is often called product line engineering (PLE). In this column, we'll explore PLE in more detail and look at a company with a unique paradigm and solution for lowering complexity and increasing reliability within product lines.

In order to be competitive in today's environment, companies must deliver a product line, not just a single product with a mentality that "one size fits all."

## What is product line engineering?

In general, product line engineering (PLE) refers to the practice of creating an underlying architecture (both hardware and software) that describes the base platform. The architecture describes the base commonality across the product line as well as planned variations. PLE focuses on the process of engineering new products so it is possible to reuse product assets and flexibly apply a subset of variations for a specific product with minimal cost and time spent.

A Carnegie Mellon SEI study in 2003, among many others, has shown that PLE can have several benefits including higher productivity within the organization, higher quality products, faster timeto-market, and lower labor requirements.

## Challenges implementing efficient PLE

PLE is not something a "brute force" process can solve. For example, a rather simplistic embedded system with

a circuit board that can be purchased with two CPU options and software with three add-on features yields six possible product variations. With each feature addition, two additional product variations are created. Adding connectivity variations to this example creates an "M x N x O" variations problem. With each additional variable, the product variations can quickly grow out of control, causing duplication, increased development and test time, and even less reliable products.

There is significant complexity to managing all these variations. The example above was simple. Applying the same principles to autonomous vehicles that have a variety of options for radars, cameras, sensors, and electronic steering makes this a tremendous challenge.

#### The theory behind PLE

Systems and software PLE creates and maintains a portfolio of related products using a shared set of engineering assets and an efficient means of production.

I talked with Dr. Charles Krueger, CEO of BigLever Software (www.biglever.com) about their approach to PLE. Dr. Krueger says their PLE solutions take a "factory view" of the engineering process. "Think of an analogy of a factory," Dr. Krueger says. "Assembling and producing requirements and specifications is one dimension. Think about the things coming into the factory: the traditional artifacts like technical specifications, subsystem designed, bills of material, software, user documentation, calibration data, test cases, certifications... The list is long. We want to get really good at reusing these artifacts."

Dr. Krueger cites a familiar example of the user's manual in the glove box of an automobile.

"Open [the manual] up and it's full of things that say 'if you have this kind of option, do this; otherwise do that.'" Dr. Krueger says. "Most of the time I have no idea if that option is on my car. If PLE can customize the product [auto] down to the user's manual in the glove box so we don't have to guess at these if/then statements, things are cleaner and easier."

#### Two key abstractions

BigLever uses two key abstractions in their PLE solution: a feature catalog and a bill of features.

These abstractions are key to corporate success in managing the PLE process.

#### **SOFTWARE** Embedded Agile Development, Tools

The key to success here is, at a corporate level, everyone in the organization buys into the utilization and management of the feature catalog for a product line and a bill of features must exist for each unique product within the product line.

The feature catalog is a corporate-wide asset that lists the available features for the product line. Features describe things that are optional within the product family. Product managers can choose to include or exclude any feature in the feature catalog for a given product within the product family.

The "bill of features" is a description the product manager puts together that details exactly what features go into the making of a specific product within the product line.

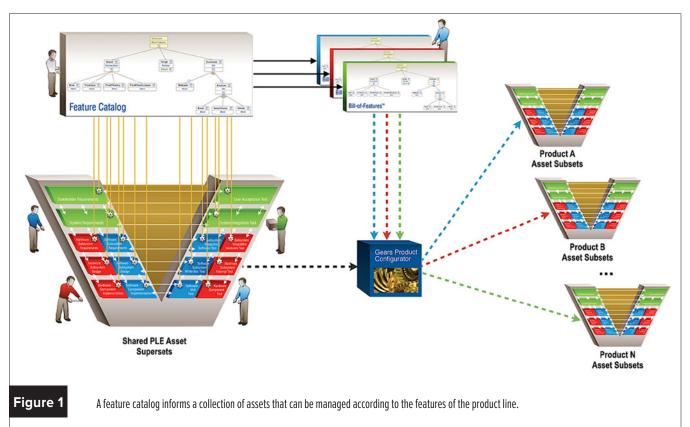

The BigLever "Gears product configurator" takes the bill of features description and takes the asset descriptions that come from the supply chain to output a specific product asset subset for a specific version of the product. This includes the product bill of materials, test cases, feature specifications, documentation, and anything else relevant to the included features for this specific product. The Gears configurator differentiates between assets needed for internal production and those that are included in the end product. For example, software source code and test cases are identified as assets needed to build the features included in the product, but only the executable binary and no test cases are included in the final product delivery.

## Applying factory point of view to PLE

Figure 1 illustrates the factory-based PLE approach as applied to the V-model product life cycle. The V-model demonstrates the relationships between each phase of the development cycle and its associated testing phase.

The diagram shows a feature catalog that informs a collection of assets that can be managed according to the features of the product line. These may be a long list of engineering artifacts – bill of materials, descriptions, software, system requirements, test cases, and wiring harness instructions are some of the common artifacts in an automotive product.

The feature descriptions go into the PLE process and are used to engineer the feature profiles that cause the products to come out. You'll notice in the diagram the comprehensive nature of the feature catalog as it feeds into both the development engineering and testing phases of the V-model.

In order to create a specific product, we need a way to filter all these assets. How do we know what to do within the configurator? This is where the bill of features specifications come in. If the feature list includes a feature, the configurator will include that in the assets, based on the bill of features. The configurator uses the bill of features to associate the pieces within the feature profiles to know what to include/exclude from the assets. This drives every engineer working on their part of the system to think about how their assets get used on all the variants

of these products within the family. Engineers become skilled at specifying these feature-based variations, and that results in efficiencies up and down the V-model.

"We want all the engineers to create features by accepting the single source of truth throughout the product family," Dr. Krueger says. "Anywhere there is variability the organization needs to make sure there is a single, common understanding of what the varying features are."

In order for the process to work, there must be an organizational view of PLE. Dr. Krueger mentions when they begin working with a company often, they are changing the fundamentals of how the organization does their engineering. The BigLever goal is to elevate the organization to this factory point of view. The new engineering mindset is they are creating artifacts that get put into the factory. But the training permeates across all disciplines of the organization in order to be effective.

The first level of decision involves the feature catalog – what features do the organization want to support? Orchestration between engineering, product management and executive management is critical here.

Once the feature catalog is set and the proper bill of features development is understood, engineers can be turned loose. The key concept here is to respect the feature catalog and develop accordingly. All experts are still doing their jobs, but they are doing so realizing there are different flavors defined by the feature catalog.

The second important discipline involves a portfolio team. This is the team that is deciding which specific features are to be included for a given product instance. These people are assembling according to the feature catalog and, in some cases, clustering by sub-families of these features.

The configurator operates on each of the bill of features and a unique V model pops out and pulls out the right assets automatically so every feature specified to be in the product will be included. Once this process has been followed, the automation of assembly and production enables additional efficiencies.

At the end of the day, the PLE process can bring an enormous increase in efficiencies, resulting in competitive advantage from the process itself in addition to the feature set.

#### PLE and Agile development

The V-model example may cause the impression that PLE is only applicable to the waterfall mode, but Dr. Krueger says that PLE is development-agnostic.

"Agile processes still have assets [definition of done, user stories, sprint reviews], and these assets can be handled in the same way within the factory view of PLE," Dr. Krueger says. "The development of each feature may be coming from a user story, but the asset result is the same."

## Real-world factory view PLE examples

The automotive market is finding a significant benefit with a factory view of PLE. General Motors faces one of the most complex PLE challenges in terms of product complexity, multiple options, and high reliability. They call this the "Mega-scale product line engineering" problem. GM produces on average one vehicle every three seconds somewhere around the world. Each one is considered a member or variant of one single big family of vehicles in the GM organization. They are adopting BigLever solutions to address the massive feature variants their product line entails.

In the military market, Lockheed Martin and Navy have adopted a "fix it once" initiative. They have 100 ships and it's possible that a defect might go out and be found on a single ship. Once found, there is a cycle to fix it. Later, this same defect may pop up on another ship and the same effort happens. PLE can facilitate a paradigm where you find it once, fix it once, then apply the fix across the entire product line that includes the feature with the defect. This is an extremely valuable part of the solution. The Lockheed Martin integrated weapons system is deployed in more than 100 ships. By managing a single "family of ships" with variants as defined by a bill of features, they can leverage the factory view of the PLE process. They reported a \$47M cost avoidance per year using the BigLever PLE solution and dramatically increasing the productivity by using the Gears approach.

Sound PLE also results in competitive advantage. Lockheed bought in and got good at this solution, and as a result their productivity has increased dramatically. By leveraging the efficiencies in the process, they can deploy projects at lower cost and deliver the same or a superior feature set. In addition, they have capacity to continue advancing and upgrading their capabilities.

In another example, General Dynamics teamed with BigLever to create the winning proposal for the U.S. Army Live Training Transformation "Consolidated Product Line Management." In this product line of training systems, each soldier has a personal area network connected to a larger network of up to 2,000 soldiers. This can be seen as an interesting Internet of Things (IoT) application. They are monitoring all these data points during maneuvers to detect patterns of activity of individuals and units that they can use as learning and training information to train soldiers on how to be effective and stay alive in the field. Using the BigLever PLE solution, the Army study produced audited numbers that project \$600M in cost avoidance over 15 years.

## What about small/medium businesses (SMBs)?

The examples cited were from very large organizations with big budgets, but Dr. Krueger claims the factory view of PLE can still be cost effective for start-ups and small businesses alike.

"The pricing scales by the number of people. And smaller organizations are typically faster to adopt the process because there is less to change and fewer existing blocks to overcome," Dr. Krueger says. "In SMB organizations, saving time for a few key people can make a world of difference in the organizations' growth potential."

# Look Ma, no code! PWM control in under five minutes with Microchip Curiosity development board

By Brandon Lewis, Assistant Managing Editor

**Goal:** The following describes how to build a simple PWM for motor control applications on the Microchip Curiosity Development Board using the MPLAB X Integrated Development Environment (IDE) and MPLAB Code Configurator (MCC) software. We begin with a basic bring up of Curiosity's onboard PIC16F1619 8-bit MCU running a "Hello, World!" program, and continue to set up a PWM using a Timer based on an FOSC/4 clock. All of this is done using the Microchip MCC without ever writing a single line of code.

#### Difficulty Level: Beginner

#### Hardware required:

- Microchip Curiosity Development Board (Outfitted with PIC16(L) F161X MCUs – Used here is the PIC16F1619)

- > USB 2.0 A-Male to Mini-B Cable

#### Software required:

- > Microchip MPLAB X IDE version 3.05 or later (Used here is MPLAB X IDE version 3.10; Download from www.microchip. com/pagehandler/en-us/family/ mplabx/)

- > MPLAB XC Compiler (Used here is MPLAB® XC8 Compiler version 1.35; Download from www.microchip. com/pagehandler/en-us/devtools/ mplabxc/home.html)

- > MPLAB Code Configurator version 2.25 plugin (Download

from www.microchip.com/ mymicrochip/filehandler. aspx?ddocname=en576270)

#### **Recommended platforms:**

- > Windows (x86/x64)

- > Linux 32-bit and Linux 64-bit (32-bit compatibility libraries required)

- Mac (Versions 10.X)

#### Support/documentation:

- > www.microchip.com/curiosity

- > www.microchip.com/support

#### Cost estimate:

- > Microchip Curiosity Development Board – \$20 (Before tax, shipping & handling. Available from multiple distributors and www. microchipdirect.com.)

- > USB 2.0 A-Male to Mini-B Cable \$5 (Rough estimate. Available from multiple distributors.)

## Powering the board and setting up a project

After downloading and installing the necessary software on your computer (installation instructions can be found at www.microchip.com/curiosity), plug the USB 2.0 Mini cable into the J2 connector located on the bottom of your Curiosity board. Doing so will illuminate the green LED D2 located near the center of the board to indicate that Curiosity is powered on, as well as LED D1 in the bottom left corner signifying that a +3.3V power supply is available on the board. If you haven't already, move the shunt jumper to the right two pins of the J12 jumper to connect a +5V power supply (the left two pins connect +3.3V).

You're now ready to program. Open the Microchip MPLAB X IDE from your applications folder, and click "New Project" in the upper left corner of the interface, or select it from the "File" dropdown menu. Doing so will open a "New Project" window.

From the Microchip Embedded folder, double click "Standalone Project." This will direct you to the next step in the project wizard, which prompts you to select a device. The Curiosity development board comes stock with the 8-bit PIC16F1619 microcontroller, so select it by either typing the model number into the "Device" dropdown, or by selecting "Mid-Range 8-bit MCUs (PIC10/12/16/ MCP)" in the "Family" field and then opening the Device dropdown and scrolling until you find the PIC16F1619. Hit "Next."

You'll be prompted to select a debug header, but you can leave that with its default settings, so click Next again.

In the next step of the Wizard, you'll be asked to select a tool, so navigate to "Curiosity – FN: XXXXXX" under the "Microchip Starter Kits" folder, and double click. This will generate a popup window that allows you to give

the board a human-friendly name. For the purposes of this exercise, just call it "Curiosity." Hit Next.

At this point we have to select a compiler. You should have already downloaded and installed Microchip's XC8 compiler, either the free or the Pro version. The Pro version offers some enhanced optimization features, and if you'd like to try it out Microchip offers a free 60-day trial. But for the purposes of this project, the free version will work just fine. Select the XC8 compiler from the "Compiler Toolchains" folder. Hit Next.

Now you're going to name your project. Call it CuriosityPWM. Leave all the default settings as they are, and click "Finish." A project folder should now appear in a column on the left of the MPLAB Xinterface.

Before getting started on the actual application, you have to configure the project to support low-voltage programming, which allows you to program the MCU without a 12 V power supply. To do this, simply right-click on your project, and select "Properties" from the subsequent dropdown. A popup window will appear that has a list of "Categories" on the left. Under the "Conf: [default]" parent, click "Starter Kit (PKOB)." The options on the right side of the window will change, revealing a dropdown next to the heading "Option categories:" Choose "Program Options" from that menu, and then check the box that says "Enable Low Voltage Programming." This may already be checked, but just highlight it anyway and click "Apply." Hit "OK."

#### Hello, World!

You're ready to roll, and can start by running a basic "Hello, World!" program just to make sure everything is working properly on the board. From the top navigation menu, go to Tools -> Embedded -> MPLAB Code Configurator. Several windows will populate to the right of the "Projects" section with project and device resources, a pin manager, and a main dashboard.

The first thing you'll want to do is make sure that low-voltage programming is also enabled on the MCU, and to do this just select "System Module" from the Project Resources window, navigate to the "Registers" tab that appears in the main dashboard, scroll down to "Register: CONFIG2," and change the LVP field from "Highvoltage on MCLR/VPP must be used for programming" to "Low-voltage programming enabled." Now, add a GPIO from the Device Resources window viewable under your project resources by finding "GPIO::GPIO" and double clicking it. This will add a GPIO to your project, and open the Pin Manager window on the far right. Open up the port for LED D7 that will run Hello, World! by closing the lock icon on the PIC16F1619's RC5 GPIO pin that controls that LED.

From here, select "GPIO Module" in the Project Resources window so we can configure LED D7 to illuminate when the application code is generated and flashed to Curiosity. When you have that selected, RC5 configuration options will appear in the PinManagerPaneViewer in the center dashboard, and here you will want to check the box labeled "Output" as we're going to be outputting to LED D7, as well as the "Start High" box to indicate that the pin should start running on high (Figure 1).

Now, hit "Generate" at the top of the main dashboard to generate the Hello, World! code. A popup will appear advising you that MCC hasn't detected a main.c file, and ask if you would like to generate one. Click Yes, then hit the "Make and Program Device" button (code box with downward arrow) in the MPLAB X top toolbar. The code will load

### **SOFTWARE** Embedded Agile Development, Tools

| 2                        | 9 📔 🞴 😼 🖬 🤊    | default : 🚏 - 👸 -                  | › · 💁 · 💁 · 🦓 🚯 · 🦓 🖾 🗵 👂                                                              | PC: 0x0 z dc c : W:0x0 : bank 0       | How do I? Keyword(s)                                              | Q= Search (3t +1) |

|--------------------------|----------------|------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------|-------------------|

| 0                        | Projects ①     | MPLABB Code Configurator Resources | Start Page 💿 💽 Naxigator 💿 MPLAB® Code Configurator                                    |                                       | MPLAB® Code Configurator Pin Manager                              | (a)               |

| -                        | CuriosityPWM_1 | Project Resources                  |                                                                                        |                                       |                                                                   |                   |

| ž                        |                | System                             | Generate Code (2)                                                                      | << Resources Pin Manager >>           |                                                                   |                   |

|                          |                | 🖈 GPIO::GPIO 💌                     | 0                                                                                      |                                       |                                                                   |                   |

| ~                        |                |                                    | Selected pins: 1                                                                       |                                       |                                                                   |                   |

| vice                     |                |                                    |                                                                                        | RC5                                   | VDD 1 • 20 V55<br>RAS 2 19 RAD                                    |                   |

| Ser                      |                |                                    |                                                                                        |                                       | RA4 3 18 RA1                                                      |                   |

| 🕄 Classes 🗐 Services 🕞 I |                |                                    | 2                                                                                      |                                       | MCLR 4 17 RA2<br>10_RCS 5 16 RC0                                  |                   |

| 2                        |                |                                    | <b>(()</b>                                                                             |                                       | RC4 6 Mccoccan 15 RC1                                             |                   |

| Iass                     |                |                                    | 0                                                                                      |                                       | RC3 7 PIC16F1619 14 RC2<br>RC6 8 13 RB4                           |                   |

| š                        |                |                                    |                                                                                        |                                       | RC7 9 12 R85<br>R87 10 11 R86                                     |                   |

|                          |                |                                    |                                                                                        |                                       | RB7 10 11 RB6                                                     |                   |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                |                                    |                                                                                        |                                       | ** ·                                                              |                   |

|                          |                |                                    |                                                                                        |                                       | Package PDIP20 \$ Reverse Pin Order                               |                   |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                |                                    |                                                                                        |                                       | 19 18 17 4 3 2 13 12 11 10 16 15 14 7 6 5<br>PORTA▼ PORTB▼ PORTC▼ | 8 9               |

|                          |                |                                    |                                                                                        |                                       | Mcdule Function 0 1 2 3 4 5 4 5 6 7 0 1 2 3 4 5                   | 6 7               |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                | Q Search for modules               |                                                                                        |                                       |                                                                   |                   |

|                          |                | > 🐴 ADC                            |                                                                                        |                                       |                                                                   |                   |

|                          |                | ▶ 🔘 AT                             |                                                                                        |                                       |                                                                   |                   |

|                          |                | ▶ 🗠 CCP                            |                                                                                        |                                       |                                                                   |                   |

|                          |                | > > cuc                            |                                                                                        |                                       |                                                                   |                   |

|                          |                | ▶ 🕗 CRC<br>▶ 🖧 CWG                 |                                                                                        |                                       |                                                                   |                   |

|                          |                | ► In Comparator                    |                                                                                        |                                       |                                                                   |                   |

|                          |                | 🕨 🥓 DAC                            | Output - MPLAB® Code Configurator                                                      |                                       |                                                                   | 6                 |

|                          |                | ▶ 🙁 EUSART<br>▶ 🦟 FVR              | Number of files to be generated: 6                                                     |                                       |                                                                   |                   |

|                          |                | ► & MSSP                           |                                                                                        |                                       |                                                                   |                   |

|                          |                | Math Accelerator                   | Checking for "drv_" files in module: PWM3<br>Code for PWM3 was successfully generated  |                                       |                                                                   |                   |

|                          |                | ► 🔲 Memory                         | Checking for "drv_" files in module: TMR2                                              |                                       |                                                                   |                   |

|                          |                | * A PWM                            | Code for TMR2 was successfully generated                                               |                                       |                                                                   |                   |

|                          |                | PWM3::PWM<br>PWM4::PWM             | Code for System was successfully generate                                              | a                                     |                                                                   |                   |

|                          |                | ▶ O SMT                            | ******* Generation ended ********                                                      |                                       |                                                                   |                   |

|                          |                | ▼ ⊙ Timer                          |                                                                                        |                                       |                                                                   |                   |

|                          |                | TMR0::Timer                        | Interrupt Manager: Please remember to ena<br>Interrupt Manager: Please remember to ena |                                       |                                                                   |                   |

|                          |                | TMR1::Timer                        |                                                                                        | the the templeter and otopat interrup |                                                                   |                   |

|                          |                | N                                  |                                                                                        |                                       |                                                                   | 1                 |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

|                          |                |                                    |                                                                                        |                                       |                                                                   |                   |

Figure 1

After adding the RC5 GPIO pin to your project, select "Output" and "Start High" to configure LED D7 to run the "Hello, World" application.

| * * * * *           | default : 🚏 - 👸 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ) + 💁 + 🏪 + 🍇 🏭 + 🖣 🌆 🔽 📝 🛞 PC: 0x0 z dc c : W:0x0 : bank 0 🛒 How do IP (cyaerdis)                               | (Q~ Search (೫+1) |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------|

| Projects O          | MPLAB® Code Configurator Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Start Page 🗈 🚫 Navigator 🗈 MPLABS Code Configurator 💿                                                            |                  |

| " >  CuriosityPWM_1 | Project Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                  |                  |

| 10                  | System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Generate Code (2) << Resources Pin Manager >>                                                                    |                  |