# ML9636GDZ45A User's Manual

Issue Date: January 10, 2008

#### **NOTICE**

- The information contained herein can change without notice owing to product and/or technical improvements. Before using the

product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. OKI assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not, unless specifically authorized by OKI, authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans.

- Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2008 Oki Electric Industry Co., Ltd.

# Preface

The ML9636GDZ45A User's Manual consists of the following two documents:

ML9636GDZ45A User's Manual FEUL9636-01

A Separate Volume for the ML9636 User's Manual Command Details FEUL9636CMD-01

This user's manual describes the operation of the ML9636.

# **Notation**

| Classification  | Notation                                                                                                                     | Description                                                                                                                                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Numeric value | 0xnn                                                                                                                         | Indicates a hexadecimal number.                                                                                                                                                                                      |

| • Address       | 0xnnnn_nnnn                                                                                                                  | Indicates a hexadecimal number (represents 0xnnnnnnnn).                                                                                                                                                              |

| • Unit          | word, WORD<br>byte, BYTE<br>mega-, M<br>kilo-, K<br>kilo-, k<br>milli-, m<br>micro-, µ<br>nano-, n<br>second, s (lower case) | 1 word = 32 bits<br>1 byte = 8 bits<br>$10^6$<br>$2^{10} = 1024$<br>$10^3 = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second                                                                                   |

| • Terminology   | "H" level                                                                                                                    | Indicates high voltage signal levels $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics. Indicates low voltage signal levels $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics. |

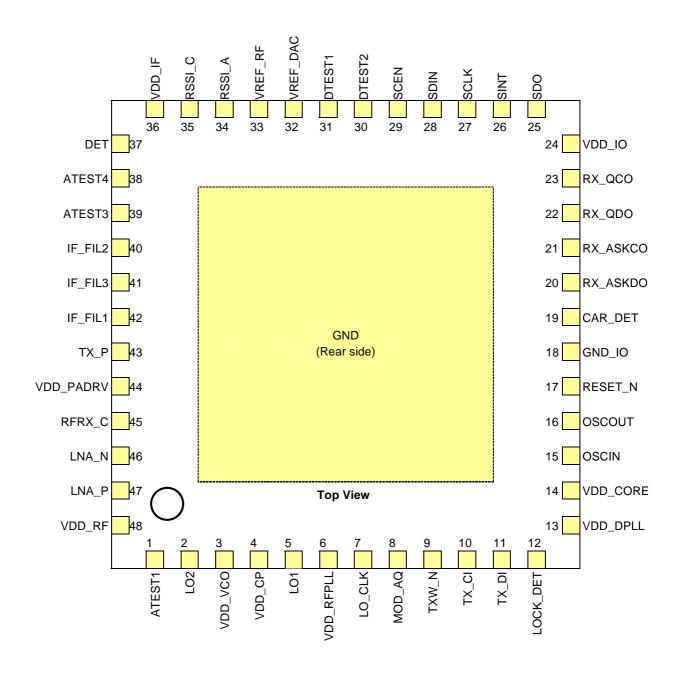

## • Register description

Read/write attribute: R indicates a readable bit and W indicates a writable bit.

MSB: Most significant bit of the 8-bit register (memory)

LSB: Least significant bit of the 8-bit register (memory)

# Table of Contents

| Preface    |                                                    | i        |

|------------|----------------------------------------------------|----------|

| 1.         | Overview                                           | 1        |

| 1.1        | Features                                           | 1        |

| 1.2        | Block Diagram                                      | 2        |

| 1.3        | Pins                                               | 4        |

| 1.3        | .1 Pin Configuration                               | 4        |

| 1.3        | .2 Pin Descriptions                                | 5        |

| 1.3        | •                                                  |          |

| 1.3        | .4 Handling of Unused Pins                         | 11       |

| 2. N       | MODEM Function                                     |          |

| 2.1        | DEMOD Interface (RX) Function                      |          |

| 2.1        | ·                                                  |          |

| 2.1        | ·                                                  |          |

| 2.2        | MODEM Interface (TX) Function                      |          |

| 2.3        | Test Signal Generation Test Function               |          |

|            | Synchronous Communication Interface (SCI) Function |          |

| 3.1        | Clock Timing                                       |          |

| 3.2        | Data Format                                        |          |

| 3.2        |                                                    |          |

| 3.2        |                                                    |          |

| 3.2        |                                                    |          |

| 3.2        |                                                    |          |

| 3.3        | Setting Write Data                                 |          |

| 3.4        | Reading Set Data                                   |          |

|            | List of Commands                                   |          |

|            | Electrical Characteristics                         |          |

| 5.1        | Absolute Maximum Ratings                           |          |

| 5.2        | Recommended Operating Conditions                   |          |

| 5.3        | DC Characteristics                                 |          |

| 5.4        | AC Characteristics                                 |          |

| 5.4        |                                                    |          |

| 5.4<br>5.4 |                                                    |          |

|            | Package Dimensions                                 |          |

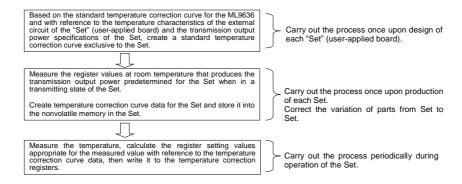

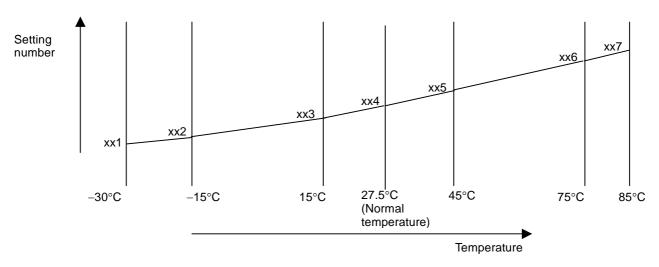

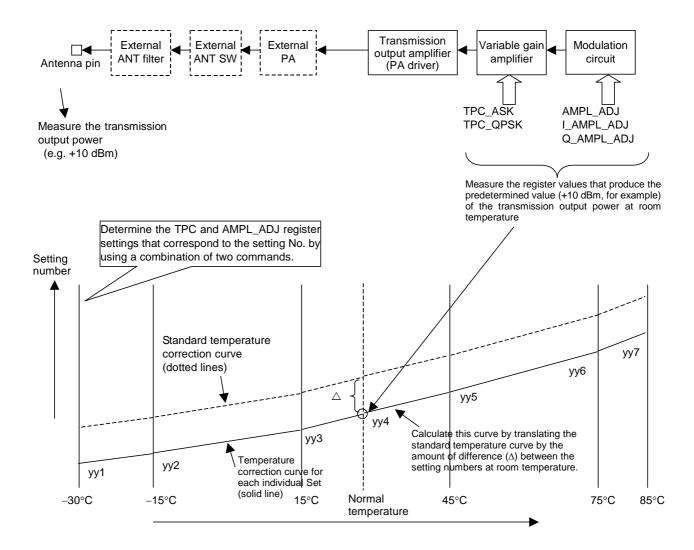

| 7. T       | Temperature Correction for RF Characteristics      | 41<br>19 |

| 7.1        | Transmission Characteristics                       |          |

| 7.1        |                                                    |          |

| 7.1        |                                                    |          |

|            | IPL_ADJ Register)                                  |          |

| 7.1        |                                                    |          |

| 7.1        | •                                                  |          |

| 7.1        |                                                    | 50<br>51 |

| 7.1        | Reception Characteristics                          |          |

| 7.2        | •                                                  |          |

| 7.2        |                                                    |          |

| 7.2        |                                                    |          |

| 7.2        | -                                                  | 53<br>54 |

| 7.2<br>7.2 |                                                    |          |

|            |                                                    |          |

|            | lixes                                              |          |

| A.         | SCI Timing Specifications (Reference Values)       |          |

| A.1        | 6 · · · · · · · · · · · · · · · · · · ·            |          |

| A.2        | ·                                                  |          |

| В.         | Example of Setting Transmit Timing                 |          |

| B.1        | Example of Setting QPSK Transmit Timing            | 58       |

| B.2 Example of Setting ASK Transmit Timing                                             | 59   |

|----------------------------------------------------------------------------------------|------|

| C. RF Burst Receive Timing (Reference Values)                                          | 61   |

| E. Example of External Circuit                                                         | 62   |

| F. Example of Improving the demodulation tracking characteristics with respect to a su | dden |

| change in the bottom level of a input modulation signal                                |      |

| G. Notes on Hardware Design                                                            |      |

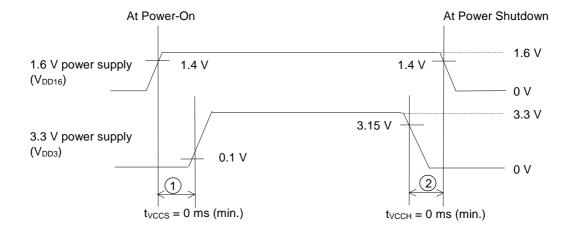

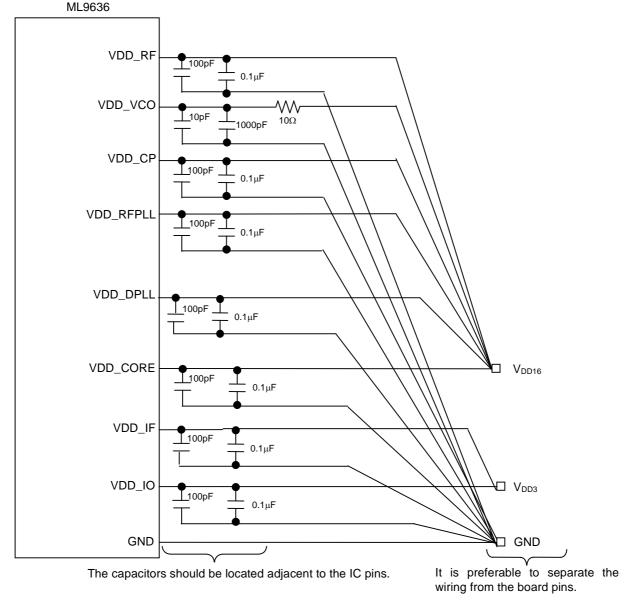

| G.1 When Designing Power Supplies                                                      |      |

| G.1.1 Power-On Sequence                                                                |      |

| G.1.2 Bypass Capacitor Insertion                                                       |      |

| G.1.2.1 Example of Bypass Capacitor Insertion                                          |      |

| G.1.2.2 Notes on Inserting Bypass Capacitors                                           |      |

| G.1.2.3 Notes on Power Supply Voltages                                                 | 65   |

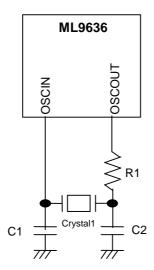

| G.2 When Configuring Oscillation Circuits                                              |      |

| G.2.1 When Using a Crystal Oscillation Circuit                                         |      |

| G.2.1.1 Example of Crystal Oscillation Circuit Configuration                           |      |

| G.2.1.2 Notes on Configuring a Crystal Oscillation Circuit                             |      |

| G.2.1.3 Examples of Applicable Crystal Resonators                                      |      |

| G.2.2 When Configuring an External Clock as the Input to an Oscillation Circuit        |      |

| G.2.2.1 Example of Configuring an External Oscillation Circuit                         |      |

| G.2.2.2 Notes on Configuring an External Crystal Oscillation Circuit                   |      |

| G.3 On Designing a High-Frequency Circuit                                              |      |

| G.3.1 General Notes                                                                    |      |

| G.3.2 High-Frequency Circuit Design                                                    |      |

| H. Register Setting Procedure                                                          |      |

| H.1 Example of Activation Procedure at Power-On                                        |      |

| H.2 Example of Procedure at Power Shutdown                                             |      |

| H.3 Example of Procedure (for Frequency Selection) during Operation                    |      |

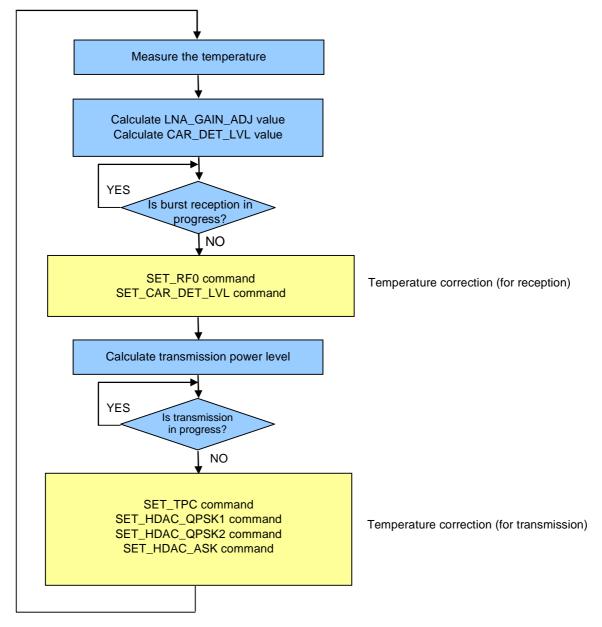

| H.4 Example of Procedure (for Temperature Correction) during Operation                 |      |

| Revision History                                                                       | 72   |

## 1. Overview

The ML9636GDZB5A (Called ML9636 in following) conforms to ARIB STD-T75 (dedicated short-range communications (DSRC) system standard) version 1.3. It is an IC whose RF and MODEM sections are integrated into a single chip and can be used for 5.8 GHz ASK/QPSK DSRC communication. The IC can be applied to DSRC systems in combination with a baseband LSI for DSRC.

#### 1.1 Features

- Conforms to ARIB STD-T75 (dedicated short-range communications (DSRC) system standard) version 1.3.

- Includes receive and transmit circuits, a synthesizer, and a digital modulation and demodulation circuit.

- The digital circuit also includes a split phase coding and decoding circuit in ASK mode. However this is only for the split phase code of 1024kbps. (Manchester code)

- The interface with a base-band is for digital signals and low-speed analog signals (RSSI) only

- Radio frequency range

Downlink

D7 5775 MHz, D6 5780 MHz, D5 5785 MHz, D4 5790 MHz,

D1 5795 MHz, D3 5800 MHz, D2 5805 MHz

Uplink

U7 5815 MHz, U6 5820 MHz, U5 5825 MHz, U4 5830 MHz,

U1 5835 MHz, U3 5840 MHz, U2 5845 MHz

• Data transfer speed

In ASK mode: 1024 kbps In QPSK mode: 4096 kbps

• Supply voltage

I/O section VDDIO: 3.3 V Typ. 3.15 V Min. 3.45 V Max. CORE and RF sections VDDCORE:1.6 V Typ. 1.5 V Min. 1.65 V Max.

• Supply current

During reception: 115 mA (Max.)

During transmission: 95 mA (Max.: When -7 dBm is transmitted from the TX\_P pin)

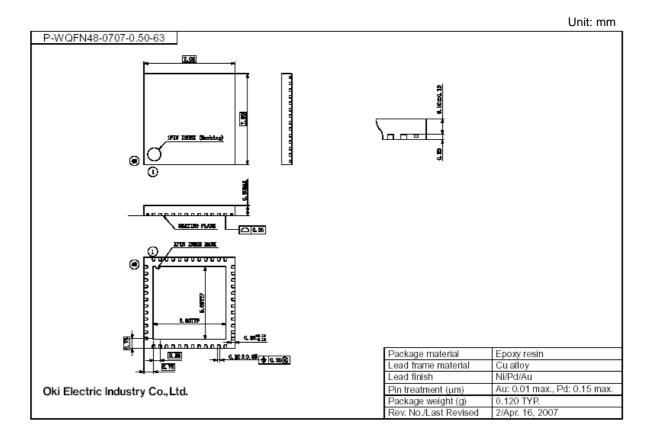

• Package

48-pin WQFN P-WQFN48-0707-0.50-63

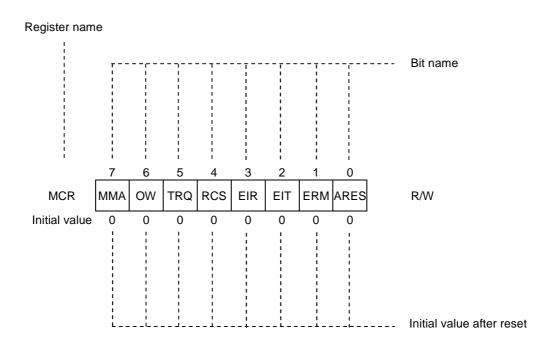

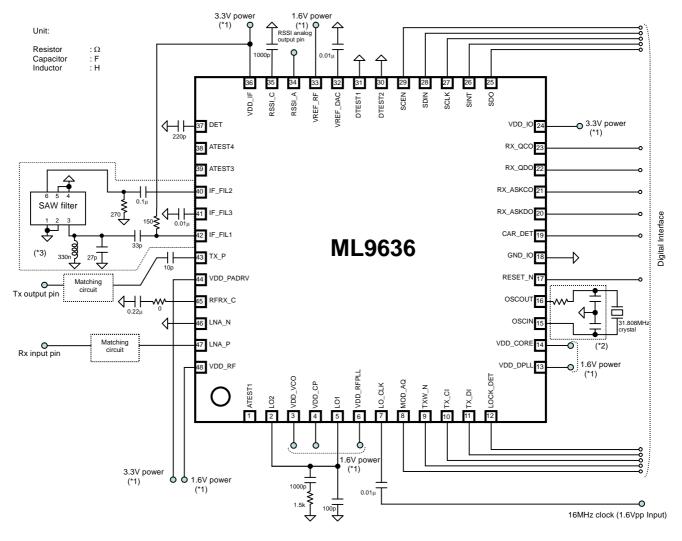

## 1.2 Block Diagram

Figure 1-1 shows a block diagram of this IC. Table 1-1 shows a functional summary of each block.

Figure 1-1 Block Diagram of ML9636

Table 1-1 Functional Summary of Each Block

| Block             | Function                                                             |

|-------------------|----------------------------------------------------------------------|

| LNA               | Low noise amplifier                                                  |

| RX 1st Mix        | 1st receive mixer                                                    |

| IF Amp            | Intermediate frequency amplifier                                     |

| RX 2nd Mix        | 2nd receive mixer                                                    |

| OSC               | Oscillator for 2nd mixer (31.808 MHz)                                |

| AM Det RSSI       | Amplitude detect / RSSI carrier detect                               |

| LO                | Local oscillator                                                     |

| VGA               | Variable gain amplifier                                              |

| ASK/QPSK Mod      | ASK/QPSK modulation                                                  |

| LPF               | Low-pass filter                                                      |

| I/Q DAC           | Digital to analog conversion for I/Q                                 |

| QPSK Demod        | QPSK digital demodulation                                            |

| ASK Demod         | A decoding for split phase of 1024kbps and a clock recovery for ASK  |

| D-Mod             | Digital modulation (includes split phase coding of 1024kbps for ASK) |

| Logic section PLL | PLL for the logic section (generates the clock based on 4M CLK)      |

| SCI               | Serial interface used to configure settings for registers            |

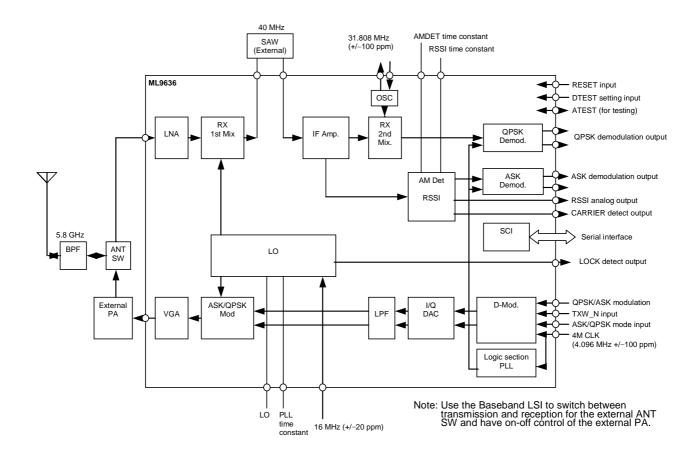

## 1.3 Pins

#### 1.3.1 Pin Configuration

#### 48-Pin WQFN (Top View)

Figure 1-2 Pin Configuration of ML9636

Note: The exposed die attach pad must be connected to a solid ground plane as this is the ground connection for the chip.

<sup>\*</sup> The actual pads are not visible since this pin configuration shows the top view.

# 1.3.2 Pin Descriptions

| Pin                                                    | Symbol                             | I/O (*1)        | Description                                                       | State    | Active |

|--------------------------------------------------------|------------------------------------|-----------------|-------------------------------------------------------------------|----------|--------|

| RF re                                                  | RF related pins   at reset   level |                 |                                                                   | ievei    |        |

| 47                                                     | LNA_P                              | I               | Possivo antonna input sia P                                       |          |        |

|                                                        | <u> </u>                           | I <sub>RF</sub> | Receive antenna input pin P                                       |          | _      |

| 46                                                     | LNA_N                              | I <sub>RF</sub> | Receive antenna input pin N                                       |          |        |

| 43                                                     | TX_P                               | O <sub>RF</sub> | Output pin P to transmit PA                                       |          | _      |

| 42                                                     | IF_FIL1                            | O <sub>A</sub>  | Output pin for the external 40 MHz filter                         |          |        |

| 40                                                     | IF_FIL2                            | I <sub>A</sub>  | Input pin for the external 40 MHz filter                          |          | _      |

| 41                                                     | IF_FIL3                            | I <sub>A</sub>  | Connection pin for the external 40 MHz filter                     |          |        |

| 45                                                     | RFRX_C                             |                 | Connection pin for the external capacitor for RF                  | _        | _      |

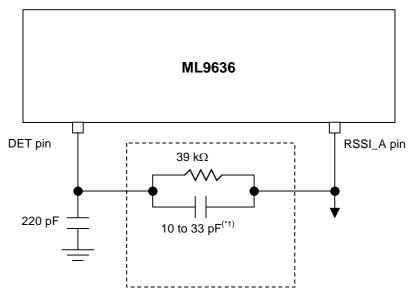

| 37                                                     | DET                                |                 | Connection pin for the external capacitor (for ASK demodulation)  | _        | _      |

| 35                                                     | RSSI_C                             | _               | Connection pin for the external capacitor (for RSSI integration)  | _        |        |

| 5                                                      | LO1                                |                 | Connection pin for the external capacitor and resistor (for PLL)  | _        | _      |

| 2                                                      | LO2                                |                 | Connection pin for the external capacitor and resistor (for PLL)  | _        |        |

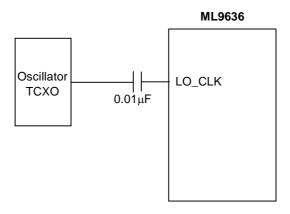

| 7                                                      | LO_CLK                             | I <sub>A</sub>  | 16 MHz input pin for LO (*2)                                      | _        | _      |

|                                                        |                                    |                 | Reference pin for DAC                                             |          |        |

| 32                                                     | VREF_DAC                           | _               | (connected to GND via a 0.01 μF capacitor)                        | _        |        |

| 33                                                     | VREF_RF                            |                 | Reference pin for RF (connected to the 1.6 V supply)              |          | _      |

|                                                        | EM interface (F                    | (X) related     |                                                                   |          |        |

| 20                                                     | RX_ASKDO                           | O O             | RX ASK split phase demodulation data output pin                   | L        |        |

|                                                        |                                    |                 |                                                                   |          | _      |

| 21                                                     | RX_ASKCO                           | 0               | Clock output pin for RX ASK (1.024 MHz)                           | <u>L</u> | _      |

| 22                                                     | RX_QDO                             | 0               | RX QPSK data output pin                                           | <u>L</u> | _      |

| 23                                                     | RX_QCO                             | 0               | Clock output pin for RX QPSK (equivalent to 4.096 MHz)            | L        |        |

| 19                                                     | CAR_DET                            | 0               | Carrier detect output pin H: Detect                               |          | Н      |

| 34                                                     | RSSI_A                             | $O_A$           | RSSI analog output pin                                            |          | _      |

| MODEM interface (TX) related pins                      |                                    |                 |                                                                   |          |        |

| 11                                                     | TX_DI                              | I               | TX data input pin                                                 |          |        |

| 10                                                     | TV CI                              | TV CI           | TX clock input pin (4.096 MHz)                                    |          |        |

| 10                                                     | 0 TX_CI I                          |                 | Digital reference clock (*3)                                      |          | _      |

| 9                                                      | TXW_N                              | I               | Input pin for output timing control L: Transmission, H: Reception |          |        |

| 8                                                      | MOD_AQ                             | I               | Input pin for ASK/QPSK output switching H: ASK, L: QPSK           | _        | _      |

| Synchronous communication interface (SCI) related pins |                                    |                 |                                                                   |          |        |

|                                                        |                                    |                 | Synchronous communication interface                               |          |        |

| 28                                                     | SDIN                               | I               | Data input pin                                                    | _        | _      |

|                                                        |                                    |                 | Synchronous communication interface                               |          |        |

| 25                                                     | SDO                                | 0               | Data output pin                                                   | L        | _      |

|                                                        |                                    |                 | Synchronous communication interface                               |          |        |

| 27                                                     | SCLK                               | I               | Clock input pin                                                   | _        | _      |

|                                                        |                                    |                 | Synchronous communication interface                               |          |        |

| 26                                                     | SINT                               | 0               | Interrupt output pin                                              | Н        | L      |

|                                                        |                                    |                 |                                                                   |          |        |

| 29                                                     | SCEN                               | I               | Synchronous communication interface                               | _        | L      |

|                                                        |                                    |                 | Chip enable pin                                                   |          |        |

| _                                                      | em control pins                    |                 | I.u                                                               |          |        |

| 17                                                     | RESET_N                            | 1               | Hardware reset pin                                                |          | L      |

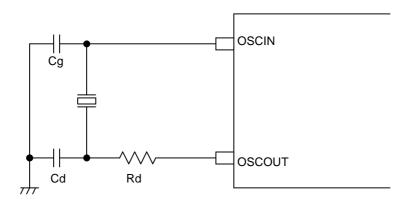

| 15                                                     | OSCIN                              | Ios             | 31.808 MHz crystal connection pin 1                               | _        | _      |

|                                                        | 200                                | -03             | External clock input pin                                          |          |        |

|                                                        |                                    |                 | 31.808 MHz crystal connection pin 2                               |          |        |

| 16                                                     | OSCOUT                             | Oos             | Leave this pin open when OSCIN is used as an external clock input | _        | _      |

|                                                        |                                    |                 | pin.                                                              |          |        |

| 12                                                     | LOCK_DET                           | 0               | PLL LOCK detecting output pin H: Lock, L: Unlock                  | _        | Н      |

| Pin  | Symbol                          | I/O (*1)                         | Description                                                               | State at reset | Active<br>level |

|------|---------------------------------|----------------------------------|---------------------------------------------------------------------------|----------------|-----------------|

| Cont | rol pins for testi              | ng                               |                                                                           |                |                 |

| 31   | DTEST1                          | I <sub>D</sub>                   | Test mode setting pin 1. Fix to "L."                                      | _              | _               |

| 30   | DTEST2                          | I <sub>D</sub>                   | Test mode setting pin 2. Fix to "L."                                      | _              | _               |

| 1    | ATEST1                          | I <sub>RF</sub> /O <sub>RF</sub> | RF circuit test pin                                                       | Hi-Z           |                 |

| 39   | ATEST3                          | I <sub>A</sub> /O <sub>A</sub>   | IF and analog circuits test air                                           | Hi-Z           | _               |

| 38   | ATEST4                          | I <sub>A</sub> /O <sub>A</sub>   | IF and analog circuits test pin                                           | Hi-Z           |                 |

| Powe | er supply pins (*               | ·4)                              |                                                                           |                |                 |

| 48   | VDD_RF                          |                                  | Power supply pin for LNA and DET (1.6 V typ.)                             |                |                 |

| 6    | VDD_RFPLL                       | _                                | Power supply pin for RF PLL (1.6 V typ.)                                  |                |                 |

| 3    | VDD_VCO                         | _                                | Power supply pin for RF VCO (1.6 V typ.)                                  |                | _               |

| 4    | VDD_CP                          | _                                | Power supply pin for RF CP (1.6 V typ.)                                   |                | _               |

| 36   | VDD_IF                          |                                  | Power supply pin for IF and MOD (3.3 V typ.)                              |                |                 |

| 44   | VDD_PADRV                       |                                  | Power supply pin for PA drivers (3.3 V typ.)                              |                |                 |

| 13   | VDD_DPLL                        | _                                | Power supply pin for digital PLL (1.6 V typ.)                             |                | _               |

| 14   | VDD_CORE                        | _                                | Power supply pin for digital CORE (1.6 V typ.)                            |                |                 |

| 24   | VDD_IO                          | _                                | Power supply pin for digital IO (3.3 V typ.)                              |                | _               |

| 18   | GND_IO                          |                                  | Ground pin for digital IO                                                 |                |                 |

| Grou | Ground on the package rear side |                                  |                                                                           |                |                 |

| _    | GND                             | _                                | Ground for the analog section and digital core section (on the rear side) | _              | _               |

#### \*1 I/O definition

I<sub>RF</sub> : RF input pin

I<sub>A</sub> : Analog input pin

I : Digital input pin

$\begin{array}{lll} I_D & : & Pulled-down \ digital \ input \ pin \\ I_{OS} & : & Oscillator \ circuit \ input \ pin \\ O_{RF} & : & RF \ control \ output \ pin \\ O_A & : & Analog \ output \ pin \\ O & : & Digital \ output \ pin \end{array}$

Oos : Oscillator circuit output pin

- \*2 Do not stop the 16 MHz input while the ML9636 is operating.

- \*3 Since TX\_CI serves as the reference clock of the digital circuits, do not stop it all the time.

- \*4 The 3.3 V supply should be used for VDD\_IO, VDD\_IF, and VDD\_PADRV and the 1.6 V supply for VDD\_RF, VDD\_VCO, VDD\_CP, VDD\_RFPLL, VDD\_DPLL, and VDD\_CORE.

Never leave the power supply pins or the GND pins open.

The exposed die attach pad must be connected to a solid ground plane as this is the ground connection for the chip.

## 1.3.3 Pin Structure

Tables 1-2, 1-3, 1-4, and 1-5 show the simplified pin structures that this IC has.

Table 1-2 Pin Structure (1 of 4)

| Type                                        | Symbol                                                                                                                                  | Pin structure                                   |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Input pin/Output pin                        | RX_ASKDO, RX_ASKCO,<br>RX_QDO, RX_QCO,<br>CAR_DET, TX_DI, TX_CI,<br>TXW_N, MOD_AQ, RESET_N,<br>LOCK_DET, SDIN, SDO,<br>SCLK, SINT, SCEN | Output signal Output enable signal Input signal |

|                                             |                                                                                                                                         | Input/output pin                                |

| Input/output pin with<br>pull-down resistor | DTEST1, DTEST2                                                                                                                          | Output signal Output enable signal Input signal |

|                                             | OSCIN, OSCOUT                                                                                                                           | Input/output pin with pull-down resistor        |

| Oscillator pin                              | 33011, 000001                                                                                                                           | Oscillator circuit buffer cell                  |

|                                             |                                                                                                                                         | Oscillator pins                                 |

<sup>\*</sup> The input protection circuits are not shown in the figures above.

Pin structure Туре Symbol LNA\_P, LNA\_N LNA\_P □-5.8GHz band Amplifier RF pin LNA\_N □  $\eta \eta$ TX\_P RF pin 5.8GHz ba -□ TX\_P IF\_FIL1 40MHZ - IF\_FIL1 amplifier Analog pin IF\_FIL2, IF\_FIL3 IF\_FIL2 □ 40MHz Analog pin IF\_FIL3 □-Bias voltage eneration circuit DET ASK demodulation Analog pin circuit —□ DET

Table 1-3 Pin Structure (2 of 4)

<sup>\*</sup> The input protection circuits are not shown in the figures above.

Symbol Pin structure Туре RSSI\_C RSSI signal Processing circuit Analog pin -□ RSSI\_C LO1 Charge pump Analog pin \_\_ LO1 LO2 VCO Analog pin LO2 🗆 LO\_CLK LO PLL Analog pin LO\_CLK \_\_\_ VREF\_DAC DAC Reference pin VREF\_DAC ☐—

Table 1-4 Pin Structure (3 of 4)

<sup>\*</sup> The input protection circuits are not shown in the figures above.

Type Symbol Pin structure

VREF\_RF

VREF\_RF

VREF\_RF

RF control circuit

RSSI output amplifier circuit

RFRX\_C

Mixer circuit

RFRX\_C

Table 1-5 Pin Structure (4 of 4)

<sup>\*</sup> The input protection circuits are not shown in the figures above.

## 1.3.4 Handling of Unused Pins

Table 1-6 shows how unused pins of this IC should be handled. Be sure to connect the other input pins than shown below to appropriate signal lines according to their use.

Table 1-6 Handling of Unused Pins

| Pin    | If unused, connect to: |

|--------|------------------------|

| DTEST1 | GND                    |

| DTEST2 | GND                    |

| ATEST1 | Open                   |

| ATEST3 | Open                   |

| ATEST4 | Open                   |

#### Notes:

- When left open, a digital input pin may carry an excessive supply current.

- Never leave power supply pins or GND pins open.

The exposed die attach pad must be connected to a solid ground plane as this is the ground connection for the chip.

#### 2. MODEM Function

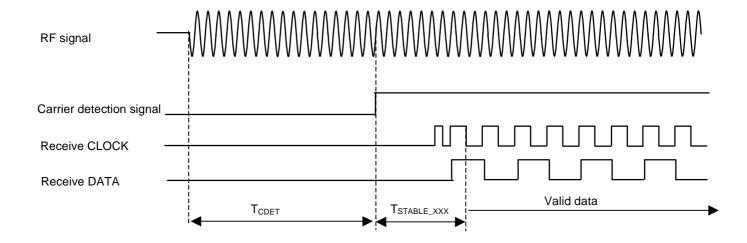

## 2.1 DEMOD Interface (RX) Function

#### 2.1.1 QPSK Demodulation Function

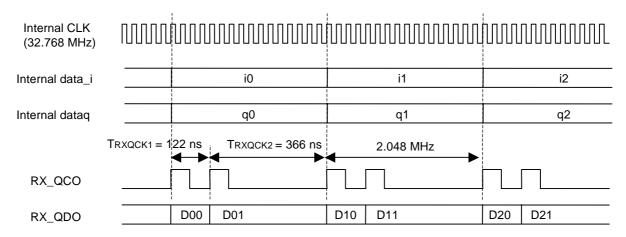

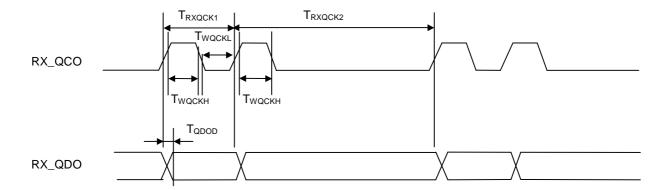

The QPSK demodulation section demodulates the QPSK signal and regenerates clocks. Figure 2-1 shows the data and clock waveform during normal output for the QPSK demodulation function. The QPSK demodulation performs modulation in units of symbols and, as shown in the figure below, produces a 2-bit output at 2.048 MHz for normal output.

When no carrier signal is detected (CAR\_DET = "L"), data and clock outputs go "L." This masking function can be disabled using a register setting command SET\_DEMOD\_SET.

While the IC is transmitting TX data, demodulation data and clock outputs stop and go "L."

Figure 2-1 QPSK Demodulation Data and Data Clock Timings

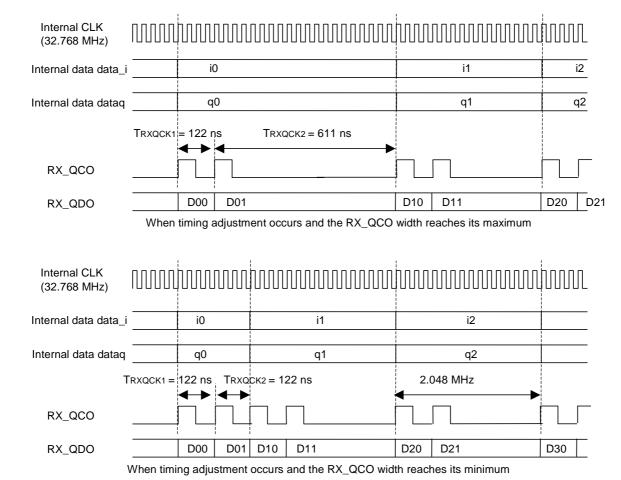

The QPSK demodulation section of the IC has a function to pull in frequency synchronously. At synchronous pulling-in or at detection of a frequency drift compared with the roadside unit, timing adjustment is performed; therefore, the output clock (RX\_QCO) may change.

Figure 2-2 shows the output timing waveforms when a frequency drift is the largest in cases where timing adjustment occurs backwards (upper diagram) and timing adjustment occurs forwards (lower diagram).

The output width of the 2nd bit of the one symbol that is demodulated is normally 366 ns, as shown in Figure 2-1; however, if timing adjustment occurs, the width is a value between a maximum of 611 ns (see the upper diagram of Figure 2-2) and a minimum of 122 ns (see the lower diagram of Figure 2-2).

Figure 2-2 Timing Adjustment at Synchronous Pulling-In

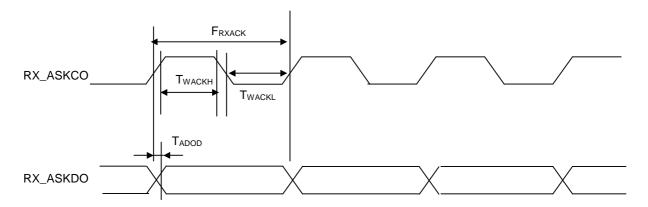

#### 2.1.2 ASK Demodulation Function

The ASK demodulation section has a decryption function for split phase of 1024kbps and a clock recovery function and outputs a 1.024 MHz clock.

In the clock recovery function, timing adjustment is performed at synchronous pulling-in or at detection of a frequency drift compared with roadside unit; therefore, the output clock (RX\_ASKCO) may change.

When no carrier signal is detected (CAR\_DET = "L"), data and clock outputs go "L." This masking function can be disabled using a register setting command SET\_DEMOD\_SET.

While the IC is transmitting TX data, demodulation data and clock outputs stop and go "L."

In addition, the ASK demodulation function can be disabled using a register setting command SET\_DEMOD\_SET. In this case, no split phase will be decrypted, nor will clock (ASK\_CO) be output; only data (ASK\_DO) will be output.

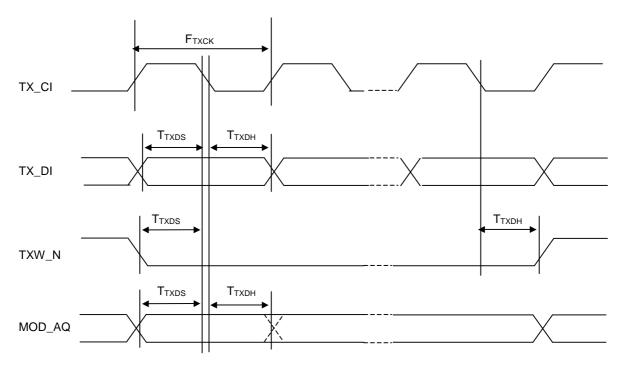

## 2.2 MODEM Interface (TX) Function

This IC performs ASK modulation and  $\pi/4$  shift QPSK modulation as transmission (TX side) functions. Switching between ASK and QPSK is made by the MOD\_AQ signal sent from the baseband LSI (BB LSI).

The TX\_CI clock input has a frequency of 4.096 MHz bon in QPSK mode and in ASK mode. Since the TX\_CI clock serves as the reference clock of the digital processing section of the IC, do not stop clock input even during the period other than during transmission.

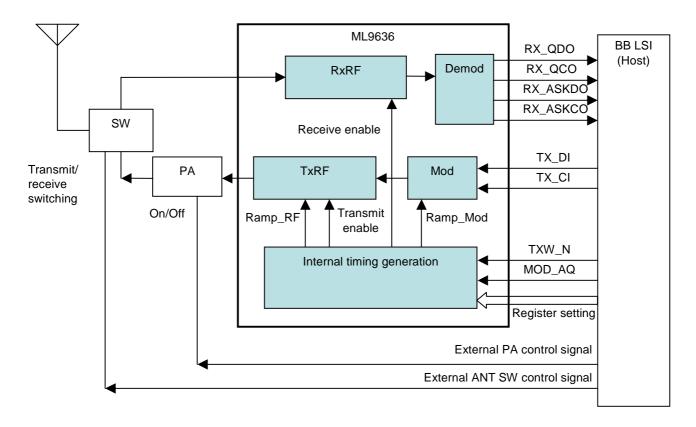

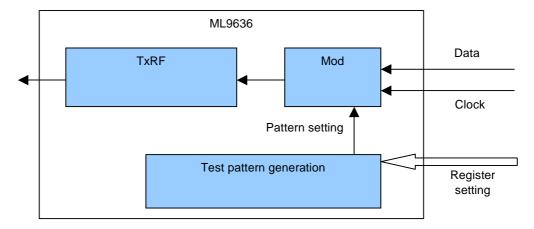

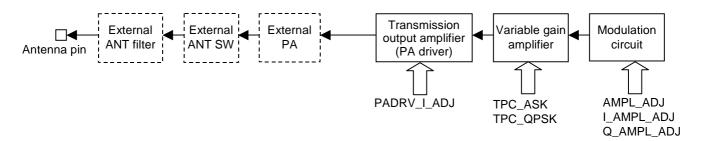

Figure 2-3 shows the relationship between the timing signal generating circuit and the blocks to be controlled during transmission.

The RF signal transmission is triggered by the TXW\_N signal from the BB LSI. Note that it must be done from the BB LSI to switch between transmission and reception at the external ANT SW or have on-off control of the external PA.

Figure 2-3 Block Diagram of Timing Control Function at Transmission

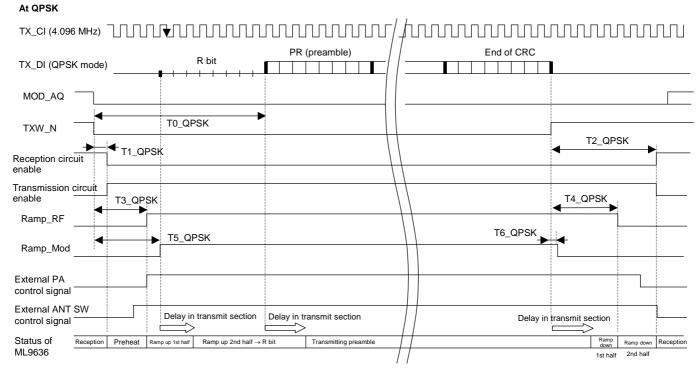

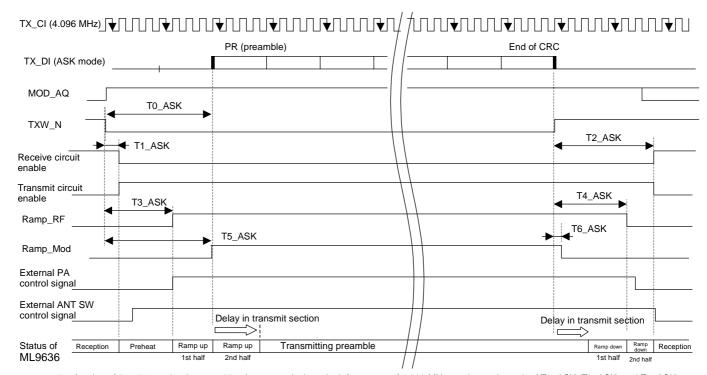

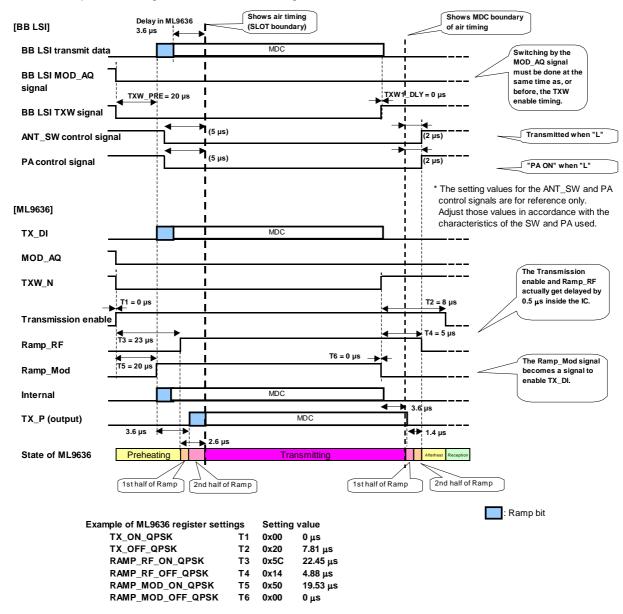

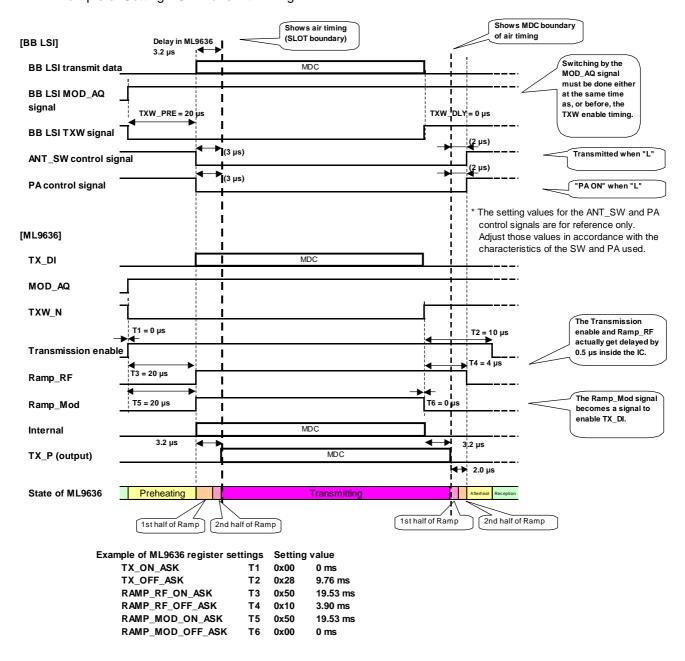

The following timing diagrams shows the relationships between the data/clock during data transmission, the transmit/receive circuit enable signal (on-off signal), the Ramp\_RF signal, and the Ramp\_Mod signal in the respective cases of ASK mode and QPSK mode.

As the clock to be input, a 4.096 MHz clock is used both in QPSK mode and in ASK mode. When in QPSK mode, the data to be input is the QPSK mode data at 4.096 Mbps; when in ASK mode, the data to be input is the data at 1.024 Mbps before split-phase coding. In ASK mode, the boundary of ASK data at 1.024 Mbps is identified by the TXW\_N signal falling edge timing. Then the "Mod" circuit performs the split phase coding of 1.024 Mbps.

It is necessary for the BB LSI to enable the TXW\_N signal prior to the transmit channel data. It is also necessary for the BB LSI to be provided with a setting function that can change the TXW\_N enable timing with respect to transmit channel data. It is recommended that the variable values (T0\_QPSK, T0\_ASK) for antecedent output be set to 0 to 255 cycles (approx. 0 to 62 µs) at an equivalent clock frequency of 4.096 MHz.

The TXW\_N signal disabling timing is the end of the CRC bit of the TX\_DI transmit channel data.

This IC generates timing for internal control signals (transmit/receive enable, Ramp\_RF, and Ramp\_Mod) based on the TXW\_N signal. So, the user needs to configure the settings for appropriate internal registers.

Fix the MOD\_AQ signal at the same time as, or before, the assertion of the TXW\_N signal. The MOD\_AQ signal is only fetched at the first cycle during which the TXW\_N signal is asserted, and no decision between ASK and QPSK is made in any other timing.

Because the R bit in QPSK mode is added before the input data from TX\_DI, fix TX\_DI to "L" during the R bit addition timing. Hold the TX\_DI input "L" also after CRC is finished.

- \* A value of 0 to 255 cycles (approx. 62 μs) at an equivalent clock frequency of 4.096 MHz can be set in each of T1\_QPSK, T3\_QPSK, and T5\_QPSK.

- \* A value of 0 to 63 cycles (approx. 16 µs) at an equivalent clock frequency of 4.096 MHz can be set in each of T2\_QPSK, T4\_QPSK, and T6\_QPSK.

- \* T0\_QPSK is set on the BB LSI side.

- \* The external PA control signal and the external ANT SW control signal are controlled from the BB LSI.

Figure 2-4 Transmit Timing Diagram in QPSK Mode

#### At ASK

- A value of 0 to 255 cycles (approx.  $62 \mu s$ ) at an equivalent clock frequency of 4.096 MHz can be set in each of T1\_ASK, T3\_ASK, and T5\_ASK. A value of 0 to 63 cycles (approx.  $16 \mu s$ ) at an equivalent clock frequency of 4.096 MHz can be set in each of T2\_ASK, T4\_ASK, and T6\_ASK.

- T0\_ASK is set on the BB LSI side.

- The external PA control signal and the external ANT SW control signal are controlled from the BB LSI side.

Figure 2-5 Transmit Timing Diagram in ASK Mode

## 2.3 Test Signal Generation Test Function

This IC is equipped with a test pattern generating circuit. Figure 2-6 shows the configuration of the test pattern generating circuit.

Figure 2-6 Configuration of the Test Pattern Generating Circuit

Table 2-1 lists the patterns that can be generated.

Each test pattern is transmitted by first writing a value for the test pattern to the register of the test command (SET\_TEST\_SEND) and then setting  $TXW_N = "L"$  with a clock being input to  $TX_CI$ .

| Pattern | Description                                                                                                                                                                                                   |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CW0     | Transmits an ASK carrier-off level equivalent continuous wave.  If QPSK mode is selected (MOD_AQ = "L"), the neutral data (origin) signal of QPSK is transmitted.                                             |

| CW1     | Transmits an ASK carrier-on level equivalent continuous wave.  If QPSK mode is selected (MOD_AQ = "L"), the neutral data (origin) signal of QPSK is transmitted.                                              |

| PN15    | Transmits a random pattern (PN15) continuously. The data to be transmitted in ASK mode is the data after split phase coding. X15+X14+1 is used as the generating polynomial, and an inverted value is output. |

Table 2-1 Test Patterns That Can Be Generated

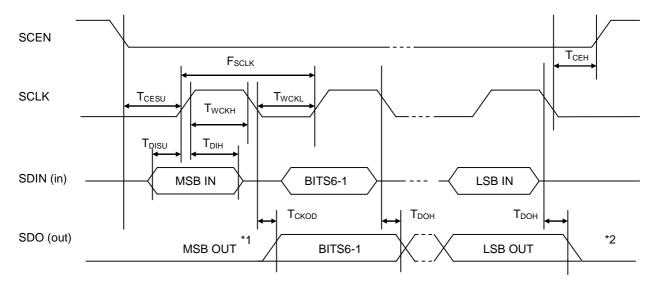

# 3. Synchronous Communication Interface (SCI) Function

The ML9636 is equipped with a synchronous communication interface (SCI) as an interface with the host.

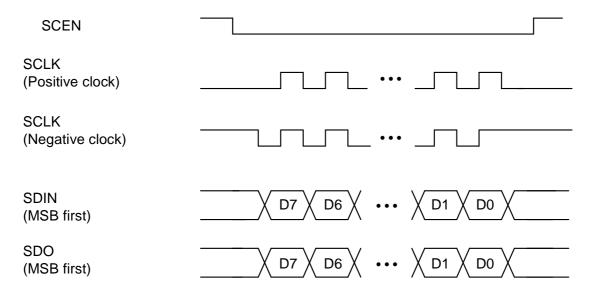

#### 3.1 Clock Timing

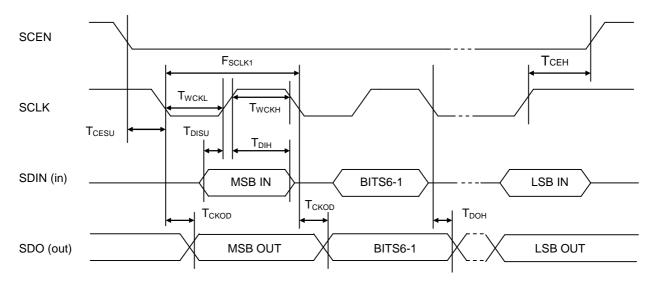

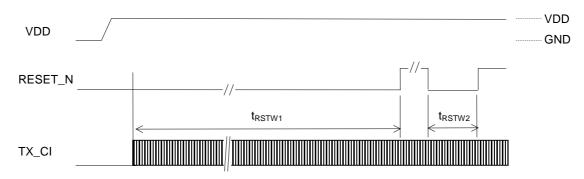

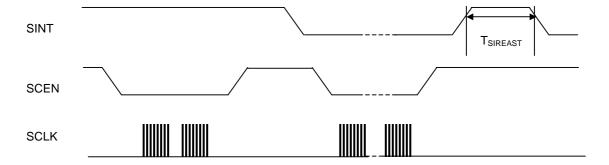

The SCI that the ML9636 has is for slave use only, and input clocks from the host are applied to rising edges only. Only MSB first is supported for transmit/receive data.

Figure 3-1 SCI Clocks and Data Transmit/Receive Waveforms

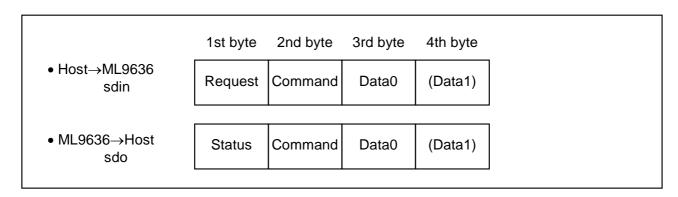

#### 3.2 Data Format

Figure 3-2 shows the transfer data format.

Transfer data consists of request or status byte, command byte, and data byte(s). The number of data bytes is either one or two depending on the command.

The types of commands are: SET commands to set registers, GET\_request and GET\_confirm commands to read registers, and SET\_confirm command that is returned from the ML9636 if a SET command error occurs.

To configure settings from the host to the ML9636, write setting values using the SET command. To read from the host into the ML9636, send the GET\_request command from the host, and the ML9636 will assert SINT and returns the corresponding GET\_confirm command and the read value if set to output enable for reading from the host. If a SET command error is detected, the ML9636 asserts SINT and, if set to output enable for reading from the host, returns the SET\_confirm command.

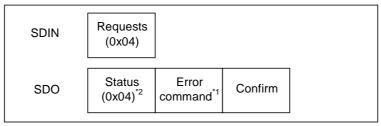

Figure 3-2 Transfer Data Format

#### 3.2.1 Transaction

The request is exchanged with the status between the host and the ML9636 at the first transfer byte. If host →ML9636 or ML9636→host or both are feasible, data transfer for the second byte onwards is carrired out. Use the SET command to write a setting value to the ML9636 and the GET command to read the set value from it.

#### 3.2.2 Request/Status Byte

The host sends a request to the ML9636 and at the same time, the ML9636 sends the status to the host. For the request and status, only bits 3 and 2 out of the eight bits (bits 7–0) are used (positive logic) and the other bits are Don't Care, as shown below. When the bits at the same bit position in the request and status transmitted from the host and the ML9636 are both in the "1" state, a handshaking between the host and the ML9636 is established and data transmission/reception for the second bytes onwards starts.

In the actual ML9636 status output, "0x0C" (both bits 3 and 2 are "1") is always returned to the host in order to support read and write to the host at the same time.

| Bit | Request (Host→ML9636)    | Status (ML9636→Host)    |

|-----|--------------------------|-------------------------|

| 3 - | Setup data write request | Setup data write enable |

|     | Setup data read request  | Setup data read enable  |

| 2   | Confirm enable           | Confirm request         |

#### 3.2.3 Command Byte and Data Bytes

There exist commands and data that accompanies them. For the details of each command, refer to "A Separate Volume for the ML9636 User's Manual Command Details."

#### 3.2.4 Timing Diagram

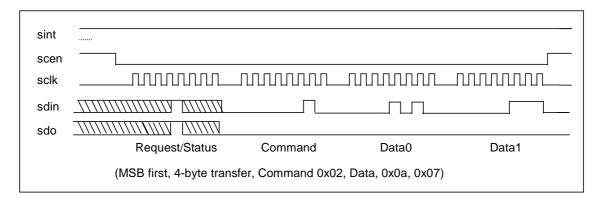

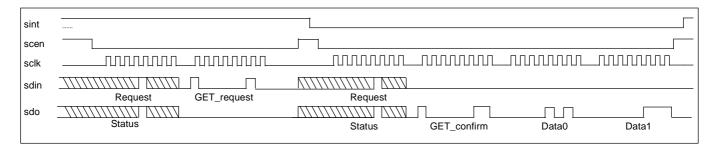

Figure 3-3 Host→ML9636 Data Write (SET command)

- \* Do not negate (scen="H") scen during transfer. If it is negated, the transfer data is invalid.

- \* The interrupt (sint) changes only when scen is "H".

- \* When only a write operation is performed after interrupt occurrence, the ML9636 first negates sint and then asserts sint again.

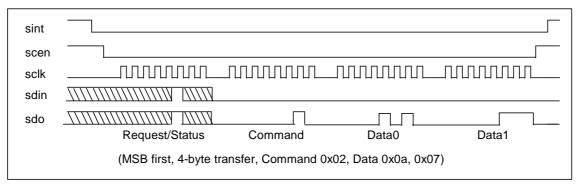

Figure 3-4 ML9636→Host Data Read (GET command)

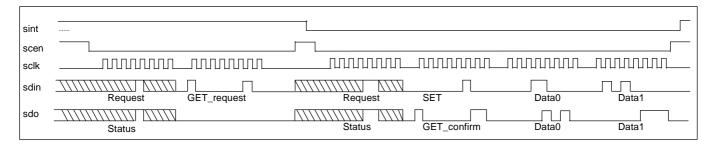

#### 3.3 Setting Write Data

Use the SET command to write a setting value from the host to the ML9636.

Register setting to the ML9636 can be achieved by setting bit 3 of byte 1 to "1" and writing a setting value to byte 2 onwards using the SET command and sending the data to the ML9636 from the host.

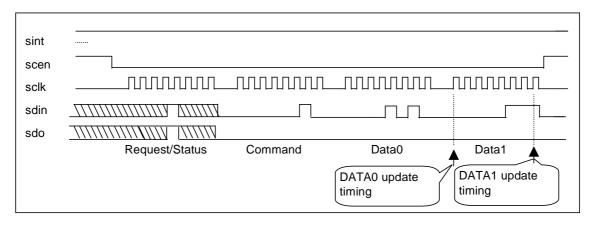

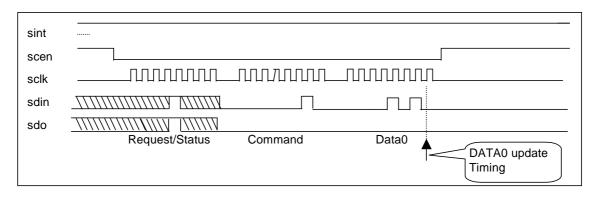

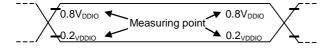

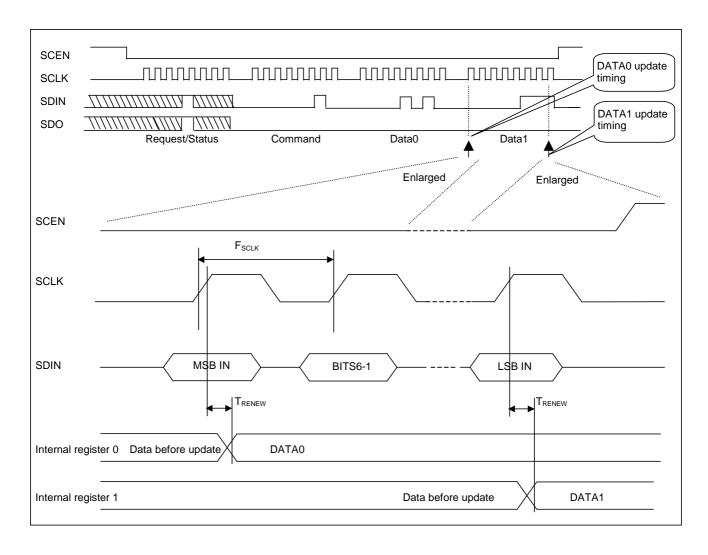

The internal register update timing varies depending on whether the length of the setting data is two bytes or one byte. If the length of setting data is two bytes, the update timing for DATA0 is hundreds of nanoseconds after the first rising edge of SCLK of the subsequent DATA1 transmission, and the update timing for DATA1 is hundreds of nanoseconds after the SCLK rising edge at the eighth bit of DATA1. Meanwhile, if the length of the setting data is one byte, the update timing is hundreds of nanoseconds after the SCLK rising edge at the eighth bit of DATA0. Figures 3-5 and 3-6 shows the outlines of update timing.

Figure 3-5 Data Write Timing (Setting Data: 2 Bytes)

Figure 3-6 Data Write Timing (Setting Data: 1 Byte)

If a data write is not carried out correctly, the ML9636 asserts the SINT signal and notifies the host of a write error.

When SINT has been asserted, the command at the error occurrence and the error contents will be output from the ML9636 by setting the request byte (first transfer byte) to "Confirm enable" (set bit 2 to "1") from the host. (Reading by a SET\_confirm command.)

The command at the error occurrence to be output is displayed as a value (command) of the target SET command incremented by 1.

When reading of the error state is completed, the SINT signal is negated.

If reading by a SET\_confirm command is not executed upon the assertion of SINT, SINT is left asserted. So, be sure to execute a SET\_confirm command read.

## At a read by a SET\_confirm

Figure 3-7 SET\_Confirm Data Format

- \*1 The command at an error occurrence is output as a value (command) of the target SET command incremented by

- \*2 In the actual ML9636 status output, "0x0C" is always returned in order to support read and write to the host at the same time.

## [Details of Confirm]

| Contents              | Data | Description                                             |

|-----------------------|------|---------------------------------------------------------|

| UNSUPPORTED_ATTRIBUTE | 0x0A | Error occurred that indicates set data being too short. |

The conditions for causing incorrect writing and the possible resultant operations are shown below.

| Command conditions                                                 | SCEN negate timing                                                                                                                               | Operation                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All SET commands                                                   | When SCEN is negated before completion of transmission up to the Command data                                                                    | The command fails. Operates normally at the next command and onwards.                                                                                                                                                                                                                                                                                                            |

|                                                                    | When SCEN is negated after completion of transmission up to the Command data                                                                     | For a SET command, the data write ends in failure and the ML9636 asserts SINT. After that, when a read request is received, the ML9636 sends the command <sup>(*1)</sup> at the error occurrence and the error contents and negates SINT.                                                                                                                                        |

|                                                                    | When SCEN is negated before the SCLK rising edge at the eighth bit 8                                                                             | Since the data write fails, the internal register is not updated.  The ML9636 asserts SINT and notifies the host of the write error.  When a read request is received, the ML9636 sends the command <sup>(*1)</sup> at the error occurrence and the error contents and negates SINT.                                                                                             |

| Commands<br>where the<br>number of<br>data bytes to<br>be set is 1 | When SCEN is negated immediately after the SCLK rising edge at the eighth bit (when SCEN is negated without observing the interface regulations) | If the data write fails, the ML9636 asserts SINT and notifies the host of the write error. When a read request is received, the ML9636 sends the command <sup>(*1)</sup> at the error occurrence and the error contents and negates SINT.  If SINT is not asserted, it indicates that the data write has succeeded. However, whether the set value is correct is not guaranteed. |

|                                                                    | When the number of SCLK clock pulses is larger than the number prescribed for the command                                                        | The data write succeeds and setting in the register is performed normally.  The excessive clocks and data are ignored.                                                                                                                                                                                                                                                           |

| Command conditions           | SCEN negate timing                                                                                                                                                                                               | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                              | When SCEN is negated before the SCLK rising edge at the first bit in the second byte (DATA1)                                                                                                                     | Since the data write fails, the internal register is not updated.  The ML9636 asserts SINT and notifies the host of the write error.  When a read request is received, the ML9636 sends the command <sup>(*1)</sup> at the error occurrence and the error contents and negates SINT.                                                                                                                                                                                                              |  |

| Commands where the number of | When, although transmission was done normally up to the first bit (SCLK rising edge) in the second byte (DATA1), SCEN is negated before the transmission of the eighth bit (SCLK rising edge) in the second byte | Writing of the data (DATA0) at the first byte is effected and DATA0 is updated. However, DATA1 is not updated, because writing of the data at the second byte ends in failure.  The ML9636 asserts SINT and notifies the host of the write error.  When a read request is received, the ML9636 sends the command (*1) at the error occurrence and the error contents and negates SINT.                                                                                                            |  |

| data bytes to<br>be set is 2 | When SCEN is negated immediately after the SCLK rising edge at the eighth bit 8 (when SCEN is negated without observing the interface regulations)                                                               | If the data write fails, the ML9636 asserts SINT and notifies the host of the write error. In this case, the data (DATA0) at the first byte is updated but the data (DATA1) at the second byte is not. When a read request is received, the ML9636 sends the command <sup>(*1)</sup> at the error occurrence and the error contents and negates SINT. If SINT is not asserted, it indicates that the data write has succeeded. However, whether the DATA1 set value is correct is not guaranteed. |  |

|                              | When the number of SCLK clocks is larger than the number prescribed for the command                                                                                                                              | The data write succeeds and the register is set normally.  The excessive clocks and data are ignored.                                                                                                                                                                                                                                                                                                                                                                                             |  |

<sup>\*1</sup> The command at an error occurrence is output as a value (command) of the target SET command incremented by 1.

#### 3.4 Reading Set Data

For the host to read set values in the ML9636, use a GET command.

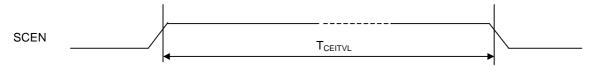

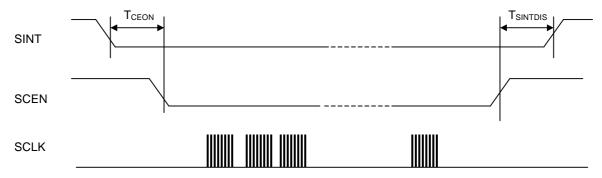

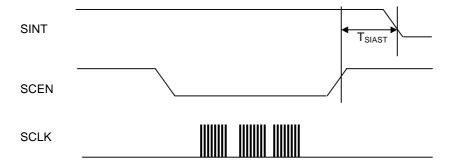

By setting bit 3 of the first byte to "1" and transmitting a GET\_request command at the second byte, the ML9636 prepares for a read. When the ML9636 completes the preparation, it asserts the SINT signal. It takes several microseconds after the negation of SCEN to assert SINT. The host must confirm that the SINT signal has been asserted and then execute the read request (read output enable).

Figure 3-8 shows the timing diagram for read. A simultaneous operation of a read and a write is also possible. Figure 3-9 shows the timing diagram when performing a read and a write simultaneously.

Figure 3-8 Timing Diagram for Read

Figure 3-9 Timing Diagram for Read and Write (when read and write are simultaneously performed)

The conditions for causing incorrect reading and the possible resultant operations are shown below.

| Command conditions | SCEN negate timing                                                                                       | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | When SCEN is negated before completion of transmission up to the Command data                            | The command fails. Operates normally at the next command and onwards.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                    | When SCEN is negated after completion of transmission up to the Command data                             | In the case of a GET command, the ML9636 asserts SINT after completion of the preparation for a read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                    | When SCEN is asserted before SINT is asserted after the GET_request command is transmitted               | The GET_confirm command is not returned from the ML9636. SINT is asserted after SCEN is negated, thereby enabling the GET_confirm command to be read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GET<br>commands    | When one GET_request command is transmitted and then another GET_request command is transmitted          | The ML9636 can hold a maximum of two GET_request commands. Therefore, when the first read is executed, the GET_confirm command that corresponds to the first GET_request command is transmitted, and when the second read is executed, the GET_confirm command that corresponds to the second GET_request command is transmitted. If three or more GET_request commands are executed in succession, the GET_request command being held at the second time will be overwritten. When the reads are executed, the GET_confirm command that corresponds to the first GET_request command is transmitted, then the GET_confirm command that corresponds to the last GET_request command is transmitted. |

|                    | When the GET_request command is transmitted and then a SET command is executed without performing a read | SINT is once negated and the SET command is executed normally.  When SCEN is negated after the SET command is executed, SINT is asserted again, thereby enabling a read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | When SCEN is negated before all the GET_confirm command data is transmitted                              | SINT will be left asserted.  If a read is performed again, the GET_confirm command is transmitted; however, the read data at that time is not guaranteed. Transmit the GET_request command again.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# 4. List of Commands

The following table lists the commands required for normal data transmission/reception. These commands can be input from the SCI interface.

| -              | e SCI interface.                      | 1                                                                         | T                          |

|----------------|---------------------------------------|---------------------------------------------------------------------------|----------------------------|

| Command (code) | Name                                  | Description                                                               | Direction                  |

| 0x02           | SET_VCV_RAW                           | VCO calibration control setting                                           | Host→ML9636                |

| 0x04           | SET_FMAP                              | PLL counter setting                                                       | Host→ML9636                |

| 0x06           | SET_HDAC_QPSK1                        | QPSK HDAC adjustment 1                                                    | Host→ML9636                |

| 0x08           | SET_HDAC_QPSK2                        | QPSK HDAC adjustment 2                                                    | Host→ML9636                |

| 0x0A           | SET_HDAC_ASK                          | ASK HDAC adjustment                                                       | Host→ML9636                |

| 0x0C           | SET_TPC                               | Gain control for QPSK/ASK                                                 | Host→ML9636                |

| 0x0E           | SET_RF_TMP                            | RF section adjustment (RF_TEMP)                                           | Host→ML9636                |

| 0x10           | SET_CAR_DET_LVL                       | Carrier detection level setting                                           | Host→ML9636                |

| 0x12           | SET_CAR_DET_CTL                       | Carrier detection hysteresis width adjustment                             | Host→ML9636                |

| 0x16           | SET_RF0                               | RF section adjustment 0                                                   | Host→ML9636                |

| 0x18           | SET_RF1                               | RF section adjustment 1                                                   | Host→ML9636                |

| 0x1A           | SET_RF2                               | RF section adjustment 2                                                   | Host→ML9636                |

| 0x1C           | SET_RF3                               | RF section adjustment 3                                                   | Host→ML9636                |

| 0x20           | SET_DEMOD_SET                         | DEMOD section configuration                                               | Host→ML9636                |

| 0x22           | SET_TEST_SEND                         | Generation of test patterns for transmission                              | Host→ML9636                |

| 0x24           | SET TX ON ASK                         | TX ON/RX OFF timing adjustment (T1_ASK)                                   | Host→ML9636                |

| 0x26           | SET_TX_OFF_ASK                        | TX OFF/RX ON timing adjustment (T2_ASK)                                   | Host→ML9636                |

| 0x28           | SET_RAMP_RF_ON_ASK                    | RAMP RF ON timing adjustment (T3_ASK)                                     | Host→ML9636                |

| 0x2A           | SET_RAMP_RF_OFF_ASK                   | RAMP RF OFF timing adjustment (T4_ASK)                                    | Host→ML9636                |

| 0x2C           | SET_RAMP_MOD_ON_ASK                   | RAMP MOD ON timing adjustment (T5_ASK)                                    | Host→ML9636                |

| 0x2E           | SET_RAMP_MOD_OFF_ASK                  | RAMP MOD OFF timing adjustment (T6_ASK)                                   | Host→ML9636                |

| 0x30           | SET_TX_ON_QPSK                        | TX ON/RX OFF timing adjustment (T1_QPSK)                                  | Host→ML9636                |

| 0x32           | SET_TX_OFF_QPSK                       | TX OFF/RX ON timing adjustment (T2_QPSK)                                  | Host→ML9636                |

| 0x34           | SET_RAMP_RF_ON_QPSK                   | RAMP RF ON timing adjustment (T3_QPSK)                                    | Host→ML9636                |

| 0x36           | SET_RAMP_RF_OFF_QPSK                  | RAMP RF OFF timing adjustment (T4_QPSK)                                   | Host→ML9636                |

| 0x38           | SET_RAMP_MOD_ON_QPSK                  | RAMP MOD ON timing adjustment (T5_QPSK)                                   | Host→ML9636                |

| 0x3A           | SET_RAMP_MOD_OFF_QPSK                 | RAMP MOD OFF timing adjustment (T6_QPSK)                                  | Host→ML9636                |

| 0x3C           | SET_TEST_MODE                         | Test monitor mode setting                                                 | Host→ML9636                |

| 0x3E           | SET_INITIAL                           | Initial setting                                                           | Host→ML9636                |

| 0x82           | GET_VCV_RAW_request                   | VCO calibration results register read request                             | Host→ML9636                |

| 0x83           | GET_VCV_RAW_confirm                   | VCO calibration results register read                                     | ML9636→HOST                |

| 0x84           | GET_FMAP_request                      | PLL counter settings read request                                         | Host→ML9636                |

| 0x85           | GET_FMAP_confirm                      | PLL counter settings read                                                 | ML9636→HOST                |

|                | 021_1 10011 _001111111                | I ch DC offset and amplitude adjustment value                             | MEGGGG /IIGGI              |

| 0x86           | GET_HDAC_QPSK1_request                | read request                                                              | Host→ML9636                |

| 0x87           | GET_HDAC_QPSK1_confirm                | I ch DC offset and amplitude adjustment value read                        | ML9636→HOST                |

| 0x88           | GET_HDAC_QPSK2_request                | QchDC offset, amplitude, and phase adjustment value read request          | Host→ML9636                |

| 0x89           | GET_HDAC_QPSK2_confirm                | QchDCoffset, amplitude, and phase adjustment value read                   | ML9636→HOST                |

| 0x8A           | GET_HDAC_ASK_request                  | ASK DC offset and amplitude adjustment value read request                 | Host→ML9636                |

| 0x8B           | GET_HDAC_ASK_confirm                  | ASK DC offset and amplitude adjustment value read                         | ML9636→HOST                |

| 0x8C           | GET_TPC_request                       | QPSK/ASK gain control value read request                                  | Host MI 0636               |

| 0x8D           | GET_TPC_request                       | QPSK/ASK gain control value read  QPSK/ASK gain control value read        | Host→ML9636<br>ML9636→HOST |

| 0x8E           |                                       | Ţ                                                                         |                            |

| OYOE           | GET_RF_TMP_request GET_RF_TMP_confirm | RF section adjustment value read request RF section adjustment value read | Host→ML9636<br>ML9636→HOST |

| Command (code) | Name                          | Name Description                                                 |             |

|----------------|-------------------------------|------------------------------------------------------------------|-------------|

| 0x90           | GET_CAR_DET_LVL_request       | Carrier detection level setting value read request               | Host→ML9636 |

| 0x91           | GET_CAR_DET_LVL_confirm       | Carrier detection level setting value read                       | ML9636→HOST |

| 0x92           | GET_CAR_DET_CTL_request       | Carrier detection hysteresis width adjustment value read request | Host→ML9636 |

| 0x93           | GET_CAR_DET_CTL_confirm       | Carrier detection hysteresis width adjustment value read         | ML9636→HOST |

| 0x94           | GET_INIT_READ_request         | This command is canceled                                         | Host→ML9636 |

| 0x95           | GET_INIT_READ_confirm         | This command is canceled                                         | ML9636→HOST |

| 0x96           | GET_RF0_request               | RF section adjustment 0 value read request                       | Host→ML9636 |

| 0x97           | GET_RF0_confirm               | RF section adjustment 0 value read                               | ML9636→HOST |

| 0x98           | GET_RF1_request               | RF section adjustment 1 value read request                       | Host→ML9636 |

| 0x99           | GET_RF1_confirm               | RF section adjustment 1 value read                               | ML9636→HOST |

| 0x9A           | GET_RF2_request               | RF section adjustment 2 value read request                       | Host→ML9636 |

| 0x9B           | GET_RF2_confirm               | RF section adjustment 2 value read                               | ML9636→HOST |

| 0x9C           | GET_RF3_request               | RF section adjustment 3 value read request                       | Host→ML9636 |

| 0x9D           | GET_RF3_confirm               | RF section adjustment 3 value read                               | ML9636→HOST |

| 0xA0           | GET_DEMOD_request             | DEMOD section settings read request                              | Host→ML9636 |

| 0xA1           | GET_DEMOD_confirm             | DEMOD section settings read                                      | ML9636→HOST |

|                |                               | Read request for generation settings of test                     |             |

| 0xA2           | GET_TEST_SEND_request         | patterns for transmission                                        | Host→ML9636 |

| 0xA3           | GET_TEST_SEND_confirm         | Read generation settings of test patterns for transmission       | ML9636→HOST |

| 0xA4           | GET_TX_ON_ASK_request         | TX ON/RX OFF timing value read request                           | Host→ML9636 |

| 0xA5           | GET_TX_ON_ASK_confirm         | TX ON/RX OFF timing value read                                   | ML9636→HOST |

| 0xA6           | GET_TX_OFF_ASK_request        | TX OFF/RX ON timing value read request                           | Host→ML9636 |

| 0xA7           | GET_TX_OFF_ASK_confirm        | TX OFF/RX ON timing value read                                   | ML9636→HOST |

| 0xA8           | GET_RAMP_RF_ON_ASK_request    | RAMP RF ON timing value read request                             | Host→ML9636 |

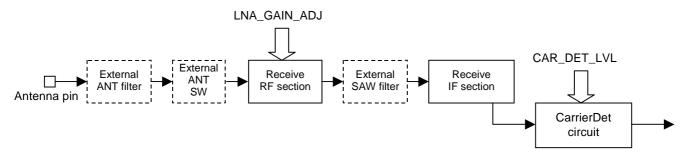

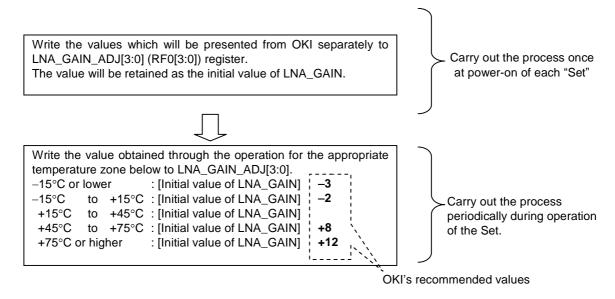

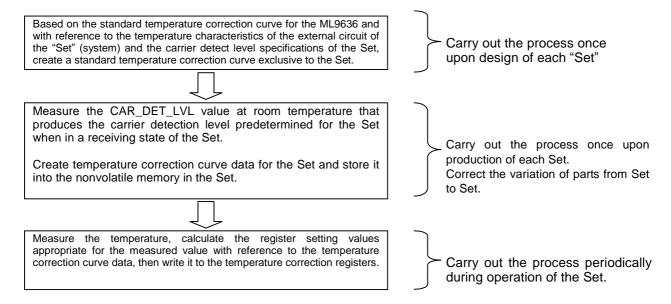

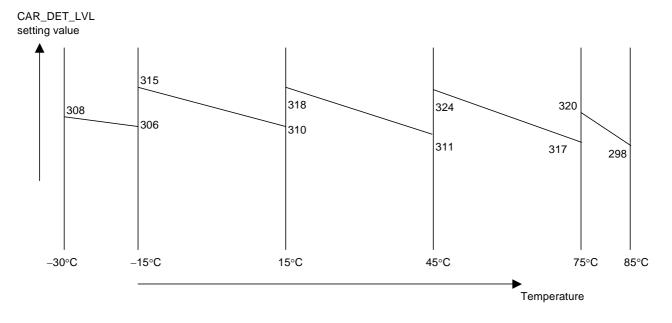

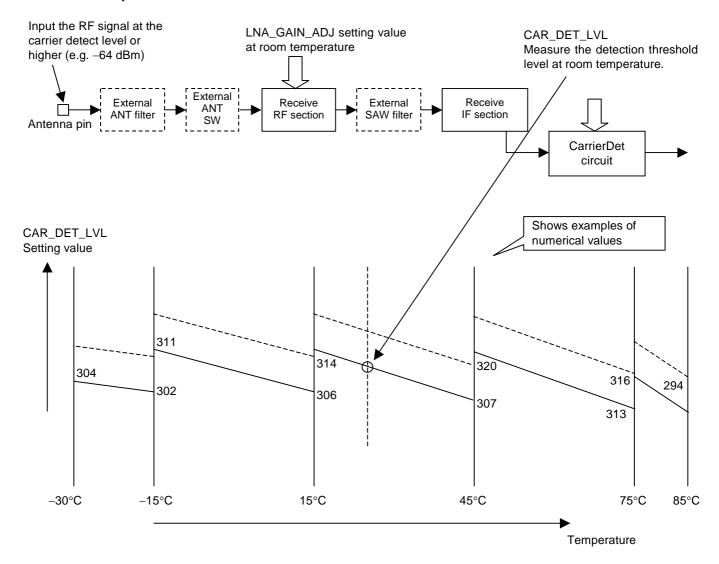

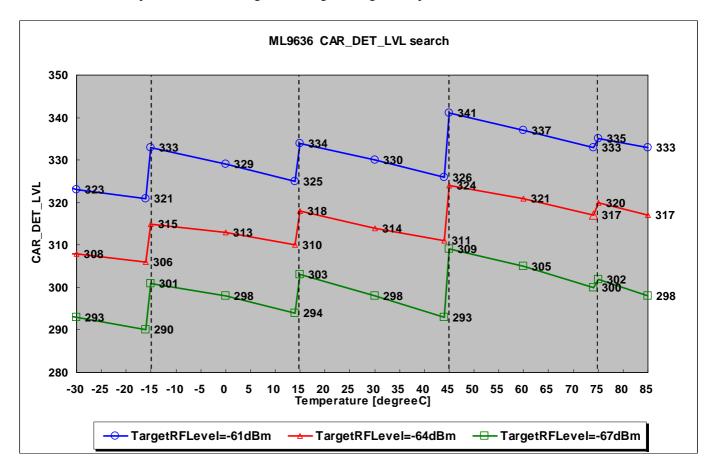

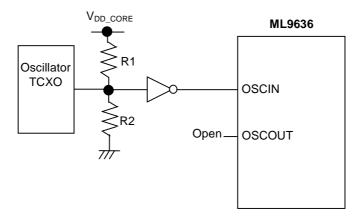

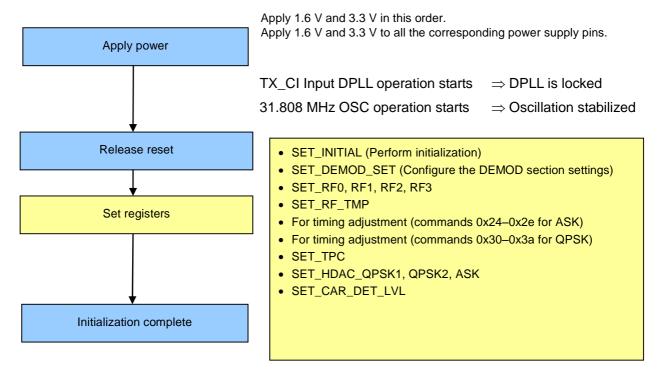

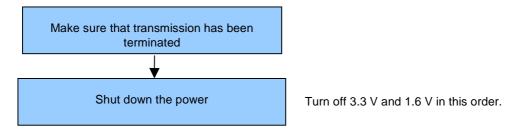

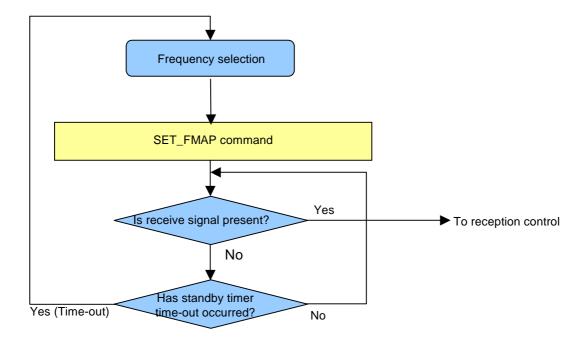

| 0xA9           | GET_RAMP_RF_ON_ASK_confirm    | RAMP RF ON timing value read                                     | ML9636→HOST |