LOGIC Emulation Source

# User Guide DN9000K10PCIE4GL

LOGIC EMULATION SOURCE

# **DN9000K10PCIE4GL User Manual**

Major Revision 1

Last Update November 26, 2008

# © The Dini Group, 2006

1010 Pearl Street • Suite 6

La Jolla, CA92037 USA

Phone 858.454.3419 • Fax 858.454.1279

<a href="mailto:support@dinigroup.com">support@dinigroup.com</a>

<a href="mailto:www.dinigroup.com">www.dinigroup.com</a>

# Table of Contents

| C | HAPTER 1: INTRODUCTION                              | 1  |

|---|-----------------------------------------------------|----|

|   |                                                     |    |

| 1 | MANUAL CONTENTS                                     | 1  |

|   | Introduction                                        | 1  |

|   | QUICK START GUIDE                                   | 1  |

|   | CONTROLLER SOFTWARE                                 | 2  |

|   | HARDWARE                                            | 2  |

|   | THE REFERENCE DESIGN                                | 2  |

|   | Ordering Information                                | 2  |

| 2 | CONVENTIONS                                         | 2  |

| _ |                                                     |    |

|   | 2.1 TYPOGRAPHICAL                                   |    |

|   | 2.2 MANUAL CONTENT                                  |    |

|   | 2.2.1 File names                                    |    |

|   | 2.2.2 Physical Dimensions                           |    |

|   | 2.2.3 Part Pin Names                                |    |

|   | 2.2.4 Schematic Clippings                           |    |

|   | 2.3 TERMINOLOGY                                     | 3  |

| 3 | RESOURCES                                           | 4  |

|   | A. I. GD                                            |    |

|   | 3.1 USER CD                                         |    |

|   | 3.2 DINIGROUP.COM                                   |    |

|   | 3.3 ERRATA AND CUSTOMER NOTIFICATIONS               |    |

|   | 3.4 SCHEMATICS AND NETLIST                          |    |

|   | 3.4.1 Netlist                                       |    |

|   | 3.4.2 Net name conventions                          |    |

|   | 3.5 DATASHEET LIBRARY                               |    |

|   | 3.6 XILINX                                          |    |

|   | 3.7 DINI GROUP REFERENCE DESIGNS                    |    |

|   | 3.8 BOARD MODELS                                    |    |

|   | •                                                   |    |

| 4 | EMAIL AND PHONE SUPPORT                             | 6  |

|   |                                                     |    |

| C | HAPTER 2: QUICK START GUIDE                         | 9  |

|   |                                                     |    |

| 1 | PROVIDED MATERIALS                                  | 9  |

|   | 1.1 System Requirements                             | 9  |

|   |                                                     |    |

| 2 | WARNINGS                                            | 10 |

|   | 2.1 ESD                                             | 10 |

|   | 2.2 OTHER                                           |    |

|   |                                                     |    |

| 3 | PRE-POWER ON INSTRUCTIONS                           | 10 |

|   | 3.1 INSTALL MEMORY                                  | 11 |

|   | 3.2 PREPARE CONFIGURATION FILES                     |    |

|   | 3.3 INSTALL DN9000K10PCIE4GL IN COMPUTER (OPTIONAL) |    |

|   | 3.4 CABLES                                          |    |

|   | 3.4.1 Connect RS232 Cable                           |    |

|   | 3.4.2 Connect USB Cable                             |    |

|   | 3.4.3 Connect Power cable                           |    |

| , | DOWED ON                                            |    |

| 4 | POWER ON                                            | 14 |

|   | 4.1 VIEW CONFIGURATION FEEDBACK OVER RS232          | 14 |

|   | 4.2 CHECK LED STATUS LIGHTS                         |    |

| _ | DIN LICE CONTROLLED                                 | 10 |

|   | 5.1 Driver Installation                  |    |

|---|------------------------------------------|----|

|   | 5.2 OPERATING THE USB CONTROLLER PROGRAM |    |

|   | 5.2.1 Configure an FPGA                  |    |

|   | 5.2.2 Set Clock Frequencies              |    |

|   | 5.2.3 Check clock frequencies            |    |

|   | 5.2.4 Run Hardware Test (DDR2)           |    |

|   |                                          |    |

| 6 | 6 COMMUNICATING OVER THE SERIAL PORT     | 21 |

| - | 7 SCAN THE JTAG CHAIN                    | 21 |

| 7 |                                          |    |

|   | 7.1 MOVING ON                            |    |

| C | CHAPTER 3: CONTROLLER SOFTWARE           | 23 |

| 1 | 1 USB CONTROLLER                         | 24 |

|   | 1.1 Main Window                          | 24 |

|   | 1.1.1 Refresh Button                     |    |

|   | 1.1.2 Disable/Enable USB                 |    |

|   | 1.1.3 Log Window                         |    |

|   | 1.1.4 Board Graphic                      |    |

|   | 1.2 MENU OPTIONS                         |    |

|   | 1.2.1 File Menu                          |    |

|   | 1.2.3 FPGA Configuration Menu            |    |

|   | 1.2.4 FPGA Reference Design              |    |

|   | 1.2.5 Main Bus                           |    |

|   | 1.2.6 Settings/Info Menu                 |    |

|   | 1.3 Unsupported Features                 |    |

|   | 1.3.1 Header Test                        |    |

|   | 1.3.2 Programmer's Menu                  |    |

|   | 1.4 Log File                             |    |

|   | 1.6 COMPILING USB CONTROLLER             |    |

| 2 |                                          |    |

| 4 |                                          |    |

|   | 2.1 COMPILING AETEST_USB                 |    |

|   | 2.1.1 Cygwin                             |    |

| 3 | 3 ROLLING YOUR OWN SOFTWARE              | 33 |

|   | 3.1 DINI API                             | 33 |

|   | 3.2 USB                                  | 33 |

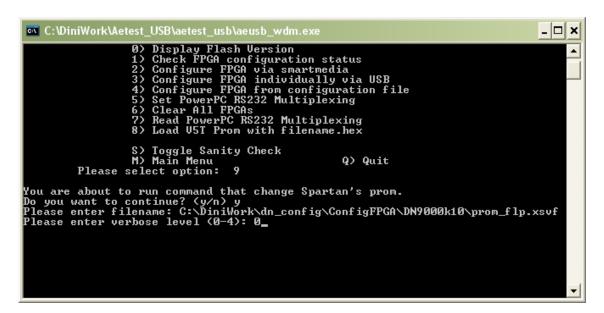

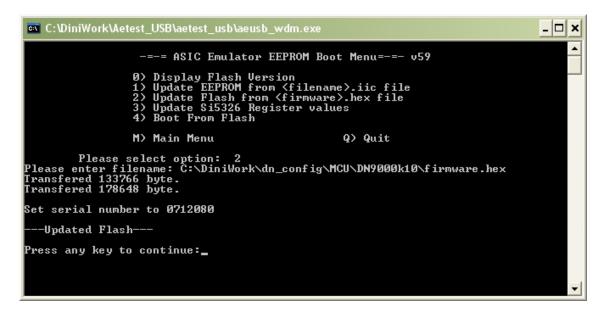

| 4 | 4 UPDATING THE FIRMWARE                  | 33 |

| • | 4.1 Obtaining the updates                |    |

|   | 4.1 OBTAINING THE UPDATES                |    |

|   | 4.3 UPDATING THE MCU (FLASH) FIRMWARE    |    |

|   | 4.4 UPDATING THE SPARTAN (PROM) FIRMWARE | 34 |

| C | CHAPTER 4: HARDWARE                      | 43 |

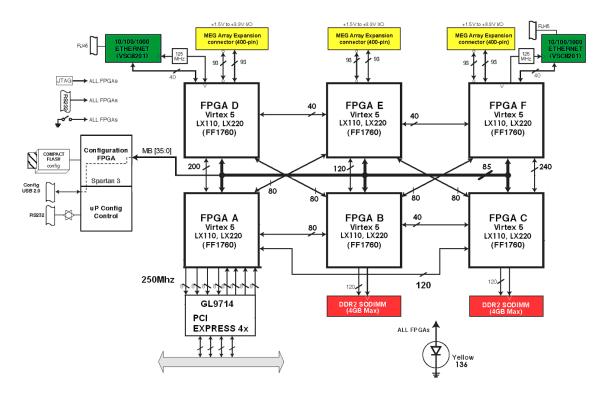

| 1 | 1 GENERAL OVERVIEW                       | 43 |

| • |                                          |    |

|   | 1.1 MARKETING CRAP                       |    |

|   | 1.1.1 Features                           |    |

| • |                                          |    |

| 2 | 2 VIRTEX 5                               | 46 |

| 3 | 3 CONFIGURATION SECTION                  | 46 |

|   | 3.1 CONFIGURATION SECTION FEEDBACK       | 47 |

|   | 3.2 FPGA Configuration                   |    |

|   | 3.3 USB INTERFACES                       |    |

|   | 3.4 CompactFlash Interface               | 49 |

|   | 3.4.1           | Main.txt                                 | 50 |

|---|-----------------|------------------------------------------|----|

|   | 3.4.2           | Limitations                              | 53 |

|   | 3.4.3           | Hardware                                 |    |

|   | 3.5 Cc          | ONFIGURATION REGISTERS                   |    |

|   | 3.5.1           | Undocumented controls                    |    |

|   | 3.6 Fi          | RMWARE                                   | 54 |

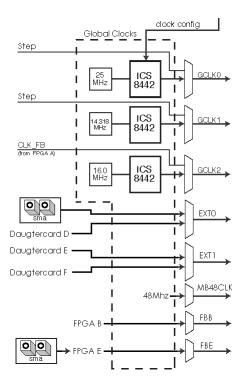

| 4 | CLOC            | K NETWORK                                | 55 |

|   | 4.1.1           | GC Pins                                  | 55 |

|   | 4.2 GI          | LOBAL CLOCKS                             |    |

|   | 4.3 GO          | ), G1, G2 Clocks                         | 57 |

|   | 4.3.1           | Clock Synthesizers                       | 57 |

|   | 4.3.2           | Possible Outputs                         |    |

|   | 4.3.3           | Duty Cycle                               |    |

|   |                 | XT CLOCKS                                |    |

|   | 4.4.1           | EXTO                                     |    |

|   | 4.4.2<br>4.4.3  | EXT1  Daughtercard zero-delay mode       |    |

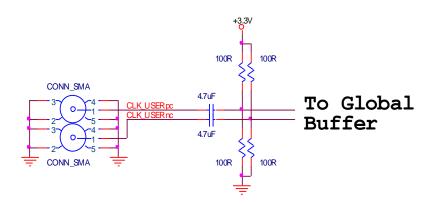

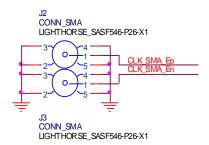

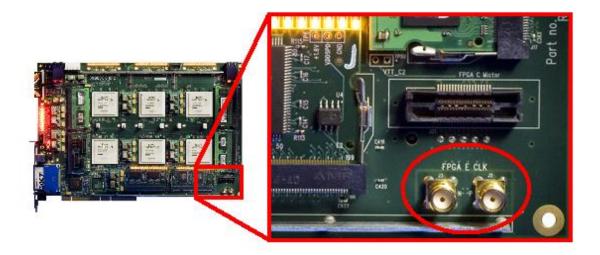

|   | 4.4.3<br>4.4.4  | SMA input                                |    |

|   |                 | SCLOCKS                                  |    |

|   |                 | ON-GLOBAL CLOCKS                         |    |

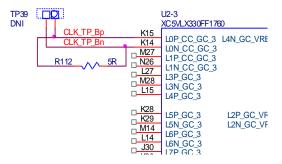

|   | 4.6.1           | Clock TP                                 |    |

|   | 4.6.2           | Ethernet Clocks                          |    |

|   | 4.6.3           | DDR2 Clocks                              |    |

|   | 4.6.4           | SMA Clock E                              |    |

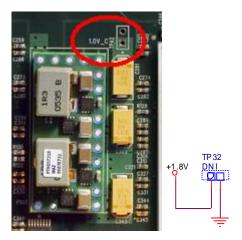

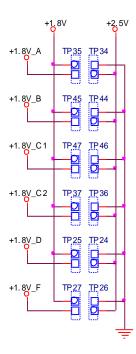

| 5 | TEST I          | POINTS                                   | 63 |

| ٥ |                 |                                          |    |

|   |                 | OWER THRU-HOLE                           |    |

|   |                 | OWER TP                                  |    |

|   |                 | MM POWER                                 |    |

|   |                 | OCK TEST POINTS                          |    |

|   |                 | MM Signals                               |    |

| , |                 | VTERFACE                                 |    |

| 6 |                 |                                          |    |

|   |                 | NLH API                                  |    |

|   |                 | ONNECTING TO THE DN9000K10PCIE4GL        |    |

|   | 6.2.1           | Windows XP                               |    |

|   | 6.2.2           | Windows Vista                            |    |

|   | 6.2.3<br>6.2.4  | Linux                                    |    |

|   |                 | ENDOR REQUESTS                           |    |

|   | 6.3.1           | VR_CLEAR_FPGA                            |    |

|   | 6.3.2           | VR_SETUP_CONFIG                          |    |

|   | 6.3.3           | VR_END_CONFIG                            |    |

|   | 6.3.4           | VR_SET_EP6TC (Read buffer size)          |    |

|   | 6.3.5           | VR_MEM_MAPPED (Configuration Registers)  | 73 |

|   | 6.3.6           | Other Vendor Requests                    |    |

|   | 6.4 M           | AIN BUS ACCESSES                         | 73 |

|   | 6.4.1           | Important Note About Endpoints           |    |

|   | 6.4.2           | Performance                              |    |

|   |                 | PGA CONFIGURATION                        |    |

|   | 6.5.1           | Readback                                 |    |

|   | 6.6 US<br>6.6.1 | SB HARDWARE                              |    |

|   | 6.6.2           | Activity LED                             |    |

|   | 6.6.3           | Configuration FPGA                       |    |

|   | 6.6.4           | Power                                    |    |

|   |                 | COUBLESHOOTING                           |    |

|   | 6.7.1           | USB Controller Freezes                   | 77 |

|   | 6.7.2           | Main Bus always returns 0x (Error Codes) | 77 |

| 7 | PCI EX          | XPRESS INTERFACE                         | 77 |

|   |                 | -                                        |    |

|   | 7.1 EL          | ECTRICAL                                 | 70 |

| 7.3<br>7.4                                     | HOST INTERFACE, MECHANICAL                                                                                                                        |          |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                | IUSABLE PINS                                                                                                                                      |          |

|                                                |                                                                                                                                                   |          |

| 8.1.                                           |                                                                                                                                                   |          |

| 8.1.<br>8.1.                                   | 5.8                                                                                                                                               |          |

| 8.1.                                           |                                                                                                                                                   |          |

| 8.2                                            | EXTENDED MB                                                                                                                                       |          |

|                                                | STEM MONITOR/ADC                                                                                                                                  |          |

|                                                |                                                                                                                                                   |          |

| 10 R                                           | RESET                                                                                                                                             |          |

| 10.1                                           | Power Reset                                                                                                                                       |          |

| 10.2                                           | USER RESET                                                                                                                                        | 83       |

| 11 J                                           | JTAG                                                                                                                                              | 83       |

| 11.1                                           | FPGA JTAG                                                                                                                                         | 83       |

| 11.1                                           |                                                                                                                                                   |          |

| 11.1                                           | 1.2 Identify                                                                                                                                      | 85       |

| 11.1                                           | 1 1                                                                                                                                               |          |

| 11.2                                           | FIRMWARE UPDATE HEADER                                                                                                                            |          |

| 11.3                                           | ETHERNET JTAG                                                                                                                                     |          |

| 11.4                                           | TROUBLESHOOTING                                                                                                                                   |          |

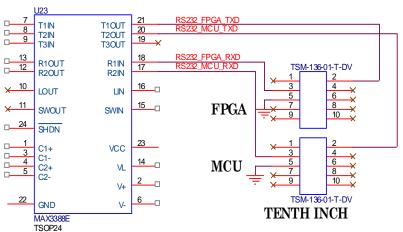

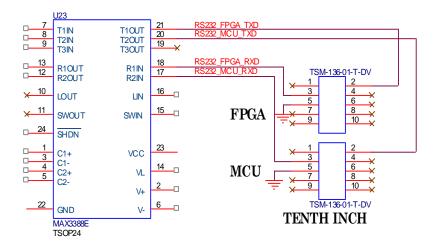

| 12 R                                           | RS232 INTERFACE                                                                                                                                   | 85       |

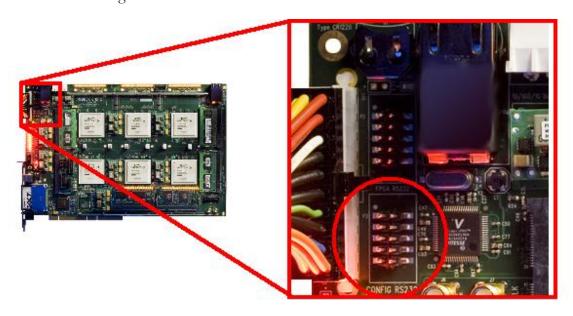

| 12.1                                           | 1.1 Configuration RS232                                                                                                                           | 86       |

| 13 T                                           | TEMPERATURE SENSORS                                                                                                                               | 87       |

| 14 E                                           | ENCRYPTION BATTERY                                                                                                                                | 87       |

|                                                |                                                                                                                                                   |          |

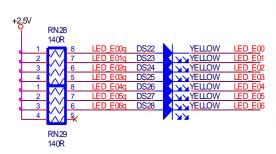

| 15 L                                           | LED INTERFACE                                                                                                                                     |          |

| 15.1                                           | CONFIGURATION SECTION LEDS                                                                                                                        | 89       |

| 15.2                                           | User LEDs                                                                                                                                         |          |

| 15.3                                           | ETHERNET LEDS                                                                                                                                     |          |

| 15.4<br>15.5                                   | POWER LEDS                                                                                                                                        |          |

|                                                |                                                                                                                                                   |          |

| 16 D                                           | DDR2                                                                                                                                              | 92       |

| 16.1                                           | Power                                                                                                                                             | 93       |

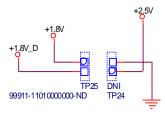

|                                                | 1.1 Interface Voltages                                                                                                                            | 93       |

| 16.1                                           |                                                                                                                                                   |          |

| 16.2                                           | CLOCKING                                                                                                                                          |          |

| 16.3                                           | SIGNALING                                                                                                                                         |          |

| 16.3<br>16.3                                   |                                                                                                                                                   |          |

| 16.3                                           | 3                                                                                                                                                 | 90       |

|                                                |                                                                                                                                                   | 07       |

| 16.4                                           | COMPATIBLE MODULES                                                                                                                                |          |

| 16.4<br>16.5                                   |                                                                                                                                                   | 97       |

| 16.5                                           | COMPATIBLE MODULES                                                                                                                                | 97<br>98 |

| 16.5<br><b>17 F</b>                            | COMPATIBLE MODULES                                                                                                                                |          |

| 16.5<br><b>17 F</b>                            | COMPATIBLE MODULES TEST POINTS  FPGA INTERCONNECT.  MAIN BUS                                                                                      |          |

| 16.5  17 F  18 N  18.1                         | COMPATIBLE MODULES TEST POINTS  FPGA INTERCONNECT.  MAIN BUS  MB Signals                                                                          |          |

| 16.5  17 F  18 N  18.1  18.1                   | COMPATIBLE MODULES TEST POINTS  FPGA INTERCONNECT.  MAIN BUS  MB SIGNALS  1.1 Disambiguation                                                      |          |

| 16.5  17 F  18 M  18.1  18.1  18.1             | COMPATIBLE MODULES TEST POINTS  FPGA INTERCONNECT.  MAIN BUS  MB SIGNALS  1.1 Disambiguation 1.2 Electrical                                       |          |

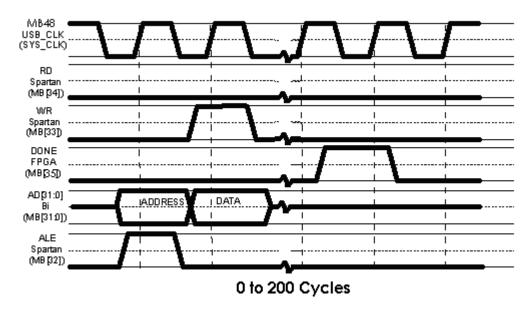

| 16.5  17 F  18 M  18.1  18.1  18.1  18.1       | COMPATIBLE MODULES TEST POINTS  FPGA INTERCONNECT.  MAIN BUS  MB SIGNALS  1.1 Disambiguation. 1.2 Electrical. 1.3 Timing.                         |          |

| 16.5  17 F  18 M  18.1  18.1  18.1             | COMPATIBLE MODULES TEST POINTS  FPGA INTERCONNECT.  MAIN BUS  MB SIGNALS  1.1 Disambiguation 1.2 Electrical.  1.3 Timing                          |          |

| 16.5  17 F  18 M  18.1  18.1  18.1  18.1  18.1 | COMPATIBLE MODULES TEST POINTS  FPGA INTERCONNECT.  MAIN BUS  MB SIGNALS  1.1 Disambiguation 1.2 Electrical 1.3 Timing 1.4 FPGA Stuffing Options. |          |

| 19 | ETI              | ERNET                                                                       | 105 |

|----|------------------|-----------------------------------------------------------------------------|-----|

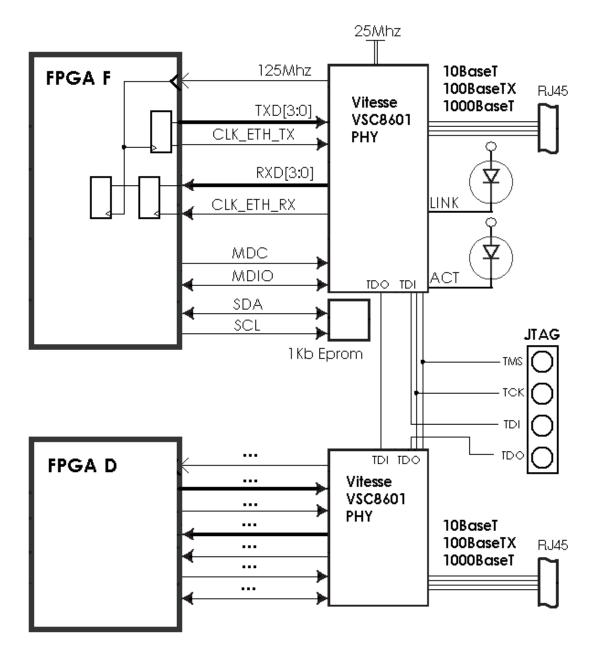

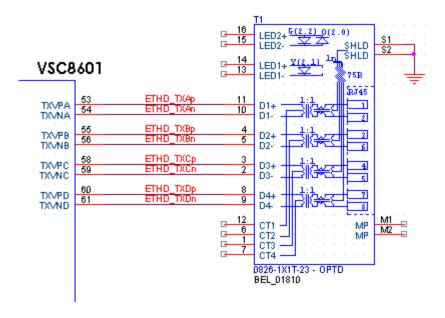

|    | 19.1             | MII                                                                         | 106 |

|    | 19.1.1           | Electrical                                                                  | 106 |

|    | 19.1.2           | Timing                                                                      |     |

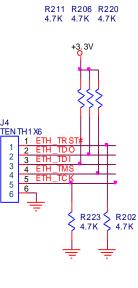

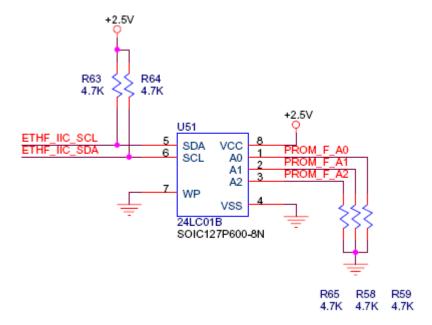

|    | 19.2             | JTAG                                                                        | 109 |

| 20 | EPF              | OM                                                                          | 109 |

| 21 | POV              | VER                                                                         | 110 |

|    | 21.1             | 12V                                                                         |     |

|    | 21.1<br>21.2     | 3.3V                                                                        |     |

|    | 21.2             | 2.5V                                                                        |     |

|    | 21.4             | GROUND                                                                      |     |

|    | 21.5             | VOLTAGE REGULATION                                                          |     |

|    | 21.6             | Power Connections                                                           | 111 |

|    | 21.7             | Power Monitors                                                              | 113 |

|    | 21.8             | Heat                                                                        |     |

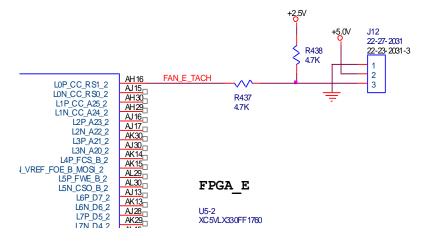

|    | 21.8.1           | Fans                                                                        |     |

|    | 21.8.2           | Removing Heatsinks                                                          |     |

|    | 21.8.3           | Fan Tachometers                                                             |     |

| 22 | CO               | INECTORS                                                                    | 115 |

|    | 22.1             | FPGA USER INTERFACE CONNECTORS                                              | 115 |

| •  | 22.1<br>22.1.1   | Comments                                                                    |     |

|    | 22.7.7           | Non-FPGA User Interface Connectors                                          |     |

|    | 22.2.1           | Comments                                                                    |     |

|    | 22.3             | Not-For-Use Connectors                                                      |     |

|    | 22.3.1           | Comments                                                                    | 117 |

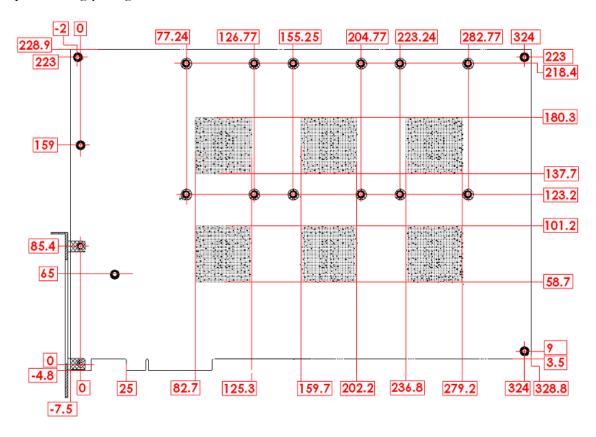

| 23 | ME               | CHANICAL                                                                    | 117 |

| 23 | WIL              | MANCAL                                                                      | 11/ |

| 24 | DA               | GHTERCARD HEADERS                                                           | 119 |

|    | 24.1             | DAUGHTER CARD PHYSICAL                                                      | 120 |

|    | 24.1.1           | Daughter Card Locations and Mounting                                        |     |

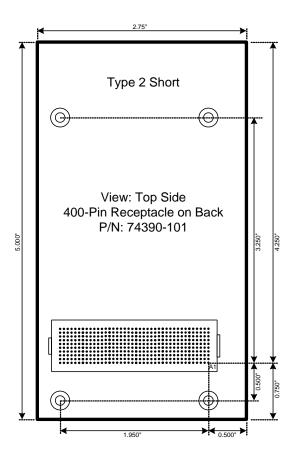

|    | 24.1.2           | Types 2 Short (400pin Short)                                                |     |

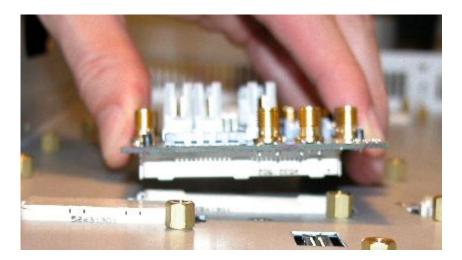

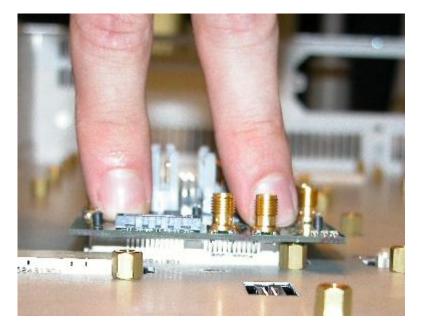

|    | 24.1.3           | Insertion and removal                                                       |     |

|    | 24.2             | DAUGHTER CARD ELECTRICAL                                                    |     |

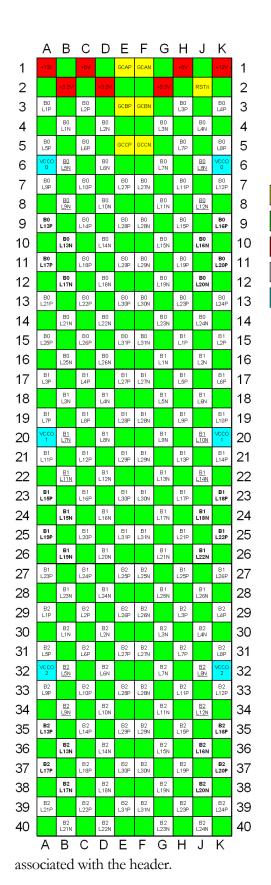

|    | 24.2.1           | Pin assignments                                                             |     |

|    | 24.2.2           | CC, VREF, DCI.                                                              |     |

|    | 24.2.3<br>24.2.4 | Global clocks<br>Timing and Clocking                                        |     |

|    | 24.2.5           | Power and Reset.                                                            |     |

|    | 24.2.6           | VCCO Voltage                                                                |     |

|    | 24.2.7           | VCCO bias generation                                                        |     |

|    | 24.3             | ROLLING YOUR OWN DAUGHTERCARD                                               |     |

| 25 | TRO              | UBLESHOOTING                                                                | 129 |

|    |                  |                                                                             |     |

|    | 25.1             | THE BOARD IS DEAD                                                           |     |

|    | 25.2             | THE FPGAS WON'T PROGRAM                                                     |     |

|    | 25.3             | MY DESIGN DOESN'T DO ANYTHING                                               |     |

|    | 25.4<br>25.5     | THE DCMS WON'T LOCKTHE SIGNAL ON MY BOARD IS GOING CRAZY ON MY OSCILLOSCOPE |     |

|    |                  |                                                                             |     |

| CI | IAPTER           | 5: THE REFERENCE DESIGN                                                     | 133 |

| 1  | WHA              | THE REFERENCE DESIGN DOES                                                   | 133 |

|    | 1.1 E            | XAMPLE USAGE OF ALL INTERFACES                                              | 133 |

|    |                  | FERENCE DESIGN TYPES                                                        |     |

|    |                  | SING THE REFERENCE DESIGN                                                   | 135 |

| 2  | DEFE             | RENCE DESIGN MEMORY MAP                                                     | 125 |

| 4  | KEFE             | NENCE DESIGN MEMUKI MAY                                                     | 135 |

| 2  | INTER            | CONNECT (DC)                                                                | 127 |

|              | 3.1 USING THE DESIGN                                                                                                 |      |

|--------------|----------------------------------------------------------------------------------------------------------------------|------|

|              | 3.2 RUNNING THE TEST                                                                                                 | 138  |

| 4            | 4 DDR2 INTERFACE                                                                                                     | 138  |

|              | 4.1 Provided Files                                                                                                   | 138  |

|              | 4.2 Using the Design                                                                                                 |      |

|              | 4.3 RUNNING THE TEST                                                                                                 |      |

| 5            | 5 CLOCK COUNTERS                                                                                                     | 130  |

|              |                                                                                                                      |      |

| 6            | 6 LEDS                                                                                                               | 139  |

| 7            | 7 SIMULATING THE REFERENCE DESIGN                                                                                    | 139  |

| 8            | 8 COMPILING THE REFERENCE DESIGN                                                                                     | 140  |

|              | 8.1.1 The Xilinx Embedded Development Kit (EDK)                                                                      |      |

|              |                                                                                                                      |      |

|              |                                                                                                                      |      |

|              |                                                                                                                      |      |

|              | 8.2 BITGEN OPTIONS                                                                                                   |      |

|              |                                                                                                                      |      |

| 9            |                                                                                                                      |      |

|              | 9.1 Provided Files                                                                                                   | 142  |

|              | 9.2 USING THE DESIGN                                                                                                 |      |

|              | 9.3 RUNNING THE TEST                                                                                                 | 142  |

| 10           | 10 ETHERNET AND PCI EXPRESS DESIGN                                                                                   | 142  |

|              |                                                                                                                      |      |

| $\mathbf{C}$ | CHAPTER 6: ORDERING INFORMATION                                                                                      | 145  |

|              |                                                                                                                      |      |

| 1            | 1 SECTION TITLE                                                                                                      | 145  |

| 2            | 2 FPGA OPTIONS                                                                                                       | 1.45 |

| 4            |                                                                                                                      |      |

|              | 2.1 FPGA A-F:                                                                                                        |      |

|              | 2.2 CES PARTS                                                                                                        |      |

|              | 2.2.1 Hardware Errata Details                                                                                        |      |

|              | 2.4 SPEED GRADES                                                                                                     |      |

|              | 2.5 UPGRADE POLICY                                                                                                   |      |

| •            |                                                                                                                      |      |

| 3            |                                                                                                                      |      |

|              | 3.1 COMPATIBLE DINI GROUP PRODUCTS                                                                                   |      |

|              |                                                                                                                      |      |

|              | 3.1.2 Extenders                                                                                                      |      |

|              | 3.2 COMPATIBLE THIRD-PARTY PRODUCTS                                                                                  |      |

| 4            |                                                                                                                      |      |

|              |                                                                                                                      |      |

|              | 4.1 COMPLIANCE                                                                                                       |      |

|              | 4.1.1 EMI                                                                                                            |      |

|              |                                                                                                                      |      |

|              | 4.1.2 PCI-SIG                                                                                                        |      |

|              | 4.1.2 PCI-SIG                                                                                                        |      |

|              | 4.1.2       PCI-SIG         4.2       ENVIRONMENTAL         4.2.1       Temperature                                  |      |

|              | 4.1.2       PCI-SIG         4.2       ENVIRONMENTAL         4.2.1       Temperature         4.3       EXPORT CONTROL |      |

|              | 4.1.2 PCI-SIG                                                                                                        |      |

|              | 4.1.2 PCI-SIG                                                                                                        |      |

# Introduction

Congratulations on your purchase of the DN9000K10PCIE4GL logic emulation board. If you are unfamiliar with Dini Group products, you should read Chapter 2, Quick Start Guide to familiarize yourself with the user interfaces the DN9000K10PCIE4GL provides.

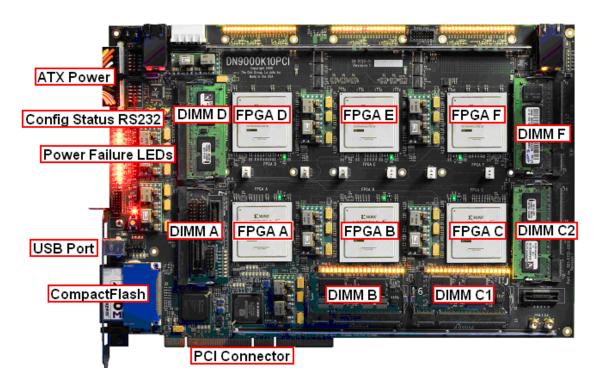

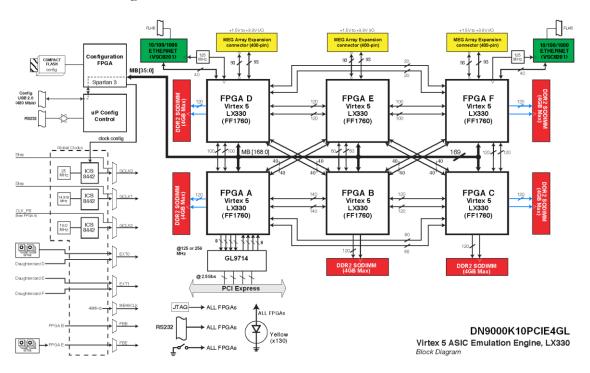

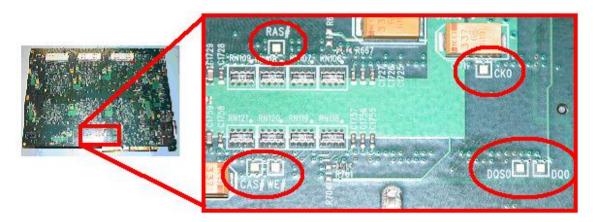

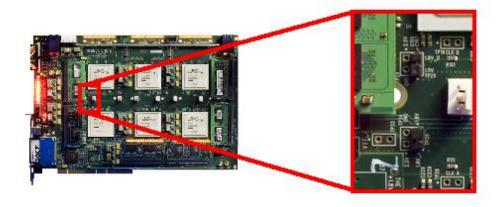

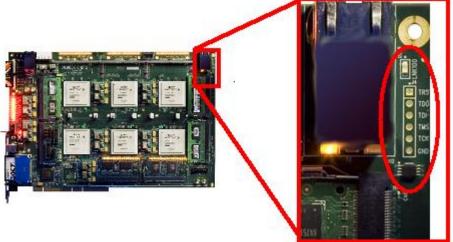

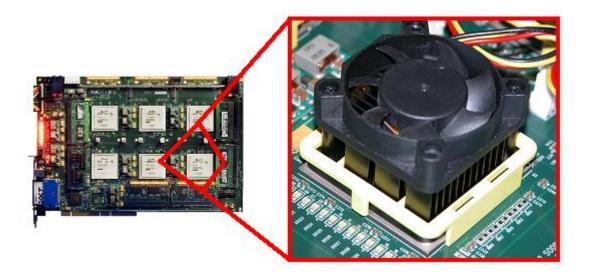

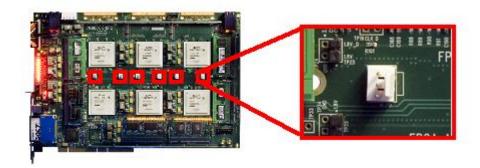

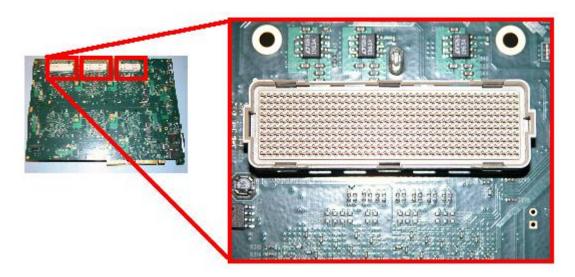

Figure 1 DN9000K10PCIE4GL – shown with optional memory modules installed; User LEDs, power fail LEDs, and Gigabit activity LEDs all glowing inexplicably. Heatsinks negligently left uninstalled.

# 1 Manual Contents

This manual contains the following chapters:

#### Introduction

Reader's Guide to this manual; List of available documentation and resources available.

## **Quick Start Guide**

Step-by-step instructions for powering on the DN9000K10PCIE4GL, loading and communicating with a simple, provided FPGA design, and using the board's common control features.

#### **Controller Software**

A summary of the functionality of the provided software. Implementation details for the remote USB board control functions and instructions for developing your own USB host software.

#### **Hardware**

Detailed description and operating instructions of each individual circuit on the DN9000K10PCIE4GL, a description of each user-accessible interface and user features.

# The Reference Design

Detailed description of the provided DN9000K10PCIE4GL reference design. Implementation details of the reference design interaction with DN9000K10PCIE4GL hardware features.

# **Ordering Information**

Contains a list of the available options and available optional equipment. Some suggested parts and equipment available from third party vendors. Compatibility lists.

# 2 Conventions

This document uses the following conventions. An example illustrates each convention.

# 2.1 Typographical

The following typographical conventions are used in this document:

| Convention      | Meaning or Use                 | Example                                  |

|-----------------|--------------------------------|------------------------------------------|

| Prefix "0x"     | Indicates hexadecimal notation | Read from address 0x00110373, returned   |

| Letter "#", "N" | Signal is active low           | INT# is active low<br>RSTn is active low |

#### 2.2 Manual Content

#### 2.2.1 File names

Paths to documents included on the User CD are prefixed with "D:\". This refers to your CD drive's root directory when the User CD is inserted in your Windows computer.

Alternately, copy the entire contents of the User CD to your hard drive, and allow D:\ to refer to this path. Due to limitations of the Xilinx ISE software, we recommend a path without space characters in it. (Bad places include C:/Documents and Settings/username/Desktop/)

#### 2.2.2 Physical Dimensions

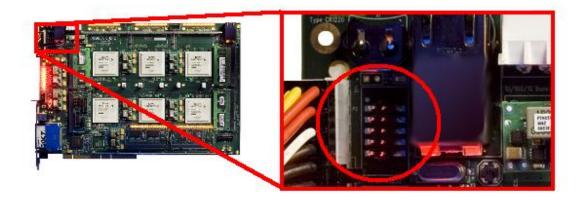

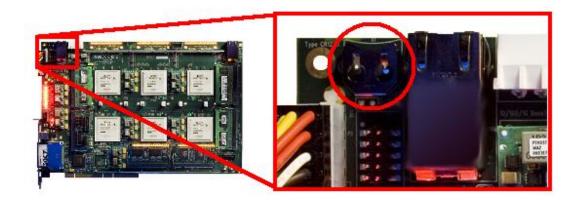

By convention, the board is oriented as shown in the above board photo, with the "top" of the board being the edge near FPGA D, E, and F with daughtercard headers. The "right" edge is near FPGA C and F. The "left" side is the side with the PCI bezel. "Top" side refers to the side of the PWB with FPGAs and fans; the "back" side is the side with the daughtercard connectors.

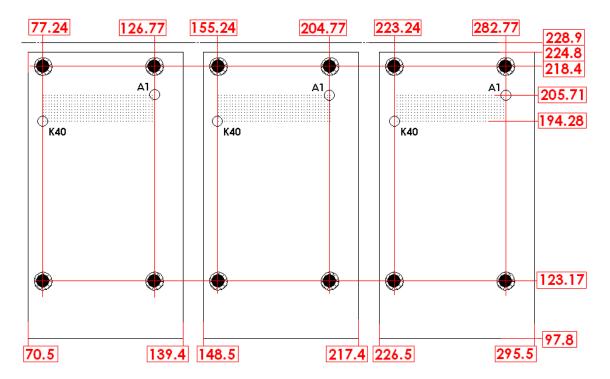

The reference origin of the board is the center of the lower PCI bezel mounting hole. Physical dimensions are given in millimeters.

#### 2.2.3 Part Pin Names

References to individual part's pin are given in the form  $\langle X \rangle \langle Y \rangle$ .  $\langle Z \rangle$ ; The  $\langle X \rangle$  is one of: U for ICs, R for resistors, C for capacitors, P or J for connectors, FB or L for inductors, TP for test points, MH for mounting structures, FD for fiducials, BT for sockets, DS for displays (light-emitting diodes), F for fuses, PSU for power supply modules, Q for discreet semiconductors, RN for resistor networks, G for oscillators, X for sockets, Y for crystals and the PCI bezel.  $\langle Y \rangle$  is a number uniquely identifying each part from other parts of the same class.  $\langle Z \rangle$  is the pin or terminal number or name, as defined in the datasheet of the part. Datasheets for all standard and optional parts used on the DN9000K10PCIE4GL are included in the Document library on the user CD.

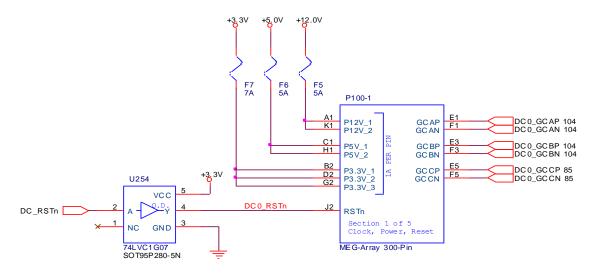

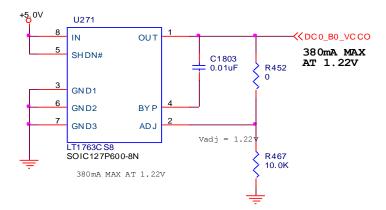

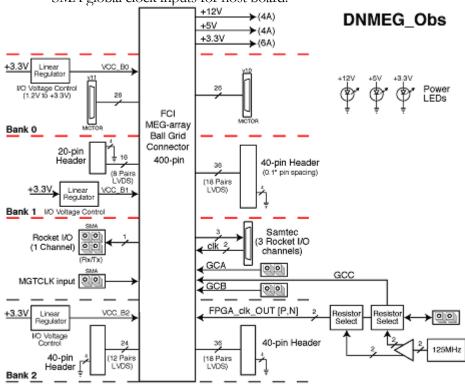

#### 2.2.4 Schematic Clippings

Partial schematic drawings are included in this document to aid quick understanding of the features of the DN9000K10PCIE4GL. These clippings have been modified for clarity and brevity, and may be missing signals, parts, net names and connections. Unmodified Schematics are included in the User CD as a PDF. *Please refer to this document when designing an interface in the FPGA*. Use the PDF search feature to search for nets and parts.

# 2.3 Terminology

Abbreviations and pronouns are used for some commonly used phrases. The user is assumed to know the meaning of the following:

#### Spartan

Spartan refers to the Spartan-3 FPGA device used by the DN9000K10PCIE4GL to perform configuration circuit functions. It is used interchangeably with "configuration circuit"

#### DCM, DLL, PLL

"Digital Clock Manager" or "Digitally-locked-loop". This is a clock synthesis module in a Virtex-5 FPGA. PLL is "Phase-locked-loop". See Xilinx documentation.

#### **LVDS**

"Low-Voltage differential signaling". A signaling standard with a 1.2V DC, and 300mV AC level. In this manual and in advertisements, LVDS is often used where "Differential Signal" should be used instead.

#### Net, Signal, Plane, rail

A net is an electrically continuous piece of conductor on the PCB before assembly. Signal can refer to an electrically continuous conductor on the PCB, or to the logical meaning of that net. Plane is a net for voltage sources. Rail is also used to mean a power net.

#### GND, ground, grounded

GND is a net on the DN9000K10PCIE4GL, to which all voltages are referenced. "Ground" is

equivalent". Grounded means "connected to GND". There is a single ground net on the  ${\rm DN}9000{\rm K}10{\rm PCIE4GL}$

# 3 Resources

The following electronic resources will help you during development with your board.

## 3.1 User CD

The User CD contains all the electronic documents required for you to operate the DN9000K10PCIE4GL. These include schematics, the user manual, FPGA reference designs, and datasheets. The directory structure of the CD is as follows

| 3rdPartySoftware\Acrobat Reader 7.0\                                          | Required to read .pdf documents (Windows)                                                                                                                    |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Config_Section_Code\                                                          | The DN9000K10PCIE4GL firmware source                                                                                                                         |

| ConfigFPGA\ MCU\                                                              | These sources are not intended to be used for development.                                                                                                   |

| Datasheets\                                                                   | A datasheet for every part used on the board. You will need these to interface successfully with resources on the DN9000K10PCIE4GL.                          |

| Documentation\Manual\                                                         | Contains this document                                                                                                                                       |

| FPGA_Reference_Designs\ common\ DN9000K10PCIE4GL\ Programming_Files\ certify\ | Contains the source and compiled programming files for the Dini group's DN9000K10-PCI reference design. Also, board description files and simulation models. |

| PCI_Software_Applications\Aetest\                                             | Source and binaries for the provided PCI-hosted controller software.                                                                                         |

| Schematics\Rev1\                                                              | Contains a PDF version of the board schematic. Search the PDF using control-F                                                                                |

| USB_Software_Applications\ driver\ USB_CMD_Line_AETEST_USB\ USBController\    | Contains source and binaries for the provided USB-hosted controller applications.                                                                            |

# 3.2 Dinigroup.com

The most recent versions of the following documents are found on the product web page http://dinigroup.com/DN9000k10PCIe4GL.php

User's Manual (this document) Certify Board Description File Errata USB Controller executable

#### 3.3 Errata and Customer Notifications

The Errata sheet (available at www.dinigroup.com) lists all cases where the DN9000K10PCIE4GL is found to have failed to meet advertised specifications, or where an error in schematics or documentation is likely to cause a difficult-to-debug error by the user.

The customer is notified when there is an update to the Errata list after the board is shipped. Customers are not notified when changes are made to other documents including the reference design, USB Controller and User Manual. These documents change or a weekly basis or faster. You may always request a duplicate User CD. We will also be happy to provide the latest version of documents via email to customers.

As of May 23, 2007, there were no errata for this product.

#### 3.4 Schematics and Netlist

Unmodified Schematics are included in the User CD as a PDF. Use the PDF search feature to search for nets and parts.

#### 3.4.1 Netlist

In leiu of providing a machine-readable version of the schematic, the Dini Group provides a text netlist of the board. This netlist contains all nets on the board that connect to user IO on any FPGA. When interfacing with any device or connector on the DN9000K10PCIE4GL you should use either the provided ucf, or the netlist to generate the pinout. The netlist is located on the user CD at

D:\Schematics\Rev 01\DN9000K10PCIE4GL customer netlist.net

#### 3.4.2 Net name conventions

All "power" nets begin with a +, - symbol, or GND

All clock signals begin with "CLK"

Two sides of a differential signal differ by one character "p" or "n". This character is near the end of the net name.

Active low signals end in #. In the provided UCF files, the # is replaced by an "N".

#### 3.5 Datasheet Library

Datasheets for all parts used, or interfaced to, on the DN9000K10PCIE4GL are provided on the user CD. In order to successfully use the DN9000K10PCIE4GL, you will have to reference

these datasheets. The interface descriptions given in this user manual typically end with electrical connectivity.

Especially read the Virtex-5 user guide. The copy provided on the user CD is only recent as of the DN9000K10PCIE4GL product announcement.

#### 3.6 Xilinx

Virtex-5 is a brand-new device, and technical questions about getting the FPGA and ISE software to behave like you expect should be directed to a Xilinx FAE. Also use

WebCase <a href="http://www.xilinx.com/support/clearexpress/websupport.htm">http://www.xilinx.com/support/clearexpress/websupport.htm</a>

AnswerBrowser <a href="http://www.xilinx.com/xlnx/xil">http://www.xilinx.com/xlnx/xil</a> ans browser.jsp

ISE Manual <a href="http://www.xilinx.com/support/sw-manuals/xilinx82/index.htm">http://www.xilinx.com/support/sw-manuals/xilinx82/index.htm</a>

<a href="http://www.xilinx.com/support/sw-manuals/xilinx82/index.htm">http://www.xilinx.com/support/sw-manuals/xilinx82/index.htm</a>

<a href="http://www.xilinx.com/support/sw-manuals/xilinx82/index.htm">http://www.xilinx.com/support/sw-manuals/xilinx82/index.htm</a>

<a href="http://www.xilinx.com/support/sw-manuals/xilinx82/index.htm">http://www.xilinx.com/support/sw-manuals/xilinx82/index.htm</a>

<a href="http://www.xilinx.com/xlnx/xweb/xil-publications-display.jsp">http://www.xilinx.com/xlnx/xweb/xil-publications-display.jsp</a>

# 3.7 Dini Group Reference Designs

The source code to the reference designs are on the User CD. Please copy and use any code you would like. The reference designs themselves are not deliverables, and as such receive limited support.

#### 3.8 Board Models

Certify board models and other simulation models for the DN9000K10PCIE4GL are provided on the user CD.

D:\FPGA\_Reference\_Designs\DN9000K10PCIE4GL\certify

#### 3.8.1 Base System Builder

We don't have a system builder file. As us if we can make one.

# 4 Email and Phone Support

Dini Group technical support for products can be reached via email at <a href="support@dinigroup.com">support@dinigroup.com</a>. Our phone number is (USA) 858-454-3419. Please do not send .exe files, .vb files, or .zip files containing other .zip files as attachments, as we will not receive these emails. Please include the board's serial number in your email. This will allow us to reference our records regarding your board.

Before contacting support you should complete the following:

- 1) Follow the debugging steps in the troubleshooting sections at the end of the hardware chapter, and in any applicable interface sections.

- 2) Test the applicable interface(s) using the provided software and .bit files, to help rule out hardware failures.

# **Quick Start Guide**

The Dini Group DN9000K10PCIE4GL can be used and controlled using many interfaces. In order to learn the use of the most fundamental interfaces of the board (FPGA Configuration, USB data movement, etc.) please follow the instructions in this quick start guide. The guide will also show you how to run the board's hardware test to verify board functionality. (The board has already been tested at the factory).

# 1 Provided Materials

Examine the contents of your DN9000K10PCIE4GL kit. It should contain:

- DN9000K10PCIE4GL board

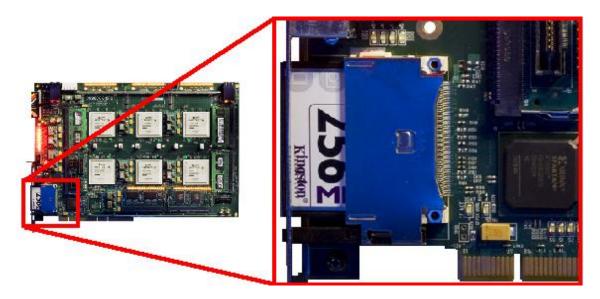

- CompactFlash card containing the FPGA configuration ".bit" files required to run the hardware test.

- USB CompactFlash card reader

- RS232 IDC header cable to female DB9

- A "Hard Drive-to-PCI express" power cable adapter

- USB cable, black.

- CD ROM containing:

- Virtex 5 Reference Designs

- User manual PDF

- Board Schematic PDF

- USB program (usbcontroller.exe)

- PCI program (Aetest.exe)

- Source code for USB program, PCI program and DN9000K10PCIE4GL firmware

- Board netlist, certify model, and QL5064 simulation model

#### 1.1 System Requirements

To compile Verilog designs for Virtex 5, ISE 8.2 (service pack 3 or later) is required. For some LX330 designs, you may need a Linux machine with a 64-bit processor and 6GB of RAM or greater. (Windows XP limits memory to 3GB)

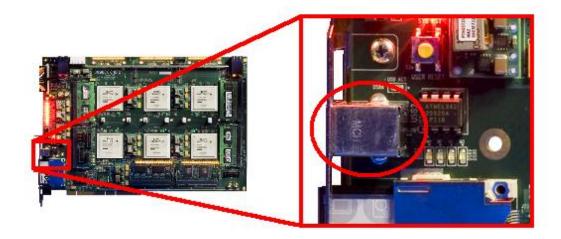

To use the provided controller software, you need any Windows XP computer with USB 2.0.

To receive firmware updates to the DN9000K10PCIE4GL, you need a JTAG programming cable from Xilinx. Having this cable is basically mandatory, otherwise you would need to ship the board back to us to enable features or correct firmware bugs. You probably need a JTAG cable anyway for using embedded debugging software. We recommend the Xilinx Platform USB cable over their Parallel IV, because it sucks less.

# 2 Warnings

#### 2.1 **ESD**

The DN9000K10PCIE4GL is sensitive to static electricity, so treat the PCB accordingly. The target markets for this product are engineers that are familiar with FPGAs and circuit boards. However, if needed, the following web page has an excellent tutorial on the "Fundamentals of ESD" for those of you who are new to ESD sensitive products:

http://www.esda.org/basics/part1.cfm

There are two large grounded metal rails on the DN9000K10PCIE4GL. The user should handle the board using these rails, as they are much less ESD sensitive than any other point on the board.

The 400-pin connectors are not 5V tolerant. No exposed surfaces on the board, except for the PCI edge connector are tolerant of voltages greater than 4V. According to the Virtex 5 datasheets, the maximum applied voltage to any IO signals on the FPGA is VCCO. This means you should not try to over-drive IOs in an FPGA interface above the interface voltage specified in this manual.

#### 2.2 Other

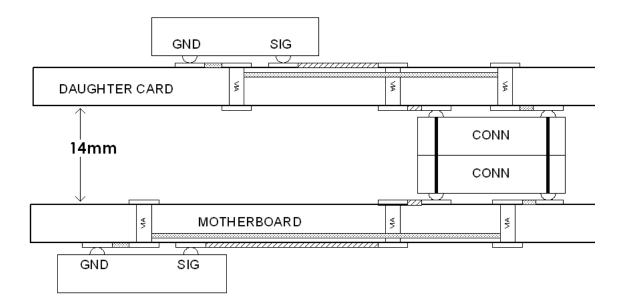

Some parts of the board are physically fragile. Take extra care when handling the board to avoid touching the daughtercard connectors. Leave the covers on the daughtercard connectors whenever they are not in use. Use mounting hardware to secure daughtercards.

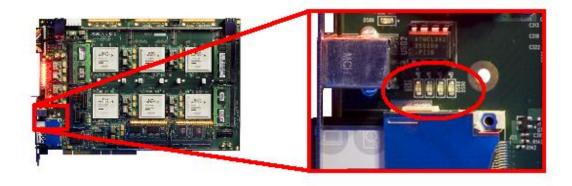

# 3 Pre-Power On Instructions

The image below represents your DN9000K10PCIE4GL. You will need to know the location of the following parts referenced in this chapter.

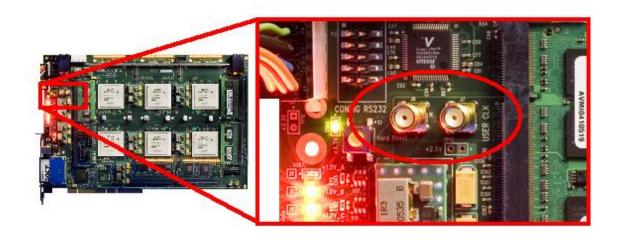

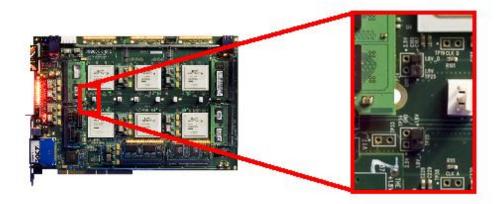

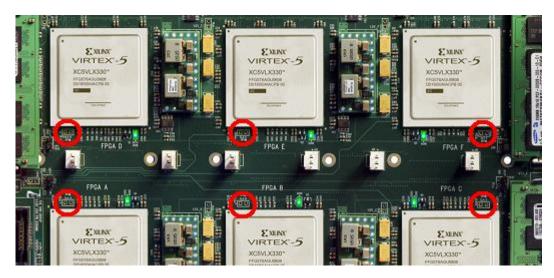

Figure 2 DN9000K10PCIE4GL configuration controls

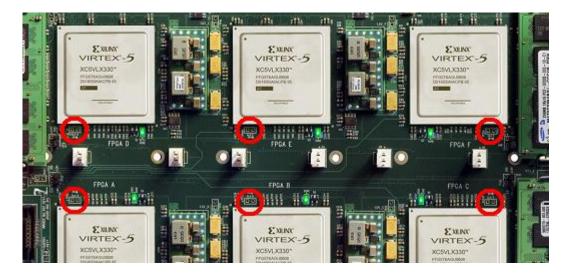

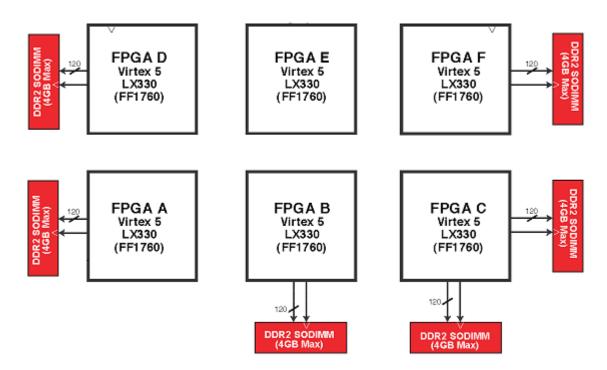

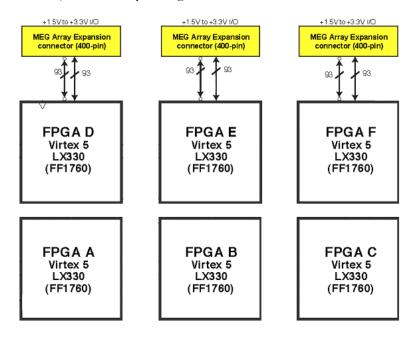

The FPGAs on the board are names "FPGA A" through "FPGA F" FPGA A is in the lower left hand corner as shown in the above photo. FPGA B and C are to its right. The top row of FPGAs from left to right are named, "FPGA D", "FPGA E", and "FPGA F"

To begin working with the DN9000K10PCIE4GL, follow the steps below.

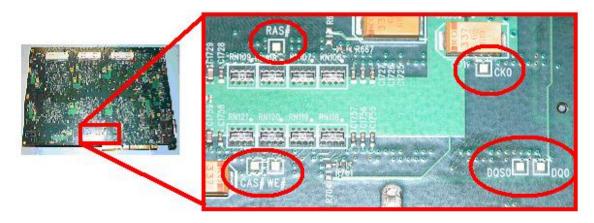

# 3.1 Install Memory

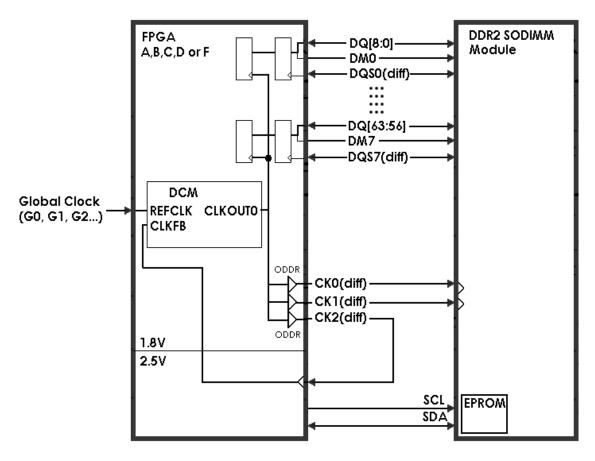

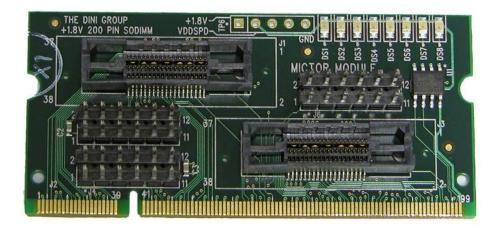

The DN9000K10PCIE4GL comes packaged without memory installed. If you want the Dini Group reference design to test your memory interfaces, you must install memory modules in the SODIMM slots on the board. The reference design supports DDR2 SODIMM modules in densities 256MB, 512MB, and 1GB with a CAS latency of 3. (Almost any modern off-the-shelf laptop memory)

The socket DIMMB is connected to FPGA B. The socket can accept any capacity DDR2 SODIMM module. Note that DDR1 modules will not work in these slots since they are a completely different pin-out and voltage level.

# 3.2 Prepare configuration files

The DN9000K10PCIE4GL reads FPGA configuration data from a CompactFlash card. To program the FPGAs on the DN9000K10PCIE4GL, FPGA design files (with a .bit file extension) put on the root directory of the CompactFlash card file using the provided USB card reader.

The DN9000K10PCIE4GL ships with a 256MB CompactFlash card preloaded with the Dini Group reference design. These "bit" files can also be found on the User CD. You can also compile the reference design source (provided on the CD) and place the generated .bit files on the Compact Flash card.

1. Insert the provided CompactFlash card labeled "Reference Design" into your USB card reader. Make sure the card contains the files:

```

FPGA_A.bit

FPGA_B.bit

FPGA_C.bit

FPGA_D.bit

FPGA_E.bit

FPGA_F.bit

main.txt

```

The files FPG\_A-F.bit are files created by the Xilinx program bitgen, part of the ISE 8.2 tools. The file main.txt contains instructions for the DN9000K10PCIE4GL configuration circuitry, including which FPGAs to configure, and to which frequency the global clock networks should be automatically adjusted.

2. Take a look at the contents of main.txt. It might look something like this:

```

// Main.txt file for the DN9000K10PCIE4GL

FPGA A: fpga_a.bit

FPGA B: fpga_b.bit

FPGA C: fpga_c.bit

FPGA D: fpga_d.bit

FPGA E: fpga_e.bit

FPGA F: fpga_f.bit

clock frequency: G0 350Mhz //LVDS frequency

clock frequency: G1 250Mhz //DDR2 frequency

clock frequency: G2 200Mhz //LVDS IDELAYCTRL

//COMMENT TIME!

```

If you feel adventurous, you can change the clock frequencies by editing the main.txt file. Or you could cause an FPGA to not configure, buy removing it's corresponding line.

3. Insert the CompactFlash card into the DN9000K10PCIE4GL's CompactFlash slot.

# 3.3 Install DN9000K10PCIE4GL in computer (Optional)

If you are not using the DN9000K10PCIE4GL in a PCIe slot, skip this step. You may instead choose to host the DN9000K10PCIE4GL over USB.

#### QUICK START GUIDE

The DN9000K10PCIE4GL can be used with any sized PCIe slot. If you are using a 1x or 2x (does 2X exist?) slot, you will need an adapter card to physically fit.

Try buying there here: <a href="http://www.getcatalyst.com">http://www.getcatalyst.com</a> PEA1621

The board will work in a 8X or 16X slot, although PCI express may revert to 1x mode in this case

This quick-start guide does not test the PCI express bus, and the DN9000K10PCIE4GL does not receive power from this slot. Therefore, placing a board in a PCI Express slot is really just using the PCI express slot as a place to put the board while we play with it.

#### 3.4 Cables

#### 3.4.1 Connect RS232 Cable

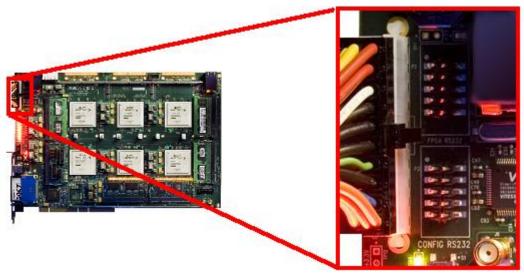

The configuration circuit displays status messages to an RS232 terminal. If (when) something goes wrong with configuration, this terminal will output error messages. Normally, you would only connect this cable when something is not working and you want to debug the problem.

Use the provided ribbon cable to connect the MCU RS232 port (P2) to a computer serial port to view feedback from the configuration circuitry during FPGA configuration. Run a serial terminal program on your PC (On Windows you can use HyperTerminal Start->Programs->Accessories->Communications->HyperTerminal) and make sure the computer serial port is configured with the following options:

- Bits per second: 19200

- Data bits: 8

- Parity: None

- Stop Bits: 1

- Flow control: None

- Terminal Emulation: VT100 (or None, if available)

#### 3.4.2 Connect USB Cable

Use the provided USB cable to connect the DN9000K10PCIE4GL to a Windows computer (Windows XP is recommended).

If your board is installed in a PCI slot, the USB host is allowed to be the same computer as the non-USB host. The two computers should be connected to the same power outlet if this is the case.

#### 3.4.3 Connect Power cable

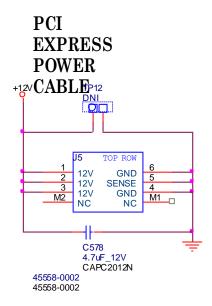

The 6-pin power connector, P5, is required for operation. This is true whether or not the board is plugged into a PCI express slot. The type of power cable that is required is a 6-pin "PCI express graphics power" connector. At least one of these connectors is available on most new

ATX power supplies. For those customers who do not have a new ATX power supply, an adapter cable is provided so that the board can be powered from the 4-pin "hard drive" power connector instead.

Please note that the 4-pin and 8-pin "Molex" connectors coming off your power supply look like they would probably plug in to the 6-pin header on the board. However, if you somehow manage to do this let us assure you that it will result in a seventy-thousand dollar fireball.

# 4 Power On

Turn on the ATX power supply (Table-top USB Hosting) or the computer (PCIe hosting).

Some power supplies require a minimum load on the +5V rail. The DN9000K10PCIe4GL draws no current off this rail. In this case, the power supply may be unstable. You can work around this limitation by plugging a spare hard drive into one of the hard drive power connectors on the supply. Alternately, you could use a power supply with a zero minimum +5V load requirement.

When operating table-top, the power supply may not power on unless pin 14 ("PSON") of the 20-pin "motherboard" connector is connected to ground. This wire is usually green.

When the DN9000K10PCIE4GL powers on, it automatically loads Xilinx FPGA design files (ending with a .bit extension), found on the CompactFlash card in the CompactFlash slot into the FPGAs, using the main.txt file as a guide.

# 4.1 View configuration feedback over RS232

As the DN9000K10PCIE4GL powers on, your RS232 terminal (connected to P2) will display information about the Configuration process. If FPGAs ever fail to configure using the Compact Flash card, this is the best place to look for help.

A typical RS232 power-on session is given below.

| Rebooting from FLASHplease wait                       | This line has to do with the firmware-update mode                                                                                       |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Setting G0<br>N 01 M: 000001000<br>DONE<br>Setting G1 | The board is setting the global clock frequencies according to the main.txt file on the CompactFlash card. The messages here are mostly |

#### QUICK START GUIDE

| N: 01 M: 000001000<br>DONE<br>Setting G2                                                                                                                                                                                                                          | only useful to whoever programmed the firmware                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N: 01 M: 000001000<br>DONE                                                                                                                                                                                                                                        |                                                                                                                                                               |

| =-=- DN9000K10PCIE4GL MCU FLASH BOOT -=-=<br>FPGAS STUFFED<br>A B                                                                                                                                                                                                 | Prints the FPGAs the configuration circuit thinks you have on your board.                                                                                     |

|                                                                                                                                                                                                                                                                   |                                                                                                                                                               |

| COMPACTFLASH INFO<br>MAKER ID: EC<br>DEVICE ID: 75<br>SIZE: 32 MB                                                                                                                                                                                                 | CompactFlash card debugging information.                                                                                                                      |

| FILES FOUND ON COMPACTFLASH CARD FPGA_B.BIT FPGA_A.BIT MAIN~1.TXT MAIN.TXT CONFIGURATION FILES FPGA A: FPGA_A.BIT FPGA B: FPGA_B.BIT                                                                                                                              | This lists the files found on the compact flash card. If this list is wrong there is something wrong with CompactFlash.                                       |

| OPTIONS Message level set to default: 2 Sanity check is set to default: ON N: 00 M: 000001010 DONE Setting G0 N: 01 M: 000001100 DONE Setting G1 N: 01 M: 000001000 DONE                                                                                          | The MCU reads the contents of the file MAIN.TXT and executes each instruction line.  Here the MCU is setting the clocks according to instructions in MAIN.TXT |

| *******CONFIGURING FPGA: A***********************************                                                                                                                                                                                                     | The MCU is configuring FPGA A according to instructions in MAIN.TXT  Debugging information about the .bit file.                                               |

| DONE WITH CONFIGURATION OF FPGA: A  *********CONFIGURING FPGA B********** Performing Sanity Check on Bit File BIT FILE ATTRIBUTES FILE NAME: FPGA_B.BIT FILE SIZE: 003A943B bytes PART: 4vlx100ff151317:05:01 DATA: 2005/07/19 TIME: 17:05:01 Sanity check passed | The MCU is configuring FPGA B according to instructions in MAIN.TXT                                                                                           |

| DONE WITH CONFIGURATION OF FPGA: B TEMPERATURE SENSORS A YES                                                                                                                                                                                                      | The MCU is setting the temperature threshold (Causes the FPGAs to automatically disable when overheating)                                                     |

| B YES                                          |

|------------------------------------------------|

| FPGA Temperature Alarm Threshold: 80 degrees C |

Figure 3 RS232 Output

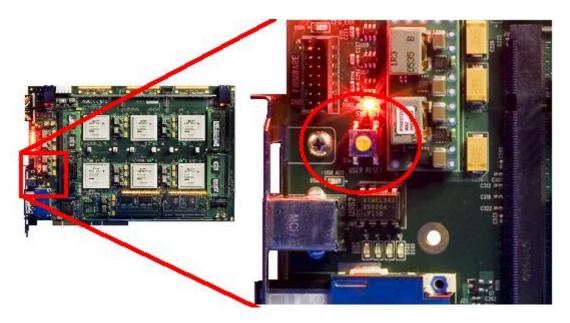

# 4.2 Check LED status lights

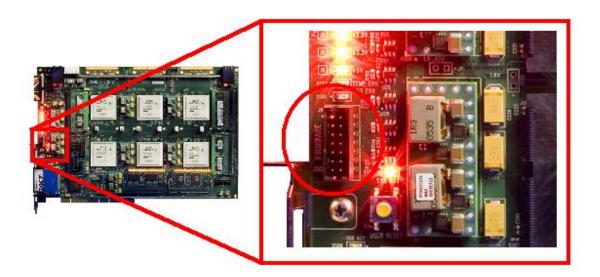

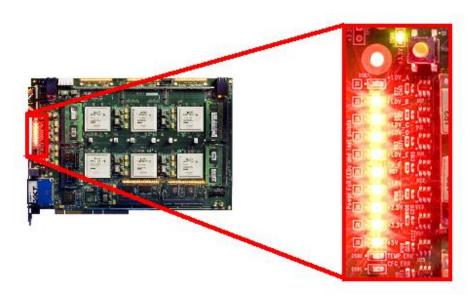

The DN9000K10PCIE4GL has many status LEDs to help the user confirm the status of the configuration process.

- 1. Check the power Failure LEDs to confirm that all voltage rails of the DN9000K10PCIE4GL are within tolerance. If the voltage of any critical power net on the DN9000K10PCIE4GL is too high or too low, the board will be held in reset and at least one of the red LEDs will light. The LEDs are located down the left side of the PCB. Each one is labeled with the voltage that it represents. Normally, all of these LEDs are off. If any of these LEDs light, there is a power problem with the board, and you should contact us. First, make sure that the output of the power supply is acceptable. If the 5V, 3.3V or 12V power fail LED is lit, you probably have a problem with the power supply you are connected to, and not with the DN9000K10PCIE4GL.

- 2. Reset LED. When the board is in reset for any reason, including power failure, or pressing the reset button, this LED will light RED. The LED is located below the RED voltage LEDs next to the logic-reset button.

- 3. Check the Spartan FPGA status LED located near pin 1 of the PCI edge connector. This LED should remain GREEN as long as the board is powered on, except for a quarter second as the board is powering on. This LED indicated the configuration and control FPGA is on. If this LED is not on, it indicates a problem with the board or firmware.

- 4. Check the "DONE" LEDs of each FPGA. When an FPGA is configured, a green LED labeled "DONE" will glow.

- 5. Check the FPGA A status LEDs located just below the FPGA A. These LEDs should be blinky and active if the Dini Group reference design is correctly loaded. Repeat this step for FPGAs B,C,D,E, and F. FPGA B and C LEDs are located just below their respective FPGAs. The LEDs for FPGA D,E and F are located along the top edge of the board.

- Check the CF activity LED, located just below the CompactFlash socket. When

the board is reading off the CompactFlash card during configuration, this LED

should blink.

# **5 Run USB Controller**

This section will get you started with USB and show you how to operate the provided software.

#### 5.1 Driver Installation

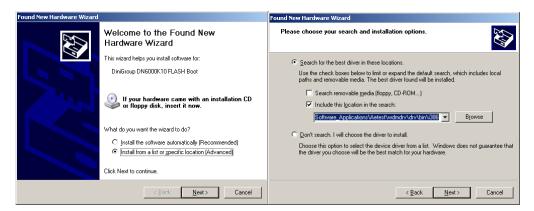

When the DN9000K10PCIE4GL powers on, or you connect it to a USB port for the first time, the computer will ask you to install a driver.

In the window that appears, select "Install from a list or specific location". Select Next.

Click "Include this location in the search" and browse to D:\USB\_Software\_Applications\driver\windows\_wdm Select Next.

In the next window, select the item in the list "Dini Group ASIC Emulator". Click FINISH.

After Windows installs the driver, you will be able to see the following device in the "USB Controllers" group in the Windows device manager: "Dini Group ASIC Emulator".

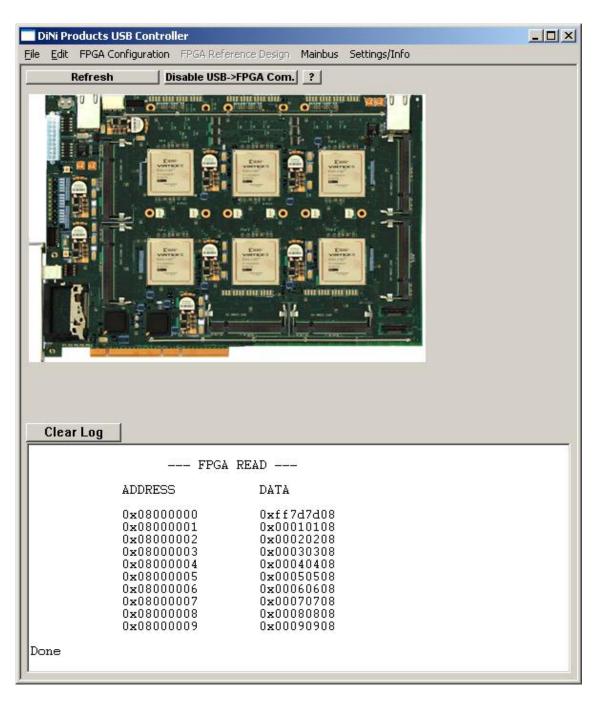

#### 5.2 Operating the USB Controller program

Run the USB controller application found on the product CD in D:\USB\_Software\_Applications\USBController\USBController.exe

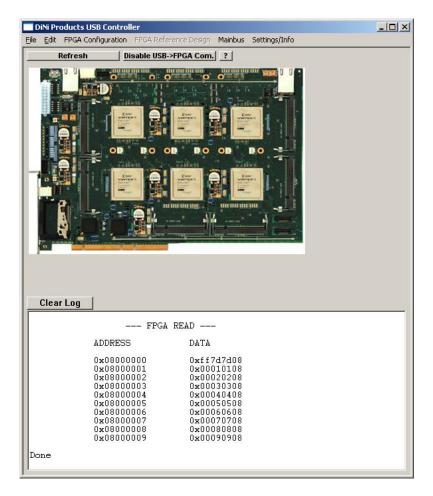

Figure 4 USB Controller Window

This window will appear showing the current state of the DN9000K10PCIE4GL. Next to each FPGA a green light will appear if that FPGA is configured successfully. The above window shows the USB Controller connected to a DN9000K10PCIE4GL with six LX110 FPGAs.

#### 5.2.1 Configure an FPGA

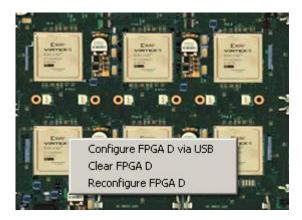

Even though the reference design should already be loaded (because you had a CompactFlash card installed when the board powered on), let's configure an FPGA over USB.

Clear an FPGA of its configuration. Right-click on an FPGA and select from the popup menu, "Clear FPGA". The blue light above the FPGA on the GUI and on the board should turn off.

To re-configure that FPGA using the USB Controller program, right-click on the FPGA and select Configure FPGA via USB from the popup menu. The program will open a dialog box for you to select the configuration file to use for configuration. Browse to the provided user's CD "D:\FPGA\_Reference\_Designs\Programming\_Files\DN9000K10PCIE4GL\MainTest\LX3 30\fpga\_a.bit"

If you are configuring an LX220 or LX110 device you should select a bit file from the LX220 or

LX110 directories instead. Failing to select the correct type of bit file will result in the USB Controller program to warn you, and the FPGA fail to configure. The program will report the status of the configuration when it finishes. "DONE did not go high". This refers to the DONE SelectMap signal, which is asserted by the FPGA when it is properly configured.

If you are configuring FPGA B or FPGA C, you should select fpga\_b.bit or fpga\_c.bit instead. Should you configure the wrong FPGA with the wrong bitfile, the FPGA will succeed to configure, but probably won't function properly. This is not recommended because it could lead to bus contention and excessive heat generation.

```

Done

FPGA B cleared successfully.

FPGA A cleared successfully.

Doing a sanity check...Sanity Check passed. Configuring FPGA

B via USB...please wait.

File

D:\\dn_BitFiles\DN9000K10PCIE4GL\MainTest\LX330\fpga_b.bit

transferred.

Configured FPGA B via USB

```

Figure 5 USB Controller Log Output

The message box below the DN9000K10PCIE4GL graphic should display some information about the configuration process. When the configuration is successful, the green LED should re-appear next to the FPGA.

#### 5.2.2 Set Clock Frequencies

To change the clock frequencies of G0, G1 or G2, select the "Clock settings" option from the "Settings" menu.

A dialog box appears asking to which frequency you would like to set each clock. Enter 100, 100, 200 for G0, G1 and G2 respectively. The log window will display feedback including what frequencies the clocks were set to. The actual frequency to which each clock is set may differ from the frequency you entered because the frequency synthesizers have a limited granularity.

#### 5.2.3 Check clock frequencies

The reference design will measure the frequency of each of the global clocks on the board and print them out if you select "read back clock frequencies" from the reference design menu. This will only work is the reference design is running and the "enable usb" option is selected.

#### **5.2.4** Run Hardware Test (DDR2)

First, hit the "Enable USB->FPGA communication" button. This must be done before this (or any usb) program can interact with the reference design. You must also have the reference design loaded, and a DDR2 module installed in a memory socket connected to the FPGA using that reference design. Also, the clock settings must be correct. Follow the procedure in the previous section to accomplish this.

From the FPGA Memory menu, select Test DDR. A box will appear and ask which FPGA should be tested. The log window will report whether the test passed. If it fails, it will print a list of addresses and data that failed. If you have a board with LX110 or LX220, remember some of the DDR SODIMM connectors (A,C2,D,F) will not work on your board.

If you would like to simulate a failure, you could repeat this guide with a broken DDR2 module or a squirrel installed, or with the DDR2 module removed. Other tests that could be performed from the USB Controller (but aren't part of this quick-start) are FPGA interconnect tests, Ethernet tests, and some other thing. For information on running these tests, see the Software chapter.

#### 5.3 Getting data to and from the FPGA

The USB Controller program also allows you to easily configure and transfer data to and from the user design on the emulation board. This data transfer occurs over the boards "MainBus". This interface is described in the Hardware chapter.

Some users may choose not to implement the "MainBus" interface, and use these signals for general-purpose FPGA interconnect. To allow this, by default the main bus is disabled, and the Host interface (USB in this case) is prevented from operating it. To override this setting, hit the "Enable USB->FPGA communication" button near the top of the window.

To read data from the FPGA design (the Dini Group reference design), select from the menu MainBus->Read

In the resulting dialog box, enter the address 0x080000000 in the address box, and "10" in the "number of DWORDs" box. Press OK, and then DONE. The result of the read is printed to the USB Controller log window.

```

FPGA READ

0x080000000 0x00000000

0x080000001 0x05000135

0x080000002 0xDEAD1234

0x080000004 0x1D0000000

...

```

Figure 6 USB Controller Log Output

The address 0x080000000 is by convention of the "MainBus" interface to be mapped to registers physically residing within FPGA A on the DN9000K10PCIE4GL. If FPGA A is not loaded with the Dini Group reference design (or a design that implements the MainBus slave), then all DWORDs will return 0xDEADDEAD, which is the timeout sentinel value.

# 6 Communicating over the Serial Port

You may want to communicate with your design over the user serial port (P1). The MainTest reference design that you already loaded has an asynchronous loop back on this port. If you want to test this connection, connect an RS232 terminal to the header and type stuff. The port should echo back what you are typing.

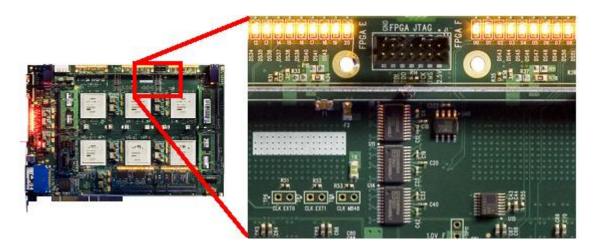

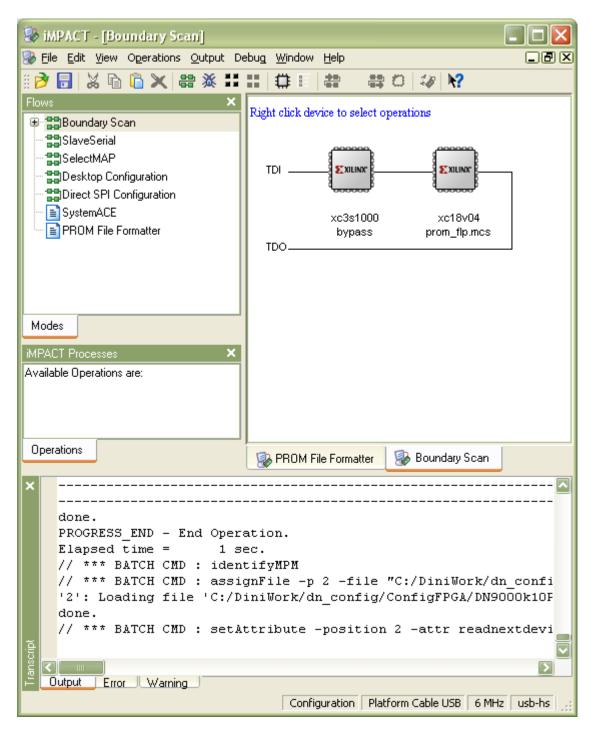

# 7 Scan the JTAG chain

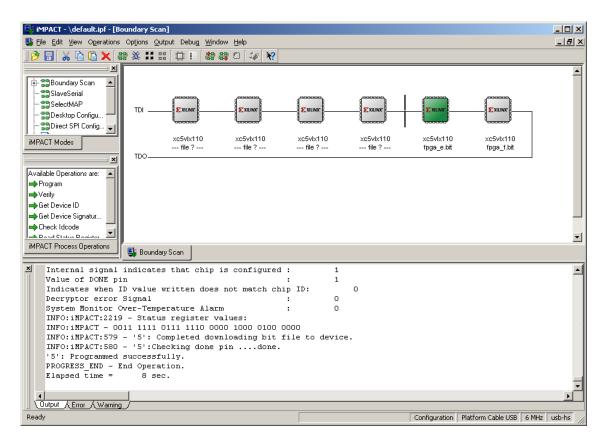

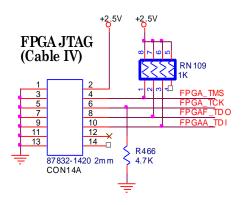

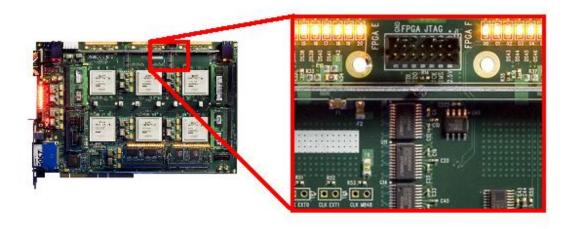

If you wish, you can program the FPGAs using their JTAG interface. Connect a Xilinx Platform USB cable into the FPGA JTAG port (J1), and open the IMPACT program that is installed with Xilinx ISE 8.2.

When you connect the Platform USB cable for the first time, the driver will install three times in a row, like a retarded parrot.

The program "scans the chain" to auto-detect the type and number of FPGAs installed on your board and display them on the screen. Right click on an FPGA and select "choose configuration file". Browse to the bit files provided on the user CD

D:\FPGA\_Reference\_Designs\Programming\_Files\DN9000K10PCIE4GL\MainTest\LX11 0\fpga\_A.bit

Right-click on the FPGA again and select "Program". Make sure "verify" is not selected, or it won't work and it won't tell you why.

This JTAG port should also be used for visibility products like Xilinx ChipScope.

If you don't see the above screen, and instead see a XC3S1000 and an 18V04, then you plugged into the wrong header. Smart!!

# 7.1 Moving On

Congratulations! You have just programmed the DN9000K10PCIE4GL and learned all of the features that you have to know to start your emulation project. If you are new to Xilinx FPGA, you might want start by compiling the reference design using the provided ISE projects, and adding code to the reference design, until you are comfortable with the design flow. You should also use the provided UCF constraint file as a starting point for your UCF file.

# **Controller Software**

The DN9000K10PCIE4GL can be hosted from USB or PCI. As an example to hosting using these interfaces, the Dini Group provides some controller software that allows configuring FPGAs, and changing the board settings. For more complex host behavior, such as interactively transferring data to and from the board from the host computer, you may have to develop your own host software, either USB or PCI. At the end of this chapter, there is a programmer's guide to help you interface to the DN9000K10PCIE4GL. This, along with the source code of the example software should be able to get you communicating with the DN9000K10PCIE4GL.

The software included with the DN9000K10PCIE4GL is

• USB Controller – A Windows XP only GUI application capable of configuring

FPGAs, sending data to the user FPGA core via USB, changing board settings, and running hardware tests.

• AETest\_usb - A cross-platform (Windows, DOS, Linux, Solaris) command-

line application capable of configuring FPGAs, sending data

via USB, and changing board settings.