# PrimeCell<sup>®</sup> AHB SRAM/NOR Memory Controller (PL241)

**Revision: r0p1**

**Technical Reference Manual**

Copyright © 2006 ARM Limited. All rights reserved. ARM DDI 0389B

## PrimeCell AHB SRAM/NOR Memory Controller (PL241) Technical Reference Manual

Copyright © 2006 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

**Change History**

| Date             | Issue | Confidentiality  | Change                  |

|------------------|-------|------------------|-------------------------|

| 17 March 2006    | А     | Non-Confidential | First release for r0p0. |

| 20 December 2006 | В     | Non-Confidential | Updated for r0p1.       |

#### **Proprietary Notice**

Words and logos marked with  $^{\otimes}$  or  $^{\bowtie}$  are registered trademarks or trademarks of ARM Limited in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM Limited in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents **PrimeCell AHB SRAM/NOR Memory Controller** (PL241) Technical Reference Manual

| Preface |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | About this manual                                                               | x                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | Feedback                                                                        | xiv                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Introd  |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.1     | About the AHB MC                                                                | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2     | Supported devices                                                               | 1-5                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Funct   | tional Overview                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1     | Functional description                                                          | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2     | SMC                                                                             | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.3     | Functional operation                                                            | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.4     | SMC functional operation                                                        | 2-15                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Progr   | rammer's Model                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1     | About the programmer's model                                                    | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.2     | Register summary                                                                | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.3     | Register descriptions                                                           | 3-6                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | Introd<br>1.1<br>1.2<br>Func<br>2.1<br>2.2<br>2.3<br>2.4<br>Progr<br>3.1<br>3.2 | About this manual         Feedback         Introduction         1.1       About the AHB MC         1.2       Supported devices         Functional Overview         2.1       Functional description         2.2       SMC         2.3       Functional operation         2.4       SMC functional operation         Programmer's Model         3.1       About the programmer's model         3.2       Register summary |

| Chapter 4  | <b>Prog</b><br>4.1 | rammer's Model for Test<br>SMC integration test registers | 4-2 |

|------------|--------------------|-----------------------------------------------------------|-----|

| Chapter 5  | Devi               | ce Driver Requirements                                    |     |

|            | 5.1                | Memory initialization                                     | 5-2 |

| Appendix A | Sign               | al Descriptions                                           |     |

|            | A.1                | About the signals list                                    | A-2 |

|            | A.2                | Clocks and resets                                         | A-3 |

|            | A.3                | AHB signals                                               | A-4 |

|            | A.4                | SMC memory interface signals                              |     |

|            | A.5                | SMC miscellaneous signals                                 |     |

|            | A.6                | Low-power interface                                       | A-7 |

|            | A.7                | Configuration signal                                      | A-8 |

|            | A.8                | Scan chains                                               | A-9 |

|            | Glos               | sary                                                      |     |

#### ARM DDI 0389B

## List of Tables **PrimeCell AHB SRAM/NOR Memory Controller** (PL241) Technical Reference Manual

|            | Change History                                                                | ii   |

|------------|-------------------------------------------------------------------------------|------|

| Table 2-1  | Static memory clocking options                                                | 2-12 |

| Table 2-2  | Asynchronous read opmode chip register settings                               |      |

| Table 2-3  | Asynchronous read SRAM cycles register settings                               | 2-28 |

| Table 2-4  | Asynchronous read in multiplexed-mode opmode chip register settings           | 2-29 |

| Table 2-5  | Asynchronous read in multiplexed-mode SRAM cycles register settings           | 2-29 |

| Table 2-6  | Asynchronous write opmode chip register settings                              | 2-30 |

| Table 2-7  | Asynchronous write SRAM cycles register settings                              | 2-30 |

| Table 2-8  | Asynchronous write in multiplexed-mode opmode chip register settings          | 2-31 |

| Table 2-9  | Asynchronous write in multiplexed-mode SRAM cycles register settings          | 2-31 |

| Table 2-10 | Page read opmode chip register settings                                       | 2-31 |

| Table 2-11 | Page read SRAM cycles register settings                                       | 2-31 |

| Table 2-12 | Synchronous burst read opmode chip register settings                          | 2-32 |

| Table 2-13 | Synchronous burst read SRAM cycles register settings                          | 2-32 |

| Table 2-14 | Synchronous burst read in multiplexed-mode opmode chip register settings      | 2-34 |

| Table 2-15 | Synchronous burst read in multiplexed-mode read SRAM cycles register settings | 2-34 |

| Table 2-16 | Synchronous burst write opmode chip register settings                         | 2-35 |

| Table 2-17 | Synchronous burst write SRAM cycles register settings                         | 2-35 |

| Table 2-18 | Synchronous burst write in multiplexed-mode opmode chip register settings     | 2-36 |

| Table 2-19 | Synchronous burst write in multiplexed-mode SRAM cycles register settings     | 2-36 |

| Table 2-20 | Synchronous read and asynchronous write opmode chip register settings         | 2-37 |

| Table 2-21 | Synchronous read and asynchronous write opmode chip register settings 2-37 |

|------------|----------------------------------------------------------------------------|

| Table 3-1  | Register summary 3-4                                                       |

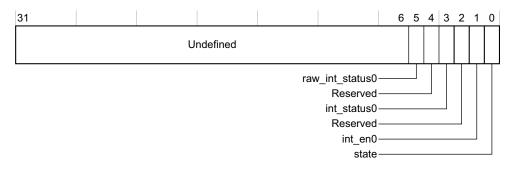

| Table 3-2  | smc_memc_status Register bit assignments 3-6                               |

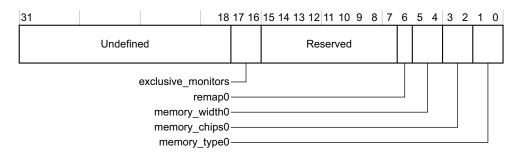

| Table 3-3  | smc_memif_cfg Register bit assignments 3-7                                 |

| Table 3-4  | smc_memc_cfg_set Register bit assignments 3-9                              |

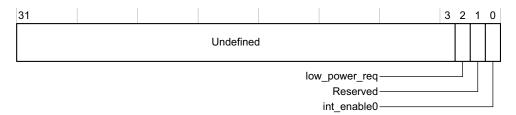

| Table 3-5  | smc_memc_cfg_clr Register bit assignments 3-9                              |

| Table 3-6  | smc_direct_cmd Register bit assignments 3-10                               |

| Table 3-7  | smc_set_cycles Register bit assignments 3-11                               |

| Table 3-8  | smc_set_opmode Register bit assignments 3-13                               |

| Table 3-9  | smc_refresh_period_0 Register bit assignments 3-15                         |

| Table 3-10 | smc_sram_cycles Register bit assignments 3-16                              |

| Table 3-11 | smc_opmode Register bit assignments 3-17                                   |

| Table 3-12 | smc_user_status Register bit assignments 3-18                              |

| Table 3-13 | smc_user_config Register bit assignments 3-19                              |

| Table 3-14 | smc_periph_id Register bit assignments 3-19                                |

| Table 3-15 | smc_periph_id_0 Register bit assignments 3-20                              |

| Table 3-16 | smc_periph_id_1 Register bit assignments 3-21                              |

| Table 3-17 | smc_periph_id_2 Register bit assignments 3-21                              |

| Table 3-18 | smc_periph_id_3 Register bit assignments 3-21                              |

| Table 3-19 | smc_pcell_id Register bit assignments 3-22                                 |

| Table 3-20 | smc_pcell_id_0 Register bit assignments 3-23                               |

| Table 3-21 | smc_pcell_id_1 Register bit assignments 3-23                               |

| Table 3-22 | smc_pcell_id_2 Register bit assignments 3-24                               |

| Table 3-23 | smc_pcell_id_3 Register bit assignments 3-24                               |

| Table 4-1  | SMC test register summary 4-2                                              |

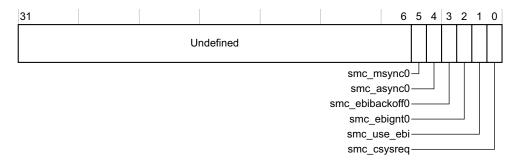

| Table 4-2  | smc_int_cfg Register bit assignments 4-3                                   |

| Table 4-3  | smc_int_inputs Register bit assignments 4-3                                |

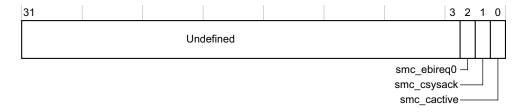

| Table 4-4  | smc_int_outputs Register bit assignments 4-4                               |

| Table A-1  | Clocks and resets A-3                                                      |

| Table A-2  | AHB signals A-4                                                            |

| Table A-3  | SMC memory interface signals A-5                                           |

| Table A-4  | SMC miscellaneous signals A-6                                              |

| Table A-5  | Low-power interface signals A-7                                            |

| Table A-6  | Configuration signal A-8                                                   |

| Table A-7  | Scan chain signals A-9                                                     |

|            |                                                                            |

## List of Figures **PrimeCell AHB SRAM/NOR Memory Controller** (PL241) Technical Reference Manual

|             | Key to timing diagram conventions           | xii    |

|-------------|---------------------------------------------|--------|

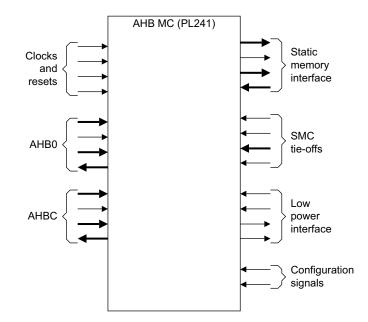

| Figure 1-1  | AHB MC (PL241) configuration                | 1-2    |

| Figure 2-1  | AHB MC (PL241) configuration                | 2-2    |

| Figure 2-2  | AHB MC (PL241) clock domains                | 2-3    |

| Figure 2-3  | SMC block diagram                           | 2-4    |

| Figure 2-4  | SMC SRAM pad interface external connections | 2-6    |

| Figure 2-5  | Big-endian implementation                   | . 2-10 |

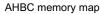

| Figure 2-6  | AHBC memory map                             | . 2-11 |

| Figure 2-7  | Request to enter low-power mode             |        |

| Figure 2-8  | AHB domain denying a low-power request      | . 2-13 |

| Figure 2-9  | Accepting requests                          | . 2-14 |

| Figure 2-10 | SMC aclk domain FSM                         |        |

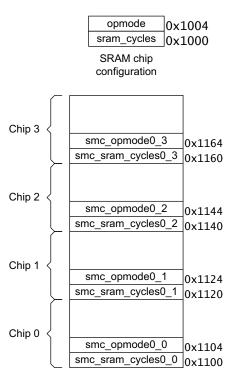

| Figure 2-11 | Chip configuration registers                | . 2-23 |

| Figure 2-12 | Device pin mechanism                        | . 2-25 |

| Figure 2-13 | Software mechanism                          | . 2-26 |

| Figure 2-14 | Asynchronous read                           | . 2-29 |

| Figure 2-15 | Asynchronous read in multiplexed-mode       | . 2-29 |

| Figure 2-16 | Asynchronous write                          | . 2-30 |

| Figure 2-17 | Asynchronous write in multiplexed-mode      | . 2-31 |

| Figure 2-18 | Page read                                   | . 2-32 |

| Figure 2-19 | Synchronous burst read                      |        |

| Figure 2-20 | Synchronous burst read in multiplexed-mode 2-34                            |

|-------------|----------------------------------------------------------------------------|

| Figure 2-21 | Synchronous burst write                                                    |

| Figure 2-22 | Synchronous burst write in multiplexed-mode                                |

| Figure 2-23 | Synchronous read and asynchronous write 2-38                               |

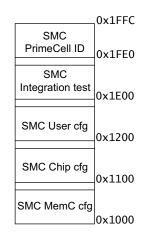

| Figure 3-1  | SMC register map 3-2                                                       |

| Figure 3-2  | SMC configuration register map 3-3                                         |

| Figure 3-3  | SMC chip configuration register map 3-3                                    |

| Figure 3-4  | SMC user configuration register map 3-4                                    |

| Figure 3-5  | SMC peripheral and PrimeCell identification configuration register map 3-4 |

| Figure 3-6  | smc_memc_status Register bit assignments 3-6                               |

| Figure 3-7  | smc_memif_cfg Register bit assignments 3-7                                 |

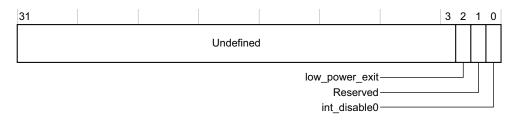

| Figure 3-8  | smc_memc_cfg_set Register bit assignments 3-8                              |

| Figure 3-9  | smc_memc_cfg_clr Register bit assignments 3-9                              |

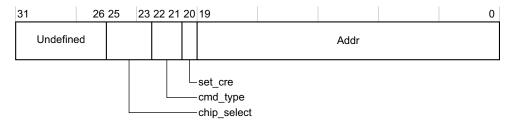

| Figure 3-10 | smc_direct_cmd Register bit assignments 3-10                               |

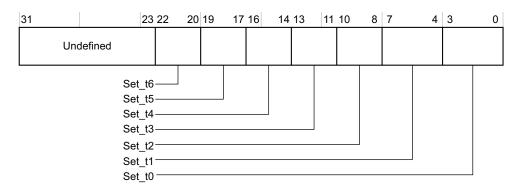

| Figure 3-11 | smc_set_cycles Register bit assignments 3-11                               |

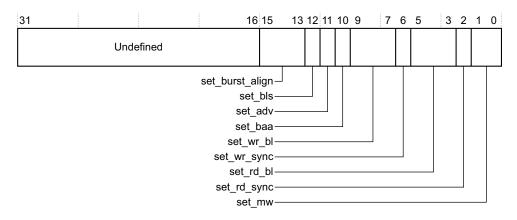

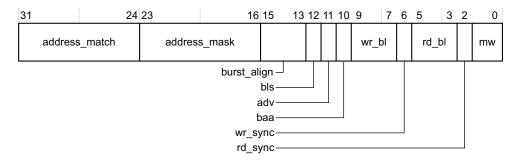

| Figure 3-12 | smc_set_opmode Register bit assignments 3-12                               |

| Figure 3-13 | smc_refresh_period_0 Register bit assignments 3-15                         |

| Figure 3-14 | smc_sram_cycles Register bit assignments 3-15                              |

| Figure 3-15 | smc_opmode Register bit assignments 3-16                                   |

| Figure 3-16 | smc_user_status Register bit assignments 3-18                              |

| Figure 3-17 | smc_user_config Register bit assignments 3-19                              |

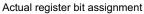

| Figure 3-18 | smc_periph_id Register bit assignments 3-20                                |

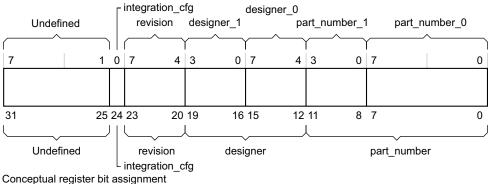

| Figure 3-19 | smc_pcell_id Register bit assignments 3-22                                 |

| Figure 4-1  | SMC integration test register map 4-2                                      |

| Figure 4-2  | smc_int_cfg Register bit assignments 4-2                                   |

| Figure 4-3  | smc_int_inputs Register bit assignments 4-3                                |

| Figure 4-4  | smc_int_outputs Register bit assignments 4-4                               |

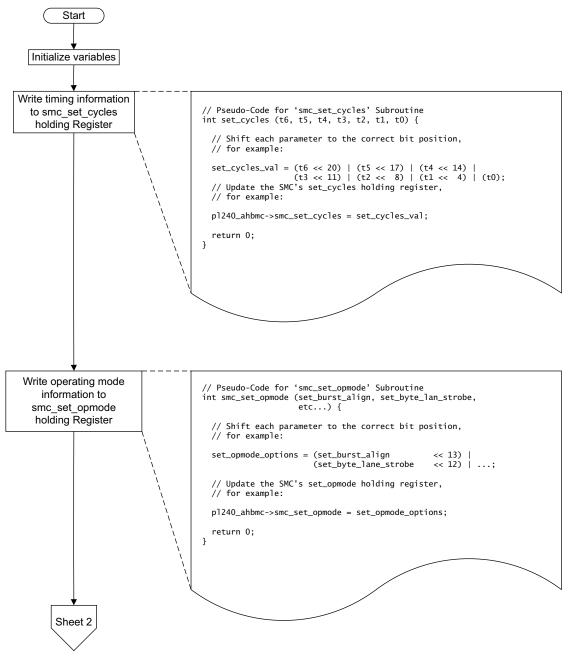

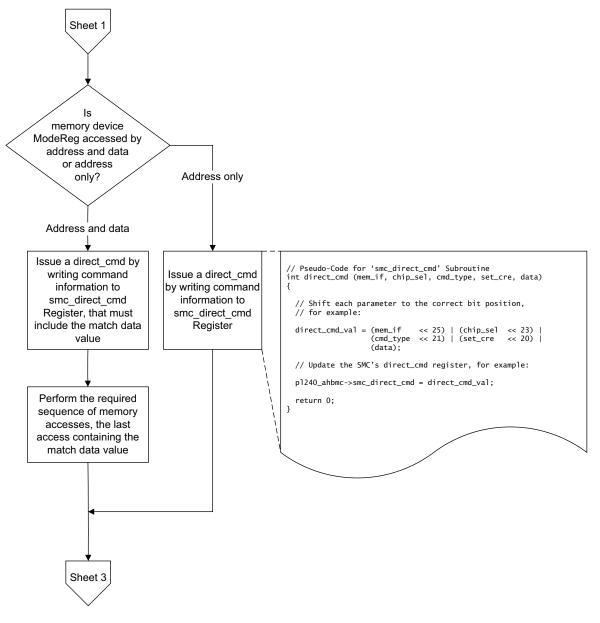

| Figure 5-1  | SMC and memory initialization sheet 1 of 3 5-3                             |

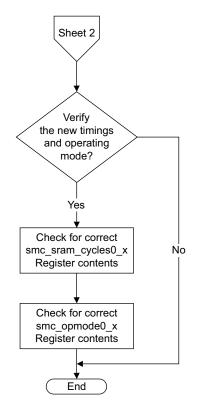

| Figure 5-2  | SMC and memory initialization sheet 2 of 3 5-4                             |

| Figure 5-3  | SMC and memory initialization sheet 3 of 3 5-5                             |

| Figure A-1  | AHB MC PL241 grouping of signals A-2                                       |

## Preface

This preface introduces the *PrimeCell AHB SRAM/NOR Memory Controller (MC)* (*PL241*) *Technical Reference Manual*. It contains the following sections:

- About this manual on page x

- *Feedback* on page xiv.

### About this manual

This is the *Technical Reference Manual* (TRM) for the *PrimeCell AHB SRAM/NOR Memory Controller*.

#### **Product revision status**

| The <i>rnpn</i> identifier indicates the revision status of the product described in this manual, where: |                                                                      |  |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|

| rn                                                                                                       | Identifies the major revision of the product.                        |  |

| p <i>n</i>                                                                                               | Identifies the minor revision or modification status of the product. |  |

#### Intended audience

This manual is written for system designers, system integrators, and verification engineers who are designing a *System-on-Chip* (SoC) device that uses the AHB MC. The manual describes the external functionality of the AHB MC.

#### Using this manual

This manual is organized into the following chapters:

#### **Chapter 1** Introduction

Read this chapter for a high-level view of the AHB MC and a description of its features.

#### Chapter 2 Functional Overview

Read this chapter for a description of the major components of the AHB MC and how they operate.

#### Chapter 3 Programmer's Model

Read this chapter for a description of the AHB MC registers.

#### Chapter 4 Programmer's Model for Test

Read this chapter for a description of the additional logic for integration testing.

#### Chapter 5 Device Driver Requirements

Read this chapter for a description of device driver requirements for the *Static Memory Controller* (SMC).

#### Appendix A Signal Descriptions

Read this appendix for a description of the AHB MC input and output signals.

**Glossary** Read the Glossary for definitions of terms used in this manual.

#### Conventions

Conventions that this manual can use are described in:

- Typographical

- *Timing diagrams* on page xii

- Signals on page xii

- *Numbering* on page xiii.

### Typographical

The typographical conventions are:

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                                                                                                                                          |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                                                                                  |  |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                                                                            |  |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                                                                                |  |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                                                                                          |  |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                                                                                              |  |

| < and >           | <ul> <li>Angle brackets enclose replaceable terms for assembler syntax where they appear in code or code fragments. They appear in normal font in running text. For example:</li> <li>MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd></li> </ul> |  |

• The Opcode\_2 value selects the register that is accessed.

— Note —

Angle brackets can also enclose a permitted range of values. The example, <0-3>, shows that in name extensions, only one of the values 0, 1, 2, or 3 is valid.

#### **Timing diagrams**

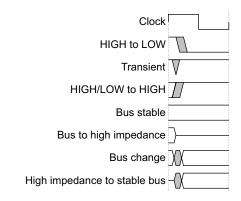

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Key to timing diagram conventions

#### Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is<br>active-HIGH or active-LOW. Asserted means HIGH for<br>active-HIGH signals and LOW for active-LOW signals. |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Lower-case n | Denotes an active-LOW signal.                                                                                                                                                 |  |

| Prefix A     | Denotes global Advanced eXtensible Interface (AXI) signals.                                                                                                                   |  |

| Prefix AR    | Denotes AXI read address channel signals.                                                                                                                                     |  |

| Prefix AW    | Denotes AXI write address channel signals.                                                                                                                                    |  |

| Prefix B | Denotes AXI write response channel signals.          |  |

|----------|------------------------------------------------------|--|

| Prefix C | Denotes AXI low-power interface signals.             |  |

| Prefix H | Denotes Advanced High-performance Bus (AHB) signals. |  |

| Prefix P | Denotes Advanced Peripheral Bus (APB) signals.       |  |

| Prefix R | Denotes AXI read data channel signals.               |  |

| Prefix W | Denotes AXI write data channel signals.              |  |

#### Numbering

The Verilog numbering convention is:

#### <size in bits>'<base><number>

This is a Verilog method of abbreviating constant numbers. For example:

- 'h7B4 is an unsized hexadecimal value.

- 'o7654 is an unsized octal value.

- 8'd9 is an eight-bit wide decimal value of 9.

- 8'h3F is an eight-bit wide hexadecimal value of 0x3F. This is equivalent to b00111111.

- 8'b1111 is an eight-bit wide binary value of b00001111.

#### **Further reading**

This section lists publications by ARM Limited, and by third parties.

ARM Limited periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets, addenda, and the Frequently Asked Questions list.

#### **ARM** publications

This manual contains information that is specific to the AHB MC. See the following documents for other relevant information:

- PrimeCell AHB SRAM/NOR Memory Controller (PL241) Integration Manual (ARM DII 0151)

- PrimeCell AHB SRAM/NOR Memory Controller (PL241) Implementation Guide (ARM DDI 0144)

- AMBA<sup>™</sup> Specification (Rev 2.0) (ARM IHI 0011)

- AMBA 3 APB Protocol v1.0 Specification (ARM IHI 0024).

## Feedback

ARM Limited welcomes feedback on the AHB MC and its documentation.

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier giving:

- the product name

- a concise explanation of your comments.

#### Feedback on this manual

If you have any comments on this manual, send email to errata@arm.com giving:

- the title

- the number

- the relevant page number(s) to which your comments apply

- a concise explanation of your comments.

ARM Limited also welcomes general suggestions for additions and improvements.

## Chapter 1 Introduction

This chapter introduces the AHB MC. It contains the following sections:

- About the AHB MC on page 1-2

- Supported devices on page 1-5.

## 1.1 About the AHB MC

The AHB MC is an *Advanced Microcontroller Bus Architecture* (AMBA) compliant *System-on-Chip* (SoC) peripheral. It is developed, tested, and licensed by ARM Limited.

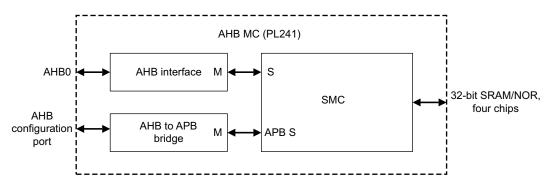

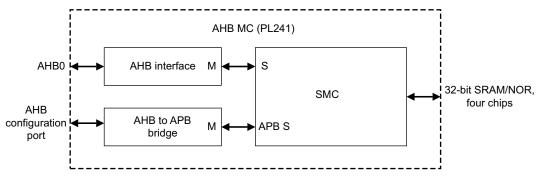

The AHB MC takes advantage of the newly developed *Static Memory Controller* (SMC). The AHB MC has an AHB port with access to the external memory. The AHB port has a bridge interface to the memory controller. There is a separate AHB port to configure the memory controller. Specific configurations of the SMC are instantiated to target specific memory devices. Figure 1-1 shows the AHB MC (PL241) configuration.

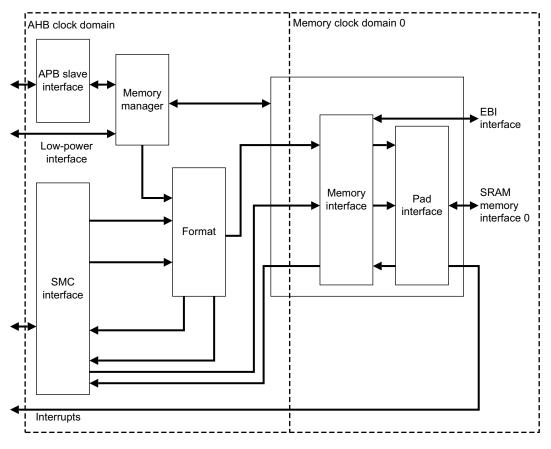

Figure 1-1 AHB MC (PL241) configuration

This section describes:

- AHB interface on page 1-3

- AHB to APB bridge on page 1-3

- *SMC* on page 1-4

- *Clock domains* on page 1-4

- *Low-power interfaces* on page 1-4.

#### 1.1.1 AHB interface

The interface converts the incoming AHB transfers to the protocol used internally by the AHB MC.

The interface has the following features:

- all AHB fixed length burst types are directly translated to fixed length bursts

- all undefined length INCR bursts are converted to INCR4 bursts

- broken bursts are supported

- the bufferable bit of the **HPROT** signal determines if the interface must wait for a write transfer to complete internally

- a *Read After Write* (RAW) hazard detection buffer avoids RAW hazards

- AHB response signals are registered to improve timing

- locked transfers are supported within a 512MB region

- **HWDATA** is registered to improve internal timing paths

- a big-endian 32-bit mode option is implemented

- AHB error response logic is removed as no internal components generate errors.

This interface is a fully validated component. This ensures that it obeys both the AHB protocol and the internal protocol that the interconnect uses.

See Chapter 2 Functional Overview for more information.

#### 1.1.2 AHB to APB bridge

This bridge converts AHB transfers from the configuration port to the APB transfers that the internal memory controllers require.

See Chapter 2 Functional Overview for more information.

#### 1.1.3 SMC

The SMC is a high-performance, area-optimized SRAM memory controller.

The SMC is pre-configured and validated for:

- the SRAM memory type

- the number of SRAM memory devices

- the maximum SRAM memory width.

The SRAM memory interface type is defined as supporting:

- synchronous or asynchronous SRAM

- Pseudo Static Random Access Memory (PSRAM)

- NOR flash

- NAND flash devices with an SRAM interface.

The SMC block offers the following features:

- it is configured to support the maximum SRAM memory data width of 32-bit

- programmable cycle timings, and memory width per chip select

- atomic switching of memory device and controller operating modes

- support for the PL220 *External Bus Interface* (EBI) PrimeCell, enabling sharing of external address and data bus pins between memory controller interfaces

- support for a low-power interface

- support for a remap signal

- support for clock domains to be synchronous or asynchronous

See Chapter 2 Functional Overview for more information.

#### 1.1.4 Clock domains

The memory controller has two clock domains:

- AHB clock domain

- static memory clock domain.

See Chapter 2 Functional Overview for more information.

#### 1.1.5 Low-power interfaces

The memory controller has two low-power interfaces, one for each clock domain.

See Chapter 2 Functional Overview for more information.

### 1.2 Supported devices

The SMC supports SRAM/NOR, see *SMC* on page 1-4. The *Release Note* provides a specific list of memory devices tested with each configuration.

Some memory devices or series of memory devices have specific requirements:

#### Intel W18 series NOR FLASH, for example 28f128W18td

These devices, when in synchronous operation, use a **WAIT** pin. However non-array operations when in synchronous mode do not use the **WAIT** pin and it is always asserted. The controller cannot differentiate between array and non-array accesses and therefore cannot support these non-array accesses.

Therefore, W18 devices can only carry out non-array operations such as Read Status in asynchronous modes of operation.

#### Cellular RAM 1.0, 64MB PSRAM, for example mt45w4mw16bfb\_701\_1us

You can program these devices using a **CRE** pin or by software access. Whenever you program these devices through software access, using a sequence of two reads followed by two writes, ensure that the third access, that is, the first write is a CE# controlled write.

SMC only does WE# controlled writes. This is to simplify the design of the SMC by having fewer timing registers and simpler timing controls.

Therefore, you can only program these devices by using the **CRE** pin method of access.

#### — Note ———

Because the memory controller maps INCR transfers into INCR4 transfers, it does not support memory mapped FIFO components.

Introduction

## Chapter 2 Functional Overview

This chapter describes the major components of the AHB MC and how they operate. It contains the following sections:

- *Functional description* on page 2-2

- *SMC* on page 2-4

- *Functional operation* on page 2-7.

- *SMC functional operation* on page 2-15.

## 2.1 Functional description

Figure 2-1 shows an AHB MC (PL241) configuration.

#### Figure 2-1 AHB MC (PL241) configuration

This section is divided into:

- AHB interface

- AHB to APB bridge

- Clock domains on page 2-3

- *Low-power interface* on page 2-3

- SMC on page 2-4.

#### 2.1.1 AHB interface

The AHB MC fully supports the AMBA AHB 2.0 specification. This interface component converts the incoming AHB transfers to the required transfers of the internal interconnect protocol. Because of the design of the internal interconnect, some optimizations are made in the interface to improve performance.

See AHB interface operation on page 2-7 for more information.

#### 2.1.2 AHB to APB bridge

The internal memory controllers of the AHB MC use the AMBA3 APB protocol for their configuration ports. To enable the AHB MC to externally function as an AHB device, the APB configuration ports are connected to an AHB to APB bridge. The bridge converts incoming AHB transfers from the configuration port to the APB transfers that the internal memory controller requires. This bridge is part of the PrimeCell infrastructure components, part BP127.

See AHB to APB bridge operation on page 2-10 for more information.

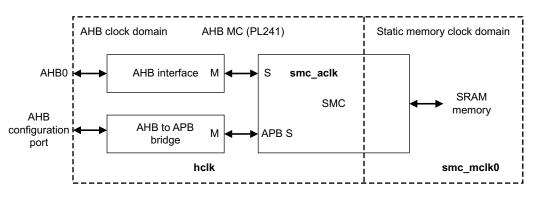

#### 2.1.3 Clock domains

The memory controller has two clock domains:

#### AHB clock domain

This is clocked by hclk, smc\_aclk and reset by hresetn.

#### Static memory clock domain

This is clocked by **smc\_mclk0**, **smc\_mclk0n** and reset by **smc\_mreset0n**.

Figure 2-2 shows the two clock domains.

#### Figure 2-2 AHB MC (PL241) clock domains

The memory controller supports many different options for clocking the different domains.

See Clock domain operation on page 2-11 for more information.

#### 2.1.4 Low-power interface

The memory controller has two low-power interfaces, one for each clock domain. These operate with a simple three signal protocol. It is expected that a system clock controller drives these interfaces and associated clocks. Each domain has individual control to enable independent handshaking with the system clock controller.

See Low-power interface operation on page 2-12 for more information.

## 2.2 SMC

Figure 2-3 shows a block diagram of the SMC.

#### Figure 2-3 SMC block diagram

The main blocks of the SMC are:

- *SMC interface* on page 2-5

- *APB slave interface* on page 2-5

- Format on page 2-5

- *Memory manager* on page 2-5

- *Memory interface* on page 2-5

- *Pad interface* on page 2-6

- *Interrupts* on page 2-6.

#### 2.2.1 SMC interface

The SMC interface processes the incoming AHB transfers and sends them to the command format block.

#### 2.2.2 APB slave interface

The SMC has 4KB of memory allocated to it.

The APB slave interface accesses the SMC registers to program the memory system configuration parameters and to provide status information. See Chapter 3 *Programmer's Model* and *APB slave interface operation* on page 2-19 for more information.

#### 2.2.3 Format

The format block receives memory accesses from the SMC interface and the memory manager. Read and write requests are arbitrated on a round robin basis. Requests from the manager have the highest priority. The format block also maps AHB memory transfers onto appropriate memory transfers and passes these to the memory interface through the command FIFO.

See Format block on page 2-19 for more information.

#### 2.2.4 Memory manager

The memory manager tracks and controls the current state of **smc\_aclk** domain logic. The block is responsible for:

- updating timing registers and controlling direct commands issued to memory

- controlling entry-to and exit-from low-power mode through the APB interface

- the low-power interface.

See Memory manager operation on page 2-22 for more information.

#### 2.2.5 Memory interface

The SRAM memory interface consists of command, read data and write data FIFOs, plus a control FSM. To support an EBI, the memory interface also contains an EBI FSM. This controls interaction with the EBI and prevents the memory interface FSM from issuing commands until it has been granted the external bus.

See Memory interface operation on page 2-27 for more information.

#### 2.2.6 Pad interface

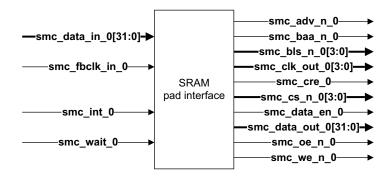

The pad interface module provides a registered I/O interface for data and control signals. It also contains interrupt generation logic.

Figure 2-4 shows the SRAM pad interface external signals. Clock and reset signals are omitted.

Figure 2-4 SMC SRAM pad interface external connections

#### 2.2.7 Interrupts

The SRAM memory interface support interrupts. The interrupt is triggered on the rising edge of the **smc\_int\_0** input for the SRAM memory interface.

See Interrupts operation on page 2-27 for more information.

## 2.3 Functional operation

This section is divided into:

- AHB interface operation

- AHB to APB bridge operation on page 2-10

- Clock domain operation on page 2-11

- *Low-power interface operation* on page 2-12

- *SMC functional operation* on page 2-15.

#### 2.3.1 AHB interface operation

This section describes:

- AHB fixed burst types

- Undefined length INCR bursts on page 2-8

- Broken bursts on page 2-8

- Bufferable bit of the HPROT signal on page 2-8

- Read after write hazard detection buffer on page 2-9

- AHB response signals on page 2-9

- Locked transfers on page 2-9

- *Registered HWDATA* on page 2-10

- Big-endian 32-bit mode on page 2-10

- *Removal of AHB error response logic* on page 2-10.

### AHB fixed burst types

All AHB fixed length bursts directly map to burst types that the internal interconnect uses. The internal interconnect and the memory controller are based on transferring bursts of data. The larger the burst size, the more efficient the transfer and overall performance. The standard AHB fixed length burst types are directly mapped to the internal protocol.

Burst operation has performance benefits because when the first beat of a burst is accepted, it contains data about the remaining beats. For example, from the first beat of a read burst, all the data required to complete the transfer can be read from memory. This first transfer has some delay before data is returned. Subsequent beats of the burst can have less delay because the data they require might have already been read from the memory.

#### **Undefined length INCR bursts**

All undefined length INCR bursts are converted to INCR bursts of length four. Many AHB masters rely on using undefined length INCR bursts to access data. If each INCR transfer is processed as a single transfer by the internal protocol then the performance is significantly degraded.

The bridge converts the incoming INCR transfers to INCR transfers of length four, INCR4. This mean that the bridge speculatively requests data from the internal interconnect, before it knows it is going to require it. If the AHB master continues the burst, then the data can be returned quickly because it has already been requested. When the INCR burst finishes, the bridge disregards any data requested from the internal interconnect that is not required.

Any INCR burst of less than four beats results in a broken INCR4. Undefined length INCR bursts of more than four beats are split into an appropriate number of INCR4s plus a broken INCR4, if required.

#### **Broken bursts**

To fully support the AMBA AHB 2.0 specification, the bridge supports all broken AHB bursts. Although bursts cannot be broken by an AHB master, if the AHB system has multiple masters then the AHB system arbitration can break a burst. Also, because the bridge converts INCR to INCR4, broken INCR4s occur when undefined length INCRs of a length not equal to a multiple of four are performed.

To support broken bursts, the bridge must keep track of how many beats of a burst have been performed and ensure it obeys the protocol of the interconnect. For read bursts, this means draining the interconnect of any requested data that is not required. For write bursts this means artificially extending write data with enough beats to obey the protocol. The interconnect uses write strobes to indicate the bytes of the data bus that are valid. When extending broken bursts, these strobes are deasserted so that the artificial data does not corrupt the actual memory.

#### Bufferable bit of the HPROT signal

The bufferable bit of the **HPROT** signal determines whether the bridge must wait for a write transfer to complete internally. The AHB protection control bits support the concept of bufferable data accesses. The **HPROT**[2] signal determines this. The internal interconnect supports the concept of a write response to indicate when data has actually been written to memory. The bridge exploits these features by not waiting for the write response if the access is described as bufferable. This enables numerous bufferable writes to occur with minimum latency. These are accepted by the interconnect and queued in the memory controller.

If transfers are described as non-bufferable then the bridge must wait for the write response to indicate that the transfer has been completed to memory. If numerous bufferable writes are performed, followed by a non-bufferable write, then the bridge must wait until it receives the write response associated with the final write.

#### Read after write hazard detection buffer

A RAW hazard detection buffer avoids potential RAW hazards. The protocol used internally to AHB MC does not perform memory coherency checks to catch *Write After Read* (WAR) or RAW hazards.

Because of the nature of the AHB protocol, WAR hazards never occur because the read must have completed before the write can be accepted.

Because the bridge permits writes to be buffered internally, there is a potential for a RAW hazard to occur. If you perform a bufferable write then it might not complete immediately. If a read to that same memory location is performed then both transfers can be in the queue and the internal memory controller can reorder these transactions for performance reasons so that the read occurs before the write. This means that the data read might be the value before the most recent write. The bridge has to detect these potential cases and stall the read transfer until any buffered writes that might cause a RAW hazard have been completed.

The bridge contains logic to monitor up to four outstanding write addresses. If an incoming read occurs to a 4KB region that has been written to, then it is stalled. If four bufferable writes occur then the AHB is stalled until a response is seen for the first of the four writes in the buffer.

### AHB response signals

The interconnect used within the AHB MC contains many combinatorial paths that link different AHB input ports. To improve the synthesis timing, the AHB responses are registered to limit these paths to within the design.

#### Locked transfers

AHB MC supports locked transfers, within a 512MB region. This is because of the way the interconnect processes locked transfers. There is a significant performance penalty in using locked transfers. Transfers that are locked together wait for all other ports to complete any outstanding transfers before they can begin. While a locked sequence occurs to a specific 512MB memory region, all other access to that region is stalled. All locked writes are processed as non-bufferable writes and so have to wait for the appropriate write response before indicating their completion.

#### **Registered HWDATA**

The interconnect used within the AHB MC contains combinatorial paths for the write data. To improve the synthesis timing, **HWDATA** is registered and makes these paths internal to the design.

#### **Big-endian 32-bit mode**

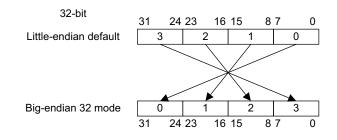

The AHB MC supports the option of storing data to memory in big-endian 32-bit mode. Each bridge contains the logic to implement this data mapping depending on the **big\_endian** input tie-off. Figure 2-5 shows that if the tie off is asserted then the data buses are reordered.

Figure 2-5 Big-endian implementation

#### **Removal of AHB error response logic**

The internal protocol used within AHB MC supports the concept of errors. However none of the components used ever generate errors. This means that the bridge does not require any logic to generate AHB errors because there are no circumstances when errors can be generated.

#### 2.3.2 AHB to APB bridge operation

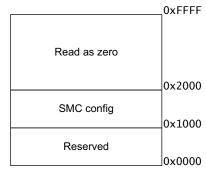

The internal memory controller has an APB configuration port. The AHB configuration port is mapped to it using an AHB to APB bridge. Figure 2-6 on page 2-11 shows that each internal memory controller configuration port has a 4KB address space.

#### Figure 2-6 AHBC memory map

The other fourteen 4KB regions are read as zero. The lower 16 bits of the AHB address decode the memory controller that is being used. An external AHB decoder determines where in the system memory map, this 64KB region is located. See *About the programmer's model* on page 3-2 for information on the internal memory controller configuration registers. The configuration port of the internal memory controller is APB, so only word reads and writes are supported.

#### 2.3.3 Clock domain operation

The memory controller supports two clock domains:

- the AHB clock domain

- the static memory clock domain.

The **hclk** input drives the AHB clock domain. This clock drives the AHB interfaces and bus matrix. The static memory controller has a separate clock input in this domain. This is called **smc\_aclk**. This signal is separated to enable the clock to be stopped independently of **hclk** for low-power operation, see *Low-power interface operation* on page 2-12. These two clocks must always be driven from the same clock source. The input signal **hresetn** resets this clock domain.

The static memory clock domain controls the memory interface logic of the SMC. The input signal **smc\_mclk0** and its inverse **smc\_mclk0** drive this domain. Each external static memory chip is driven by a gated **smc\_mclk0** signal, these are called **smc\_clk\_out\_0[3:0]**. Clocks are only driven out to chips that require them. The static memory interface has a fed back clock input, **smc\_fbclk\_in\_0**, to help with clock skews on the external pads.

The memory controller supports many different options for clocking the different domains:

#### Static memory clocking options

Table 2-1 lists the static memory clocking options.

| т                                                                                       | able 2-1 Static memory clocking options                                  |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Options                                                                                 | Tie-off values                                                           |

| Fully synchronous                                                                       |                                                                          |

| hclk = smc_mclk0                                                                        | <b>smc_async0 = smc_msync0 =</b> 1<br><b>smc_a_gt_m0_sync =</b> 0        |

| Synchronous multiples                                                                   |                                                                          |

| hclk = n x smc_mclk0<br>where:<br>n = integer value                                     | <b>smc_async0</b> = <b>smc_msync0</b> = 1<br><b>smc_a_gt_m0_sync</b> = 0 |

| m x hclk = smc_mclk0<br>where:<br>m = integer value                                     | <pre>smc_async0 = smc_msync0 = 1 smc_a_gt_m0_sync = 1</pre>              |

| Asynchronous                                                                            |                                                                          |

| Extra registers are used to avoid metastabili crossing the asynchronous clock boundary. | ity when $smc_async0 = smc_msync0 = 0$<br>$smc_a_gt_m0_sync = 0$         |

#### 2.3.4 Low-power interface operation

The memory controller has two low-power interfaces. These interfaces indicate whether the clock for a specific domain can be switched off to reduce power consumption. It is expected that these interfaces are controlled by a system clock controller. One interface controls each of the following domains:

- AHB clock domain

- static memory clock domain.

Each domain uses a simple three signal interface to indicate whether the clocks are required. The signals consist of:

#### a request input

<domain>\_csyreq

#### an acknowledge output

<domain>\_csysack

#### an active output

#### <domain>\_cactive

Where:

<domain> is abb or smc.

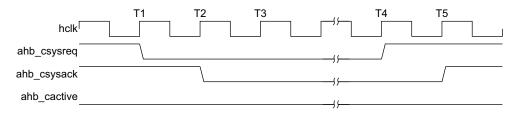

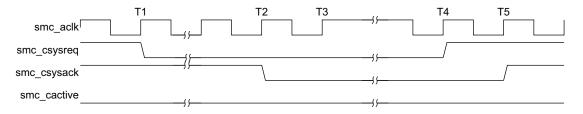

Figure 2-7 explains the protocol for the interface by showing a request to enter low-power mode.

#### Figure 2-7 Request to enter low-power mode

The memory controller receives a request to enter low-power mode, indicated by <domain>\_csysreq being driven LOW by the system clock controller, as shown at T1. The memory controller then has the chance to perform any required operations to prepare for the clock to be switched off. The memory controller acknowledges the request by asserting <domain>\_csysack LOW, as shown at T2. At this point the <domain>\_cactive signal is used to indicate whether the request has been accepted or denied. If the request is accepted, <domain>\_cactive is LOW, as shown in Figure 2-7. If the request is denied, <domain>\_cactive is HIGH. If the request is accepted, then the clock to that domain can be switched off. The peripheral is brought out of low-power state by restarting the clock and driving <domain>\_csysreq HIGH, as shown at T4. The memory controller completes the handshake by driving <domain>\_csysack HIGH, as shown at T5. Figure 2-8 shows the AHB domain denying a low-power request.

#### Figure 2-8 AHB domain denying a low-power request

When **ahb\_csysack** is asserted LOW, the **ahb\_cactive** signal is HIGH, as shown at T3, indicating the AHB domain is busy and the clock cannot be switched off. The handshake must be completed.

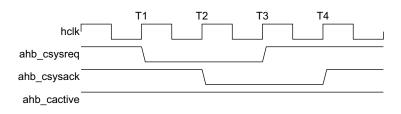

The AHB domain accepts or denies requests based on whether it is busy performing any transfers. Figure 2-9 shows that static memory controllers always accept requests after they have performed the required operations to prepare the external memory for the clock to be switched off.

#### **Figure 2-9 Accepting requests**

The low-power request **smc\_csysreq** is driven LOW at time T1. When the memory controller is happy for the clock to be switched off, the **smc\_csysack** signal is driven LOW to acknowledge the request, as shown at T2. **smc\_cactive** is driven LOW, so the system clock controller knows the request has been accepted. When acknowledged, the system clock controller can disable both the **smc\_aclk** and **smc\_mclk0** signals.

The two domains have separate interfaces to enable individual handshaking with the system clock controller. The only usage model is to switch off both domains. Each individual low-power interface protocol must be observed before all the clocks can be disabled.

## 2.4 SMC functional operation

This section describes:

- **Operating** states

- Clocking and resets on page 2-16

- *Miscellaneous signals* on page 2-18

- *APB slave interface operation* on page 2-19

- Format block on page 2-19

- *Memory manager operation* on page 2-22

- *Interrupts operation* on page 2-27

- *Memory interface operation* on page 2-27.

#### 2.4.1 Operating states

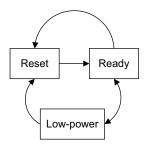

The operation of the SMC is based on three operating states. In this section, each state is described. Figure 2-10 shows the state machine.

#### Figure 2-10 SMC aclk domain FSM

The SMC states are as follows:

- **Reset** Power is applied to the device, and **hresetn** is held LOW.

- **Ready** Normal operation of the device. You can access the SMC register bank through the AHB configuration port and external memory devices accessed through the SMC interface.

- **Low-power** The device does not accept new AHB transfers, and only certain registers are accessible through the APB interface. You can stop the SMC clocks to reduce power consumption.

The state transitions are:

#### **Ready to Reset**

When reset is asserted to the **smc\_aclk** domain, it enters the Reset state.

#### **Reset to Ready**

When reset is deasserted to the **smc\_aclk** domain, it enters the Ready state.

#### **Ready to Low-power**

The Low-power state is entered when the SMC next becomes idle after either:

- the SMC receives a low-power request through the APB smc\_memc\_cfg\_set Register

- the SMC receives a low-power request through the SMC low-power interface.

#### Low-power to Ready

The SMC exits the Low-power state back to Ready when either:

- the SMC low-power request bit is cleared in the APB smc\_memc\_cfg\_clr Register

- the SMC low-power interface negates the low-power request.

#### Low-power to Reset

When Reset is asserted to the **smc\_aclk** reset domain, it enters the Reset state.

#### 2.4.2 Clocking and resets

This section describes:

- Clocking

- *Resets* on page 2-17.

#### Clocking

All configurations of the SMC support at least two clock domains, and have the following clock inputs:

- smc\_aclk

- smc\_mclk0

- smc\_mclk0n.

These clocks can be grouped into two clock domains:

AHB domain smc\_aclk is in this domain. You can only stop the smc\_aclk domain signals when the SMC is in low-power mode.

#### Memory clock domain

The **smc\_mclk0** and **smc\_mclk0n** are in this domain. **smc\_mclk0n** is an inverted version of **smc\_mclk0**. **smc\_mclk0** is used for timing and control signals.

You can tie off the **smc\_async** and **smc\_msync** pins so that the **smc\_aclk** and **smc\_mclk0** clock domains can operate synchronously or asynchronously with respect to each other.

#### Synchronous clocking

The benefit of synchronous clocking is that you can reduce the read and write latency by removing the synchronization registers between clock domains. However, because of the integer relationship of the clocks, you might not be able to get the maximum performance from the system because of constraints placed on the bus frequency by the external memory clock speed. In synchronous mode, the handshaking between the **smc\_aclk** and **smc\_mclk0** domains enables synchronous operation of the two clocks at multiples of each other, that is, ratios of n:1 and 1:m.

#### Asynchronous clocking

The main benefit of asynchronous clocking is that you can maximize the system performance, while running the memory interface at a fixed system frequency. Additionally, in sleep-mode situations when the system is not required to do much work, you can lower the frequency to reduce power consumption.

#### **Output clocks**

A clock output is provided for every external memory device on the SRAM memory interface type.

#### Resets

The SMC has two reset inputs:

hresetn This is the reset signal for the smc\_aclk domain.

#### smc\_mreset0n

This is the reset signal for the **smc\_mclk0** domain.

You can change both reset signals asynchronously to their respective clock domain. Internally to the SMC the deassertion of the **hresetn** signal is synchronized to **smc\_aclk**. The deassertion of **smc\_mreset0n** is synchronized internally to **smc\_mclk0** and **smc\_mclk0n**.

#### 2.4.3 Miscellaneous signals

You can use the following signals as general-purpose control signals for logic external to the SMC:

#### smc\_user\_config[7:0]

General purpose output ports that are driven directly from the write-only APB register. If you do not require these ports leave them unconnected. See also the *SMC User Configuration Register at 0x1204* on page 3-19.

#### smc\_user\_status[7:0]

General purpose input ports that are readable from the APB interface through the smc\_user\_status Register. If you do not require these ports then tie them either HIGH or LOW. These ports are connected directly to the APB interface block. Therefore, if they are driven from external logic that is not clocked by the SMC **smc\_aclk** signal, then you require external synchronization registers. See also the *SMC User Status Register at 0x1200* on page 3-18.

You can use the following miscellaneous signals as tie-offs to change the operational behavior of the SMC:

#### smc\_a\_gt\_m0\_sync

When HIGH, indicates that **smc\_aclk** is greater than and synchronous to **smc\_mclk0**.

smc\_async0 When HIGH, indicates smc\_aclk is synchronous to smc\_mclk0. Otherwise they are asynchronous. Ensure that smc\_async0 is tied to the same value as smc\_msync0.

#### smc\_dft\_en\_clk\_out

Use this signal for *Automatic Test Pattern Generator* (ATPG) testing only. Tie it LOW for normal operation.

#### smc\_msync0

When HIGH, indicates **smc\_mclk0** is synchronous to **smc\_aclk**. Otherwise they are asynchronous. Ensure that **smc\_msync0** is tied to the same value as **smc\_async0**.

#### smc\_rst\_bypass

Use this signal for ATPG testing only. Tie it LOW for normal operation.

#### smc\_use\_ebi

When HIGH, indicates that the SMC must operate with a PrimeCell EBI. See the *ARM PrimeCell External Bus Interface (PL220) Technical Reference Manual.*

#### 2.4.4 APB slave interface operation

To enable a clean registered interface to the external infrastructure, the APB interface always adds a wait state for all reads and writes by driving **pready** LOW during the first cycle of the access phase.

In two instances, a delay of more than one wait state can be generated:

- when a direct command is received and there are outstanding commands that prevent a new command being stored in the command FIFO

- when an APB access is received and a previous direct command has not completed.

#### 2.4.5 Format block

This section describes:

- Hazard handling

- SRAM memory accesses on page 2-20.

#### Hazard handling

There are four types of hazard:

- Read After Read (RAR)

- Write After Write (WAW)

- *Read After Write* (RAW)

- Write After Read (WAR).

The AHB interface deals with RAW hazards. WAR hazards do not occur in the AHB.

The SMC ensures the ordering of read transfers from a single port is maintained RAR, and additionally that the ordering of write transfers from a single master is maintained WAW.

#### SRAM memory accesses

This section describes:

- Standard SRAM access

- Memory address shifting

- Memory burst alignment

- *Memory burst length* on page 2-21

- Booting using the SRAM on page 2-21.

#### Standard SRAM access

The programmer's view is a flat area of memory.

The base addresses of external memory devices are defined by the **smc\_address\_match0\_<0-3>[7:0]** and **smc\_address\_mask0\_<0-3>[7:0]** tie-off pins. You can read the values of these tie-off pins through the opmode registers.

#### Memory address shifting

To produce the address presented to the memory device, the AHB address is aligned to the memory width. This is done because the AHB address is a byte-aligned address, while the memory address is a memory-width-aligned address.

—— Note ———

During initial configuration of a memory device, the memory mode register can be accessed with a sequence of transfers to specific addresses. You must take into consideration the shifting performance by the SMC when accessing memory mode registers.

#### Memory burst alignment

The SMC provides a programmable option for controlling the formatting of memory transfers with respect to memory burst boundaries, through the burst\_align bit of the opmode registers.

When set, the burst\_align bit causes memory bursts to be aligned to a memory burst boundary. This setting is intended for use with memories that use the concept of internal pages. This can be an asynchronous page mode memory, or a synchronous PSRAM. If a burst crosses a memory burst boundary, the SMC partitions the transfer into multiple memory bursts, terminating a memory transfer at the burst boundary. Also ensure the page size is an integer multiple of the burst length, to avoid a memory burst crossing a page boundary.

When the burst\_align bit is not set, the SMC ignores the memory burst boundary when mapping commands onto memory commands. This setting is intended for use with devices such as NOR flash. These devices have no concept of pages.

#### Memory burst length

The SMC enables you to program the memory burst length on an individual chip basis, from length 1 to 32 beats, or a continuous burst. However, the length of memory bursts are limited by the size of the read and write data FIFOs, and the programmed memory burst must not exceed this upper limit.

For read transfers, the maximum memory burst length is the depth of the read data FIFO, and it is four. For writes, the burst length is the depth of the write FIFO, and is four.

#### Booting using the SRAM

The SMC enables the lowest SRAM chip select, normally chip 0, to be bootable. To enable SRAM memory to be bootable, the SRAM interface does not require any special functionality, other than knowing the memory width of the memory concerned. This is indicated by a top-level tie-off. To enable the SMC to work with the slowest memories the timing registers reset to the worst case values. When the **smc\_remap\_0** port signal is HIGH, the memory with the bootable chip select is set by the **smc\_sram\_mw\_0[1:0]** tie-off port signal.

Additionally, while the SMC input **smc\_remap\_0** is HIGH, the bootable chip is aliased to base address 0x0.

#### 2.4.6 Memory manager operation

The memory manager module is responsible for controlling the state of the SMC and the updating of chip configuration registers.

This subsection describes:

- Low-power operation

- Chip configuration registers

- *Direct commands* on page 2-24.

### Low-power operation

The SMC accepts requests to enter the Low-power state through either the SMC low-power interface or the APB register interface.

The SMC does not enter the power-down state until it has received an idle indication from all areas of the peripheral, that is:

- there is no valid transfer held in the Format block

- there are no valid transfers held in the SMC interface

- all FIFOs are empty

- all memory interface blocks are IDLE.

When the Low-power state is entered, no new memory transfers are accepted until the SMC has been moved out of Low-power state. The SMC does not request to move out of Low-power state, and never refuses a power-down request.

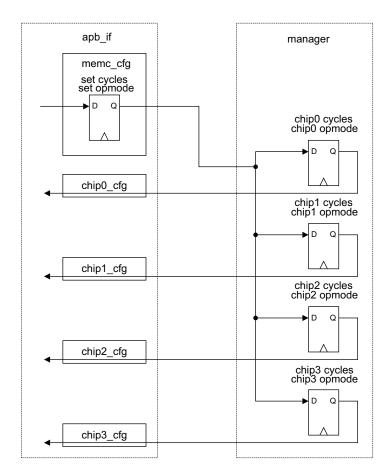

# Chip configuration registers

The SMC provides a mechanism for synchronizing the switching of operating modes of the SMC with that of the memory device.

The smc\_set\_cycles Register and smc\_set\_opmode Register act as holding registers for new operating parameters until the SMC detects the memory device has switched modes.

Figure 2-11 on page 2-23 shows the memory manager containing a bank of registers for each memory chip supported by the SMC. The manager register bank consists of all the timing parameters smc\_sram\_cycles0\_<0-3> and smc\_opmode0\_<0-3>, that are required for the controller to correctly time any type of access to a supported memory type.

The APB registers smc\_set\_cycles and smc\_set\_opmode act as holding registers, the configuration registers within the manager are only updated if either:

- the smc\_direct\_cmd Register indicates only a register update is taking place

- the smc\_direct\_cmd Register indicates either a modereg operation or an memory access has taken place, and is complete.

The chip configuration registers are available as read only registers in the address map of the APB interface.

Figure 2-11 Chip configuration registers

## **Direct commands**

The SMC enables code to be executed from the memory while simultaneously, from the software perspective, moving the same chip to a different operating mode. This is achieved by synchronizing the update of the chip configuration registers from the holding registers with the dispatch of the memory configuration register write.

The SMC provides two mechanisms for simultaneously updating the controller and memory configuration registers.

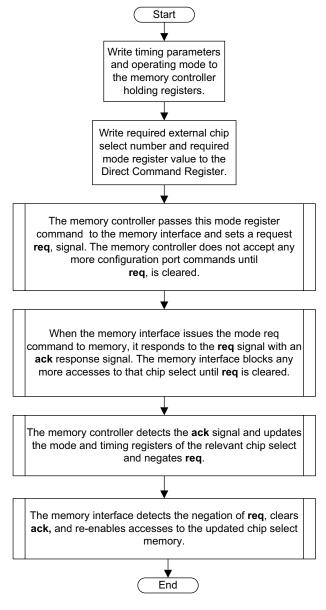

#### Device pin mechanism

For memories that use an input pin to indicate that a write is intended for the configuration register, for example in some PSRAM devices, the write mechanism can be done through the APB direct command register. Figure 2-12 on page 2-25 shows the sequence of events.

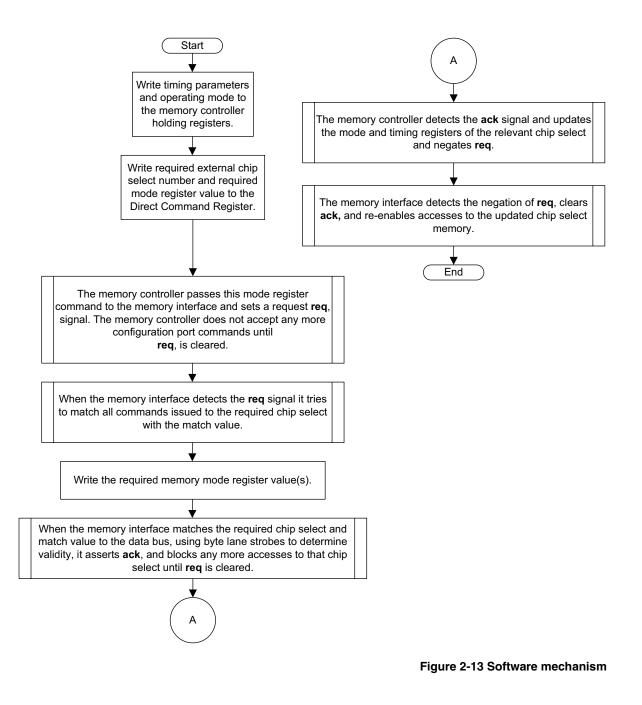

#### Software mechanism

For memories that require a sequence of read and write commands, for example, most NOR Flash devices use the SMC interface, with the write data bus indicating when the last transfer has completed and when it is safe for the SMC to update the chip configuration registers. Figure 2-13 on page 2-26 shows the sequence of events.

Figure 2-12 Device pin mechanism

#### 2.4.7 Interrupts operation

The next read to any chip select on the appropriate memory interface clears the interrupt.

The interrupt outputs are generated through a combinational path from the relevant input pin. This enables you to place the SMC in Low-power state, and to stop the clocks while waiting for an interrupt.

When interrupts are disabled, a synchronized version of the interrupt input is still readable through the APB interface.

#### 2.4.8 Memory interface operation

The memory interface issues commands to the memory from the command FIFO, and controls the cycle timings of these commands. A new command is only issued when the previous command is complete and any turn-around times have been met. Additionally, a read command is not issued unless there is space for all the impending data in the read data FIFO.

#### —— Note ———

You must not set the rd\_bl parameter in the smc\_opmode Register to a value greater than the read data FIFO depth of four.

If enabled, the EBI can prevent commands being issued when the SMC is not granted the external bus.

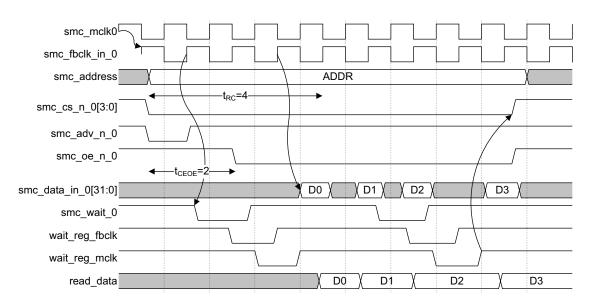

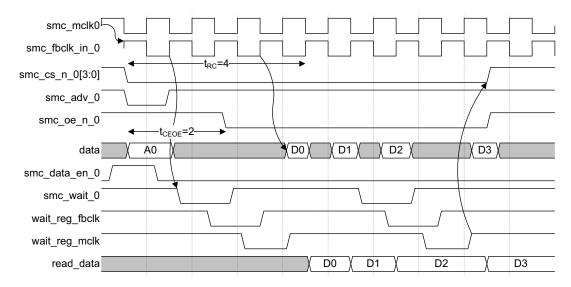

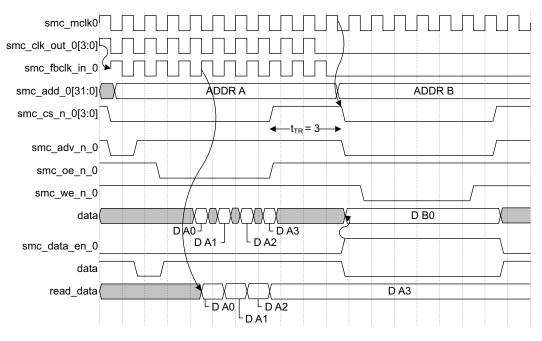

Figure 2-14 on page 2-29 to Figure 2-23 on page 2-38 show the timing parameters. They are divided into *SRAM timing tables and diagrams*.

The internal signal **read\_data** is included in the read transfer waveforms to indicate the clock edge on which data is registered by the SMC.

#### SRAM timing tables and diagrams

All address, control, and write data outputs of the SMC are registered on the rising edge of **smc\_mclk0n**, equivalent to the falling edge of **smc\_mclk0**, for both synchronous and asynchronous accesses. The clock output to memory, **smc\_clk\_out**, is driven directly by **smc\_mclk0**, but gated to prevent toggling during asynchronous accesses, or when no transfers are occurring.

Read data output by the memory device is also registered on the rising edge of **smc\_mclk0n**, equivalent to the falling edge of **smc\_mclk0**, for asynchronous reads. For synchronous reads, read data is registered using the fed back clock, **smc\_fbclk\_in**. For synchronous and asynchronous accesses, the data is then pushed onto the read data FIFO to be returned by the SMC interface.

This subsection describes:

- Asynchronous read

- Asynchronous read in multiplexed-mode on page 2-29

- Asynchronous write on page 2-30

- Asynchronous write in multiplexed-mode on page 2-31

- Asynchronous page mode read on page 2-31

- Synchronous burst read on page 2-32

- Synchronous burst read in multiplexed-mode on page 2-34

- Synchronous burst write on page 2-35

- Synchronous burst write in multiplexed-mode on page 2-36

- Synchronous read and asynchronous write on page 2-37.

#### Asynchronous read

Table 2-2 and Table 2-3 list the smc\_opmode0\_<0-3> and SRAM Register settings. See *Register summary* on page 3-3.

Table 2-2 Asynchronous read opmode chip register settings

| Field | mw | rd_sync | rd_bl | wr_sync | wr_bl | baa | adv | bls | ba |

|-------|----|---------|-------|---------|-------|-----|-----|-----|----|

| Value | -  | b0      | b000  | -       | -     | -   | -   | -   | -  |

#### Table 2-3 Asynchronous read SRAM cycles register settings

| Field | t_rc  | t_wc | t_ceoe | t_wp | t_pc | t_tr |

|-------|-------|------|--------|------|------|------|

| Value | b0011 | -    | b001   | -    | -    | -    |

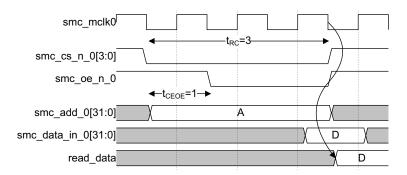

Figure 2-14 on page 2-29 shows a single asynchronous read transfer with an initial access time,  $t_{RC}$ , of three cycles and an output enable assertion delay,  $t_{CEOE}$ , of one cycle.

#### Figure 2-14 Asynchronous read

#### Asynchronous read in multiplexed-mode

Table 2-4 and Table 2-5 list the smc\_opmode0\_<0-3> and SRAM Register settings.

#### Table 2-4 Asynchronous read in multiplexed-mode opmode chip register settings

| Field | mw | rd_sync | rd_bl | wr_sync | wr_bl | baa | adv | bls | ba |

|-------|----|---------|-------|---------|-------|-----|-----|-----|----|

| Value | -  | b0      | b000  | -       | -     | -   | b1  | -   | -  |

#### Table 2-5 Asynchronous read in multiplexed-mode SRAM cycles register settings

| Field | t_rc  | t_wc | t_ceoe | t_wp | t_pc | t_tr |

|-------|-------|------|--------|------|------|------|

| Value | b0111 | -    | b101   | -    | -    | -    |

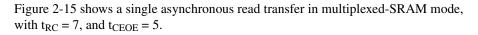

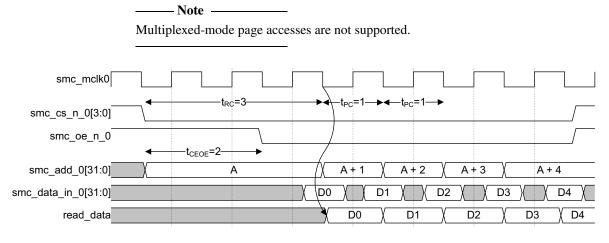

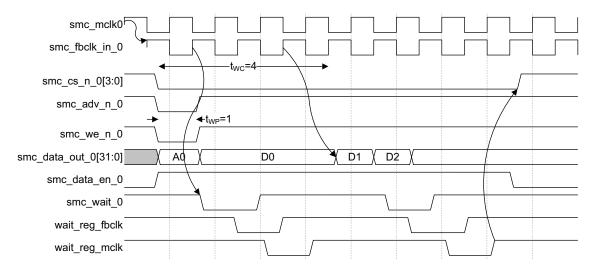

Figure 2-15 Asynchronous read in multiplexed-mode

\_\_\_\_\_Note \_\_\_\_\_

In multiplexed-mode, both address and data are output by the SMC on the **smc\_data\_out\_0[31:0]** output bus. Read data is accepted on the **smc\_data\_in\_0[31:0]** bus.

#### Asynchronous write

Table 2-6 and Table 2-7 list the smc\_opmode0\_<0-3> and SRAM Register settings.

Table 2-6 Asynchronous write opmode chip register settings

| Field | mw | rd_sync | rd_bl | wr_sync | wr_bl | baa | adv | bls | ba |

|-------|----|---------|-------|---------|-------|-----|-----|-----|----|

| Value | -  | -       | -     | b0      | b000  | -   | -   | -   | -  |

Table 2-7 Asynchronous write SRAM cycles register settings

| Field | t_rc | t_wc  | t_ceoe | t_wp | t_pc | t_tr |

|-------|------|-------|--------|------|------|------|

| Value | -    | b0100 | -      | b010 | -    | -    |

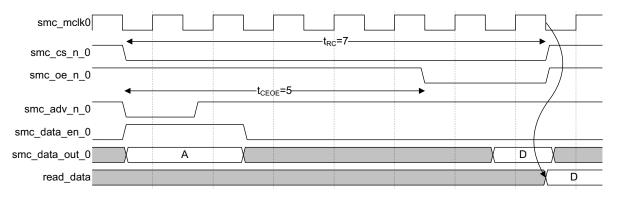

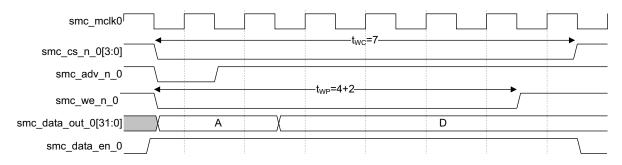

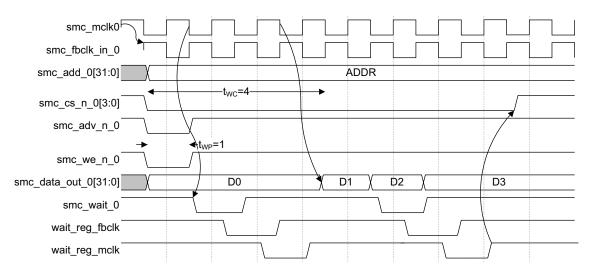

Figure 2-16 shows an asynchronous write with a write cycle time  $t_{WC}$  of four cycles and a **smc\_we\_n\_0** assertion duration,  $t_{WP}$ , of two cycles.

#### — Note ———

The timing parameter  $t_{WC}$  is controlling the deassertion of  $smc_we_n_0$ . You can use it to vary the hold time of  $smc_cs_n_0[3:0]$ ,  $smc_add_0[31:0]$  and  $smc_data_out_0[31:0]$ . This differs from the read case where the timing parameter  $t_{CEOE}$  controls the delay in the assertion of  $smc_oe_n_0$ . Additionally,  $smc_we_n_0$  is always asserted one cycle after smc cs n 0[3:0] to ensure the address bus is valid.

#### Figure 2-16 Asynchronous write

#### Asynchronous write in multiplexed-mode

Table 2-8 and Table 2-9 list the smc\_opmode0\_<0-3> and SRAM Register settings.

Table 2-8 Asynchronous write in multiplexed-mode opmode chip register settings

| Field | mw | rd_sync | rd_bl | wr_sync | wr_bl | baa | adv | bls | ba |

|-------|----|---------|-------|---------|-------|-----|-----|-----|----|