# MCPN750A CompactPCI Single Board Computer

# **Installation and Use**

MCPN750A/IH5

September 2001 Edition

#### © Copyright 2001 Motorola, Inc.

#### All Rights Reserved.

#### Printed in the United States of America.

Motorola and the stylized M logo are registered trademarks of Motorola, Inc.

PowerPC is a registered trademark of International Business Machines and is used by Motorola Inc. under license from IBM Corporation.

CompactPCI is a registered trademark of PCI Industrial Computer Manufacturers Group.

All other product or service names mentioned in this document are trademarks or registered trademarks of their respective holders.

## **Safety Summary**

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result in personal injury or damage to the equipment.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the equipment is supplied with a three-conductor AC power cable, the power cable must be plugged into an approved three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes.

#### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in any explosive atmosphere such as in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage.

#### **Keep Away From Live Circuits Inside the Equipment.**

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified service personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Service personnel should not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, such personnel should always disconnect power and discharge circuits before touching components.

#### Use Caution When Exposing or Handling a CRT.

Breakage of a Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, do not handle the CRT and avoid rough handling or jarring of the equipment. Handling of a CRT should be done only by qualified service personnel using approved safety mask and gloves.

#### Do Not Substitute Parts or Modify Equipment.

Do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that all safety features are maintained.

#### **Observe Warnings in Manual.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

To prevent serious injury or death from dangerous voltages, use extreme caution when handling, testing, and adjusting this equipment and its components.

#### **Flammability**

All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating of 94V-0 by UL-recognized manufacturers.

#### **EMI Caution**

This equipment generates, uses and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used with adequate EMI protection.

#### **Lithium Battery Caution**

This product contains a lithium battery to power the clock and calendar circuitry.

Danger of explosion if battery is replaced incorrectly. Replace battery only with the same or equivalent type recommended by the equipment manufacturer. Dispose of used batteries according to the manufacturer's instructions.

Il y a danger d'explosion s'il y a remplacement incorrect de la batterie. Remplacer uniquement avec une batterie du même type ou d'un type équivalent recommandé par le constructeur. Mettre au rebut les batteries usagées conformément aux instructions du fabricant.

Explosionsgefahr bei unsachgemäßem Austausch der Batterie. Ersatz nur durch denselben oder einen vom Hersteller empfohlenen Typ. Entsorgung gebrauchter Batterien nach Angaben des Herstellers.

#### **CE Notice (European Community)**

This is a Class A product. In a domestic environment, this product may cause radio interference, in which case the user may be required to take adequate measures.

Motorola Computer Group products with the CE marking comply with the EMC Directive (89/336/EEC). Compliance with this directive implies conformity to the following European Norms:

EN55022 "Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment"; this product tested to Equipment Class A

EN55024 "Information Technology Equipment-Immunity characteristics-Limits and methods of measurement"

Board products are tested in a representative system to show compliance with the above mentioned requirements. A proper installation in a CE-marked system will maintain the required EMC/safety performance.

In accordance with European Community directives, a "Declaration of Conformity" has been made and is available on request. Please contact your sales representative.

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to the Motorola Computer Group website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Motorola, Inc.

It is possible that this publication may contain reference to or information about Motorola products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

#### **Limited and Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

# **Contents**

| About This Manual                                       |       |

|---------------------------------------------------------|-------|

| Summary of Changes                                      | xviii |

| Overview of Contents                                    | xviii |

| Comments and Suggestions                                | xviii |

| Conventions Used in This Manual                         | xix   |

| CHAPTER 1 Hardware Preparation and Installation         |       |

| Introduction                                            | 1-1   |

| Product Description                                     | 1-1   |

| Block Diagram                                           |       |

| Getting Started                                         |       |

| Overview of Start-up Procedure                          |       |

| Equipment Required                                      |       |

| Unpacking Instructions                                  |       |

| ESD Precautions                                         | 1-5   |

| Preparation                                             | 1-6   |

| Hardware Configuration                                  | 1-6   |

| MCPN750A Base Board Preparation                         |       |

| Flash Bank Selection (J7)                               | 1-7   |

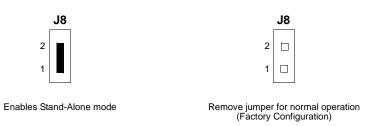

| Stand-Alone Operating Mode (J8)                         | 1-8   |

| System Considerations                                   |       |

| TMCPN710 Transition Module Preparation                  | 1-11  |

| Serial Ports 1 and 2                                    | 1-13  |

| COM3 and COM4 Asynchronous Serial Ports                 | 1-15  |

| TM-PIMC-0001 Transition Module Preparation              | 1-16  |

| COM 1 and COM 2 Asynchronous Serial Ports               | 1-18  |

| COM3 and COM4 Asynchronous Serial Ports                 | 1-20  |

| Hardware Installation                                   |       |

| Installing PMC Modules on the MCPN750A SBC              | 1-21  |

| Installing the MCPN750A Baseboard                       | 1-24  |

| Installing a TMCPN710 or TM-PIMC-0001 Transition Module | 1-26  |

| Installing PIMs on the TM-PIMC-0001 Transition Module   | 1-26  |

| Installing the Transition Module in the Chassis         | 1-28  |

| MCPN750A Module Power Requirements                      | 1-31  |

## **CHAPTER 2** Startup and Operation

| Introduction                      | 2-1  |

|-----------------------------------|------|

| Applying Power                    | 2-1  |

| Memory Maps                       | 2-3  |

| Processor Memory Map              | 2-3  |

| Default Processor Memory Map      |      |

| PCI Local Bus Memory Map          | 2-4  |

| CompactPCI Memory Map             | 2-5  |

| Address Decoding with the 21554   | 2-5  |

| L2 Cache                          | 2-6  |

| System Clock Generator            | 2-6  |

| PPC Bus Arbitration               | 2-6  |

| PCI Host Bridge                   |      |

| PCI Arbitration                   |      |

| Interrupt Handling                |      |

| ISA DMA Channels                  |      |

| Sources of Reset                  |      |

| Power-On Reset                    |      |

| Undervoltage Reset                |      |

| Front Panel Push Button Reset     |      |

| CompactPCI Reset (RST#)           |      |

| Watchdog Timer Reset              |      |

| Software Resets                   |      |

| Reset Source Identification       |      |

| Endian Issues                     |      |

| Processor/Memory Domain           |      |

| PCI Domain                        | 2-13 |

| CHAPTER 3 PPCBug  PPCBug Overview | 3 1  |

| PPCBug Basics                     |      |

|                                   |      |

| Memory Requirements               |      |

| PPCBug Implementation             |      |

|                                   |      |

| Using PPCBug                      |      |

| Debugger Commands                 |      |

| Diagnostic Tests                  | 3-10 |

| CHAPTER 4 CNFG and ENV Commands          |      |

|------------------------------------------|------|

| Overview                                 | 4-1  |

| CNFG - Configure Board Information Block |      |

| ENV - Set Environment                    |      |

| Configuring the PPCBug Parameters        |      |

|                                          |      |

| CHAPTER 5 Remote Start Via the PCI Bus   |      |

| Introduction                             | 5-1  |

| Overview                                 | 5-1  |

| Command/response Register Description    |      |

| Opcode 0x01: Write/Read Virtual Register | 5-5  |

| Opcode 0x02: Initialize Memory           | 5-5  |

| Opcode 0x03: Write/Read Memory           | 5-6  |

| Opcode 0x04: Checksum Memory             | 5-6  |

| Opcode 0x05: Memory Size Query           | 5-7  |

| Opcode 0x06: Debugger Query              | 5-7  |

| Opcode 0x07: Execute Code                |      |

| Command/Response Channel Error Codes     |      |

| Demonstration of the Host Interface      |      |

| Reference Function: srom_crc.c           | 5-12 |

| CHAPTER 6 Functional Description         |      |

| Introduction                             |      |

| Features                                 |      |

| General Description                      |      |

| Block Diagram                            | 6-3  |

| CompactPCI Bus Interface                 | 6-5  |

| Ethernet Interface                       |      |

| PCI Mezzanine Interface                  | 6-7  |

| ISA Bus Devices                          |      |

| Asynchronous Serial Ports                |      |

| Configuration and Status Registers       |      |

| Serial EEPROM                            |      |

| PCI Peripheral Bus Controller (PBC)      |      |

| ISA Interface                            |      |

| EIDE Interface                           |      |

| USB Interface                            |      |

| ISA Interrupt Controller                 | 6-10 |

| ISA DMA Channels6-                                            | 10  |

|---------------------------------------------------------------|-----|

| Interval Timers6-                                             | 11  |

| Real-Time Clock/NVRAM/Watchdog Timer Function 6-              | -11 |

| Replacing Lithium Batteries6-                                 | 12  |

| Hot Swap Control Circuitry6-                                  | 14  |

| Programmable Timers6-                                         | 14  |

| Raven General Purpose Timers6-                                | 14  |

| Raven Watchdog Timers6-                                       | 15  |

| M48T559 Watchdog Timer6-                                      | 15  |

| Interval Timers6-                                             | 16  |

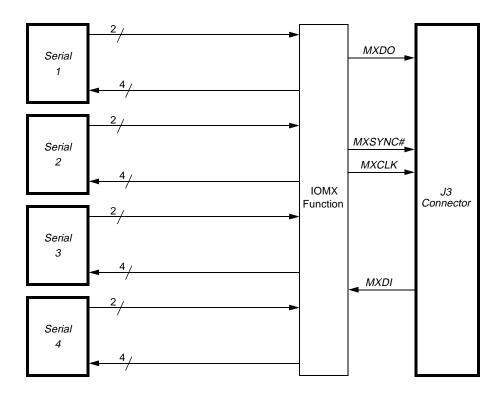

| Serial Port Signal Multiplexing6-                             | -16 |

| I/O Signal Multiplexing (IOMX)6-                              | 17  |

| Signal Descriptions6-                                         | 19  |

| ABORT(ABT)/RESET (RST) Switch (S1)6-                          | 19  |

| Front Panel Indicators (DS1 - DS3)6-                          | 20  |

| MPC750 Processor6-                                            | 20  |

| Raven PCI-Host Bridge6-                                       | 20  |

| Flash Memory6-                                                | 20  |

| JTAG/COP6-                                                    |     |

| Bank A Flash Programming Enable6-                             | 21  |

| ECC Memory Controller6-                                       |     |

| DRAM Memory6-                                                 | 22  |

| Compact FLASH Memory Card6-                                   |     |

| TMCPN710 Transition Module6-                                  |     |

| TM-PIMC-00016-                                                | 23  |

|                                                               |     |

| CHAPTER 7 Connector Pin Assignments                           |     |

| MCPN750A and Transition Module Connectors                     | 7-1 |

| MCPN750A Connector Pin Assignments                            | 7-2 |

| MCPN750A CompactPCI Bus Connectors (J1/J2)                    |     |

| MCPN750A CompactPCI User I/O Connector J3                     |     |

| MCPN750A Connector J4                                         |     |

| MCPN750A CompactPCI User I/O Connector (J5)                   | 7-7 |

| MCPN750A PCI Mezzanine Card Connectors                        |     |

| (J11/21, J12/22, J13/23, J14/24                               | 7-9 |

| MCPN750A 10BaseT/100BaseTx Connector (J18)7-                  |     |

| MCPN750A Debug Connector (J19)7-                              |     |

| MCPN750A Processor RISCWatch Debug Connector (J6)7-           |     |

| TMCPN710 Transition Module7-                                  |     |

| TMCPN710 Transition Module CompactPCI Connectors (J3/J4/J5)7- | 18  |

|    | TMCPN710 Transition Module COM1 Connector (J6)                | 7-19    |

|----|---------------------------------------------------------------|---------|

|    | TMCPN710 Transition Module COM2 Connector (J8)                |         |

|    | TMCPN710 Transition Module COM3 Header (J11)                  | 7-20    |

|    | TMCPN710 Transition Module COM4 Header (J14)                  | 7-21    |

|    | TMCPN710 Transition Module 10BaseT/100BaseTx Connector (J13). | 7-22    |

|    | TMCPN710 Transition Module USB Connectors (J10, J12)          | 7-23    |

|    | TMCPN710 Transition Module IDE Compact FLASH Connectors       |         |

|    | (J15, J16)                                                    | 7-23    |

|    | TMCPN710 Transition Module PMC I/O Connectors (J1/J2)         | 7-25    |

|    | TM-PIMC-0001 Transition Module                                |         |

|    | TM-PIMC-0001 CompactPCI User I/O Connector (J3, J4, & J5)     | 7-27    |

|    | TM-PIMC-0001 Transition Module COM1 Connector (J9)            |         |

|    | TM-PIMC-0001 Transition Module COM2 Connector (J8)            | 7-29    |

|    | TM-PIMC-0001 Transition Module COM3 and COM4 Connectors       |         |

|    | (J12 & J13)                                                   | 7-30    |

|    | TM-PIMC-0001 Transition Module 10BaseT/100BaseTx Connector (J | 7)7-31  |

|    | TM-PIMC-0001 Transition Module IDE Compact FLASH Connector (  | J1)7-31 |

|    | TM-PIMC-0001 Transition Module PMC I/O Connectors             |         |

|    | (J10, J20, and J14/J24)                                       | 7-33    |

| ΑP | PENDIX A Specifications                                       |         |

|    | Specifications                                                | A-1     |

|    | Cooling Requirements                                          |         |

|    | EMC Compliance                                                |         |

|    | Liste compliance                                              | 11 3    |

| ΑP | PENDIX B Related Documentation                                |         |

|    | Motorola Computer Group Documents                             | B-1     |

|    | Manufacturers' Documents                                      |         |

|    | Related Specifications                                        | B-4     |

# **List of Figures**

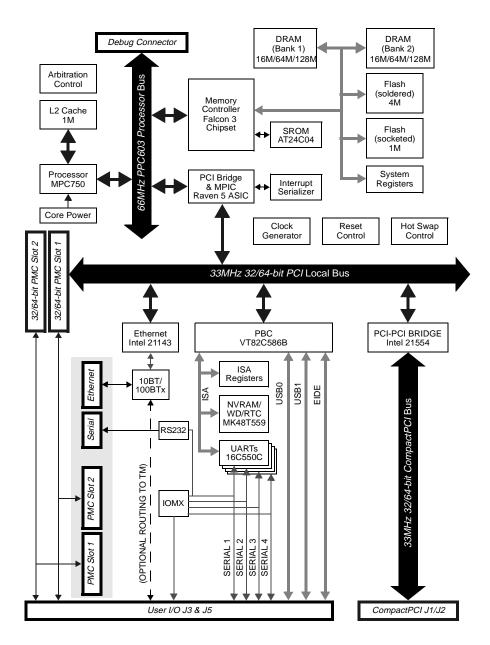

| Figure 1-1. MCPN750A Base Board Block Diagram                   | 1-2        |

|-----------------------------------------------------------------|------------|

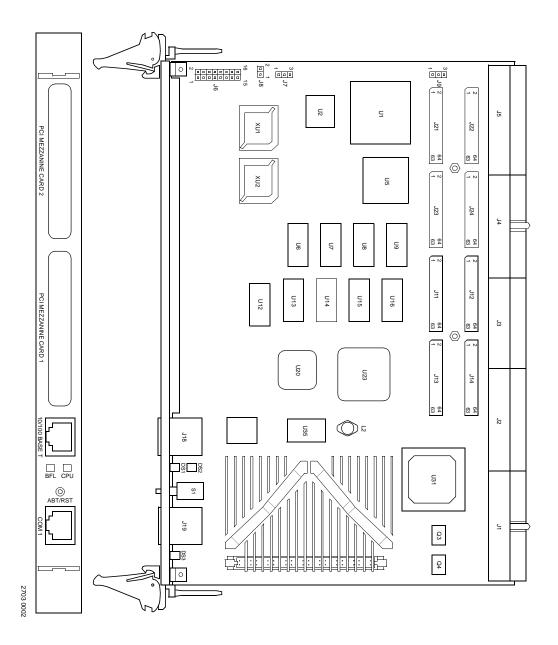

| Figure 1-2. MCPN750A Switches, Headers, Connectors, Fuses, LEDs | 1-9        |

| Figure 1-3. TMCPN710 Connector and Header Locations             | 1-12       |

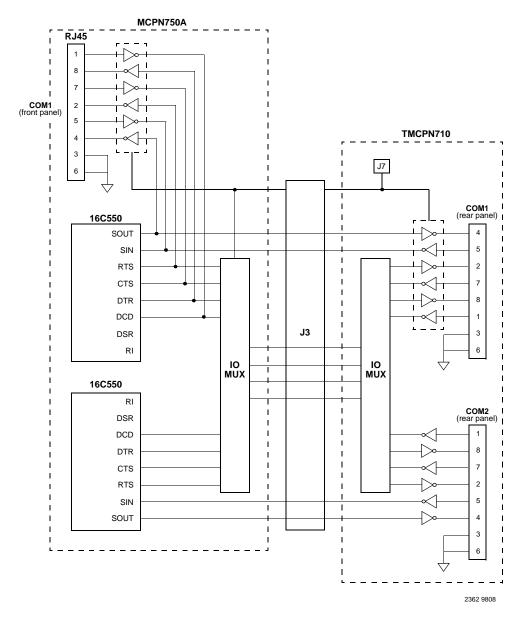

| Figure 1-4. MCPN750A/TMCPN710 Serial Ports 1 and 2              | 1-14       |

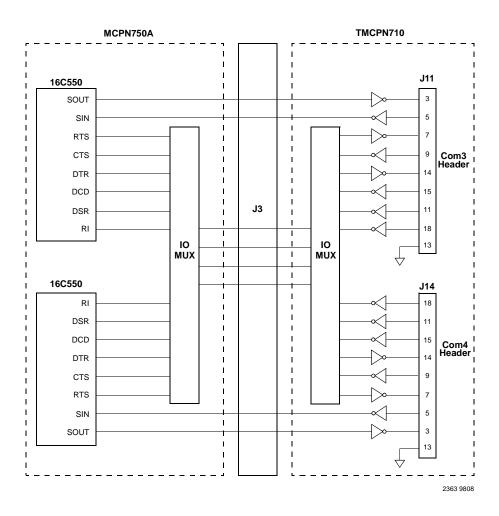

| Figure 1-5. TMCPN710 Serial Ports 3 and 4                       | 1-15       |

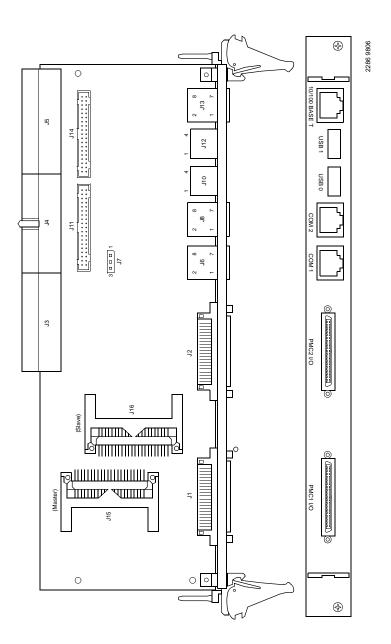

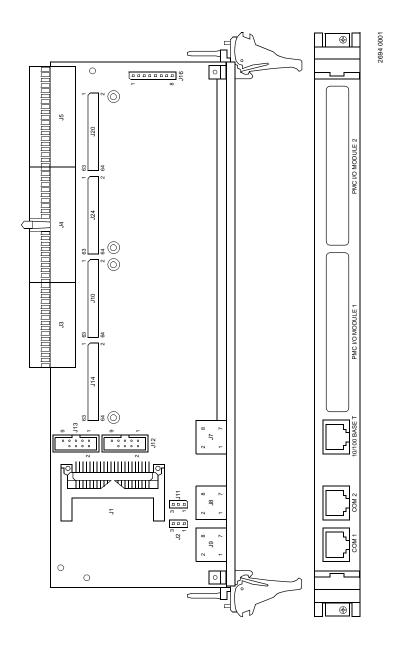

| Figure 1-6. TM-PIMC-0001 Connector and Header Locations         | 1-17       |

| Figure 1-7. MCPN750A/TM-PIMC-0001 Serial Ports 1 and 2          | 1-19       |

| Figure 1-8. TM-PIMC-0001 Serial Ports 3 and 4                   | 1-20       |

| Figure 1-9. PMC Module Placement on MCPN750A                    | 1-22       |

| Figure 1-10. TMCPN710 or TM-PIMC-0001/MCPN750A Mating Configur  | ation 1-30 |

| Figure 2-1. PPCBug System Startup                               | 2-2        |

| Figure 6-1. MCPN750A Block Diagram                              | 6-4        |

| Figure 6-2. Serial Port Signal Multiplexing                     | 6-17       |

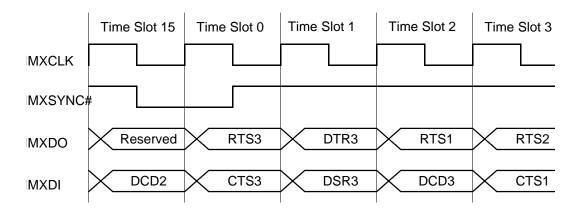

| Figure 6-3. MX Signal Timings                                   | 6-19       |

# **List of Tables**

| Table 1-1. Startup Overview                                       | 1-3  |

|-------------------------------------------------------------------|------|

| Table 1-2. Installing a PIM on the TM-PIMC-0001 Transition Module | 1-27 |

| Table 2-1. Processor Default View of the Memory Map               | 2-3  |

| Table 2-2. Classes of Reset and Effectiveness                     | 2-10 |

| Table 3-1. Debugger Commands                                      | 3-7  |

| Table 3-2. Diagnostic Test Groups                                 | 3-11 |

| Table 5-1. Command/Respond Error Codes                            | 5-8  |

| Table 6-1. MCPN750A Features                                      | 6-1  |

| Table 6-2. Multiplexing Sequence of the MX Function               | 6-18 |

| Table 7-1. MCPN750A J1 CompactPCI Connector                       | 7-2  |

| Table 7-2. MCPN750A J2 CompactPCI Connector                       | 7-3  |

| Table 7-3. MCPN750A J3 User I/O Connector                         | 7-5  |

| Table 7-4. MCPN750A J5 User I/O Connector                         | 7-7  |

| Table 7-5. MCPN750A PCI Mezzanine Card Connector                  | 7-9  |

| Table 7-6. MCPN750A PCI Mezzanine Card Connector                  | 7-10 |

| Table 7-7. MCPN750A 10BaseT/100BaseTx Connector J18               | 7-12 |

| Table 7-8. MCPN750A Debug Connector (J19)                         | 7-13 |

| Table 7-9. MCPN750A RISCWatch Debug Connector (J6)                | 7-17 |

| Table 7-10. TMCPN710 COM1 Connector (J6)                          | 7-19 |

| Table 7-11. TMCPN710 COM2 Connector (J8)                          | 7-20 |

| Table 7-12. TMCPN710 COM3/COM4 Headers                            | 7-20 |

| Table 7-13. TMCPN710 10BaseT/100BaseTx Connector (J13)            | 7-22 |

| Table 7-14. TMCPN710 USB 0 Connector (J10)                        | 7-23 |

| Table 7-15. TMCPN710 USB 1 Connector (J12)                        | 7-23 |

| Table 7-16. TMCPN710 Compact FLASH IDE Connectors                 | 7-24 |

| Table 7-17. TMCPN710 PMC 1 and 2 I/O Connector                    | 7-25 |

| Table 7-18. TM-PIMC-0001 COM1 Connector (J9)                      | 7-28 |

| Table 7-19. TM-PIMC-0001 COM2 Connector (J8)                      | 7-29 |

| Table 7-20. TM-PIMC-0001 COM3 and COM4 Headers                    | 7-30 |

| Table 7-21. TM-PIMC-0001 10BaseT/100BaseTx Connector (J7)         | 7-31 |

| Table 7-22. TM-PIMC-0001 CompactFLASH IDE Connector (J1)          | 7-32 |

| Table 7-23. TM-PIMC-0001 PMC I/O Module 1 (PIM1) - Host I/O       |      |

| Connector Pin Assignments                                         | 7-33 |

| Table 7-24. TM-PIMC-0001 PMC I/O Module 2 (PIM2) - Host I/O       |      |

| Connector Pin Assignments                                         | 7-34 |

| Table 7-25. PMC I/O Modules 1 and 2 (PIM1 and PIM2) - |      |

|-------------------------------------------------------|------|

| PMC I/O Connector Pin Assignments                     | 7-36 |

| Table A-1. MCPN750 Specifications                     | A-1  |

| Table B-1. Motorola Computer Group Documents          | B-1  |

| Table B-2. Manufacturers' Documents                   | B-2  |

| Table B-3. Related Specifications                     | B-4  |

# **About This Manual**

This manual, MCPN750A CompactPCI Single Board Computer Installation and Use (MCPN750A/IH5) provides general information, hardware preparation and installation instructions, operating instructions, firmware information, functional descriptions, and pin assignments for the MCPN750A family of Single Board Computers. In addition, sufficient information is also provided for the two transition modules manufactured by Motorola for use with the MCPN750A (TMCPN710 and TM-PIMC-0001). The document should be used by anyone who wants general, as well as technical information about the MCPN750A products.

**Note:** This revision of the *MCPN750A Installation and Use* manual supersedes all previous versions of this document.

Currently, the boards are provided in the following configurations:

| Part Number     | Description                                                                                   |

|-----------------|-----------------------------------------------------------------------------------------------|

| MCPN750-1222A   | MPC750, 266MHz, 16MB ECC DRAM, 5MB FLASH, 1MB L2 Cache                                        |

| MCPN750-1232A   | MPC750, 266MHz, 32MB ECC DRAM, 5MB FLASH, 1MB L2 Cache                                        |

| MCPN750-1332A   | MPC750, 366MHz, 32MB ECC DRAM, 5MB FLASH, 1MB L2 Cache                                        |

| MCPN750-1342A/B | MPC750, 366MHz, 64MB ECC DRAM, 5MB FLASH, 1MB L2 Cache                                        |

| MCPN750-1352A/B | MPC750, 366MHz, 128MB ECC DRAM, 5MB FLASH, 1MB L2 Cache                                       |

| MCPN750-1362A   | MPC750, 366MHz, 256MB ECC DRAM, 5MB FLASH, 1MB L2 Cache                                       |

| MCPN750-1442A   | MCP750, 466MHz, 64MB ECC DRAM, 5MB FLASH, 1MB L2 Cache                                        |

| MCPN750-2342A/B | MPC750, 366MHz, 64MB ECC DRAM, 5MB FLASH, 1MB L2 Cache, Transition Module, Ethernet Rear I/O  |

| MCPN750-2352A/B | MPC750, 366MHz, 128MB ECC DRAM, 5MB FLASH, 1MB L2 Cache, Transition Module, Ethernet Rear I/O |

| MCPN750-2352A-F | MPC750, 366MHz, 128MB ECC DRAM, 5MB FLASH, 1MB L2 Cache, Transition Module, Ethernet Rear I/O |

| MCPN750-2362A/B | MPC750, 366MHz, 256MB ECC DRAM, 5MB FLASH, 1MB L2 Cache, Transition Module, Ethernet Rear I/O |

## **Summary of Changes**

The following is a list of changes made since the last release of this manual.

| Date  | Changes                                                                                                                                                                                                                                                                                   | Replaces                                            |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 09/01 | Updated table of model numbers preceding this section.  Reinserted information left out of IH4 version of manual, which included information on MCPN750A, the TMCPN710 and the TM-PIMC-0001, instead of the earlier MCPN750. Also, included J8 jumper settings for Stand-Alone operation. | Previously listed model numbers.                    |

|       | 1                                                                                                                                                                                                                                                                                         |                                                     |

| 07/00 | 68-pin .08 Series Subminature D PMC I/O Connector.                                                                                                                                                                                                                                        | 68-pin .050 Series Subminature D PMC I/O Connector. |

## **Overview of Contents**

This section provides a brief overview of each chapter and appendix within this document.

Chapter 1, *Hardware Preparation and Installation*, provides a brief product description and a block diagram. The remainder of the chapter provides information on hardware preparation and installation instructions, including peripheral boards such as the TMCPN710 or TM-PIMC-0001 Transition Module.

Chapter 2, *Startup and Operation*, provides an overview of basic operating and configuring issues such as the PPCBug firmware, the memory maps, interrupts, arbitration, sources of reset and endian issues.

Chapter 3, *PPCBug*, provides an overview and description of basic PPCBug use including implementation issues, a list of the initialization sequence, a description of basic debugger commands, as well as a list of diagnostic tests typically run.

Chapter 4, *CNFG and ENV Commands*, provides an explanation of two of the more important PPCBug configuration commands: CNFG and ENV. Includes information on how to configure the VMEbus and PCI bus environments using the ENV command.

Chapter 5, *Remote Start Via the PCI Bus*, provides a description of the remote start capability that is available via the PCI bus using PPCBug commands.

Chapter 6, *Functional Description*, provides a description of the major components and functionality of the MCPN750A.

Chapter 7, *Connector Pin Assignments*, provides a listing of all major connector pinout information for the MCPN750A, the TMCPN710, and TM-PIMC-0001.

Appendix A, *Specifications*, provides basic board specification information including recommendations on cooling and EMC compliance.

Appendix B, *Related Documentation*, provides a listing of related motorola and vendor documentation, as well as a list of related industry standard specifications.

## **Comments and Suggestions**

Motorola welcomes and appreciates your comments on its documentation. We want to know what you think about our manuals and how we can make them better. Mail comments to:

Motorola Computer Group Reader Comments DW164 2900 S. Diablo Way Tempe, Arizona 85282

You can also submit comments to the following e-mail address: reader-comments@mcg.mot.com

In all your correspondence, please list your name, position, and company. Be sure to include the title and part number of the manual and tell how you used it. Then tell us your feelings about its strengths and weaknesses and any recommendations for improvements.

## **Conventions Used in This Manual**

The following typographical conventions are used in this document:

#### bold

is used for user input that you type just as it appears; it is also used for commands, options and arguments to commands, and names of programs, directories and files.

#### italic

is used for names of variables to which you assign values. Italic is also used for comments in screen displays and examples, and to introduce new terms.

#### courier

is used for system output (for example, screen displays, reports), examples, and system prompts.

#### <Enter>, <Return> or <CR>

<**CR**> represents the carriage return or Enter key.

#### **CTRL**

represents the Control key. Execute control characters by pressing the Ctrl key and the letter simultaneously, for example, **Ctrl-d**.

# Hardware Preparation and Installation

## Introduction

This chapter provides startup and safety instructions related to this product, hardware preparation instructions - including default jumper settings, system considerations, and installation instructions for the baseboard, as well as the PMCs and transition modules associated with this board.

A fully implemented MCPN750A consists of the baseboard plus:

- One or two optional PCI mezzanine cards (PMC) for additional versatility

- □ One of two different types of optional transition modules: the TMCPN710 or the TM-PIMC-0001 for added I/O flexibility

## **Product Description**

The MCPN750A is a hot swappable CompactPCI, non-system slot, single board computer based on the PowerPlus architecture. It consists of the MPC750 processor with L2 cache, the Raven PCI Bridge and Interrupt Controller, the ECC Memory Controller Falcon chipset, 5MB of linear Flash memory, 16MB to 256MB of ECC protected DRAM, interface to a CompactPCI bus, and several I/O peripherals.

## **Block Diagram**

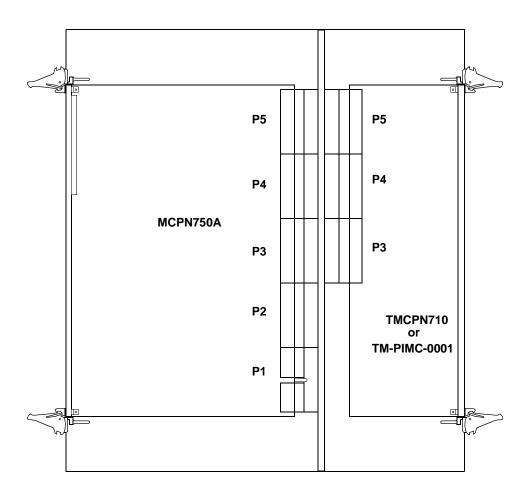

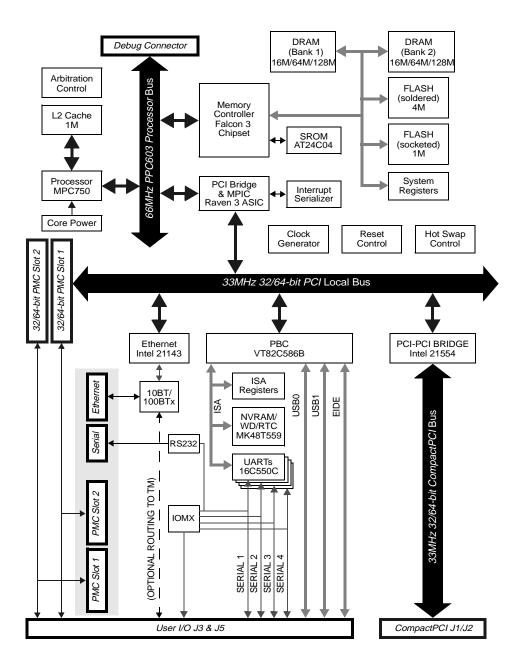

The block diagram in Figure 1-1 illustrates the architecture of the MCPN750A baseboard.

1-1

Figure 1-1. MCPN750A Baseboard Block Diagram

# **Getting Started**

This section provides an overview of the steps necessary to install and power up the MCPN750A, any additional equipment requirements, and a brief section on unpacking and ESD precautions. As identified in the table below, several steps can be omitted if your board, for example, has been shipped with PMCs and Flash already installed

## **Overview of Start-up Procedure**

The following table lists the things you will need to do before you can use this board and tells where to find the information you need to perform each step. Be sure to read this entire chapter, including all Caution and Warning notes, before you begin.

**Table 1-1. Startup Overview**

| Task                                                                              | Section or Manual Reference                                                                                     | Page                   |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------|

| Unpack the hardware.                                                              | Unpacking Instructions                                                                                          | 1-5                    |

| Configure the hardware by setting jumpers on the baseboard and transition module. | MCPN750A Baseboard Preparation and<br>TMCPN710 or TM-PIMC-0001 Transition Module<br>Preparation                 | 1-6, 1-11,<br>and 1-16 |

| Ensure CompactFlash card is installed (if required)                               | Compact Flash Memory Card Installation                                                                          | 1-6                    |

| Install the PMC Module (if required)                                              | PMC Module Installation                                                                                         | 1-21                   |

| Install the MCPN750A in the chassis.                                              | MCPN750A CompactPCI SBC Installation                                                                            | 1-24                   |

| Install the transition module in the chassis.                                     | TMCPN710 or TM-PIMC-0001 Transition Module<br>Installation                                                      | 1-26                   |

| Connect any other equipment                                                       | Connector Pin Assignments                                                                                       | 7-1                    |

| you will be using.                                                                | For more information on optional devices and equipment, refer to the documentation provided with the equipment. |                        |

| Power up the system.                                                              | Applying Power                                                                                                  | 2-1                    |

**Table 1-1. Startup Overview (Continued)**

| Task                                               | Section or Manual Reference                                                                                                | Page           |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------|

| Note that the debugger initializes                 | Using PPCBug                                                                                                               | 3-5            |

| the MCPN750A                                       | You may also wish to obtain the PPCBug Firmware Package User's Manual, listed in Appendix B, Related Documentation.        | B-1            |

| Initialize the system clock.                       | Using the Debugger, Debugger Commands, the SET command                                                                     | 3-6            |

| Examine and/or change environmental parameters.    | CNFG and ENV Commands                                                                                                      | 4-2<br>and 4-3 |

| Program the board as needed for your applications. | MCPN750A CompactPCI Single Board Computer<br>Programmer's Reference Guide, listed in Appendix<br>B, Related Documentation. | B-1            |

## **Equipment Required**

The following equipment is required to complete an MCPN750A system:

- □ CompactPCI system enclosure

- □ System console terminal

- ☐ Operating system (and/or application software)

- □ Disk drives (and/or other I/O) and controllers

- □ Transition module (TMCPN710 or TM-PIMC-0001) and connecting cables

MCPN750A baseboards are factory-configured for I/O handling via a TMCPN710 or TM-PIMC-0001 transition module. There are currently eight MCPN750A models corresponding to the five separate memory configurations, two processor speeds and front or rear ethernet I/O. Either one of the aforementioned transition modules support all models of the baseboard. Refer to the subsections on the MCPN750A and transition module installation for more information.

## **Unpacking Instructions**

Note

If the shipping carton is damaged upon receipt, request that the carrier's agent be present during the unpacking and inspection of the equipment.

Unpack the equipment from the shipping carton. Refer to the packing list and verify that all items are present. Save the packing material for storing and reshipping of equipment.

Avoid touching areas of integrated circuitry; static discharge can damage circuits.

#### **ESD Precautions**

Motorola strongly recommends that you use an antistatic wrist strap and a conductive foam pad when installing or upgrading a system. Electronic components, such as disk drives, computer boards, and memory modules, can be extremely sensitive to ESD. After removing the component from the system or its protective wrapper, place the component flat on a grounded, static-free surface (and in the case of a board, component side up). Do not slide the component over any surface.

If an ESD station is not available, you can avoid damage resulting from ESD by wearing an antistatic wrist strap (available at electronics stores) that is attached to an unpainted metal part of the system chassis.

Inserting or removing modules with power applied may result in damage to module components.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

## **Preparation**

This section discusses certain hardware and software tasks that may need to be performed prior to installing the board in a CompactPCI chassis.

## **Hardware Configuration**

To produce the desired configuration and ensure proper operation of the MCPN750A, you may need to carry out certain hardware modifications before installing the module.

The MCPN750A provides software control over most options by setting bits in control registers after installing the module in a system. You can also modify the board's configuration by modifying similar control registers. The MCPN750A control registers are described in the MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide (MCPN750A/PG), which can be accessed on line in pdf or html format through the Motorola Computer Group Literature web site (http://www.motorola.com/computer/literature).

Some options, however, are not software-programmable. These options are controlled by installing or removing header jumpers or interface modules on the baseboard or the associated transition module.

## MCPN750A Baseboard Preparation

Figure 1-2 illustrates the placement of the switches, jumper headers, connectors, and LED indicators on the MCPN750A. Manually configured items on the baseboard include:

- □ Flash bank selection (J7)

- □ Stand-Alone Operating Mode (J8)

For a discussion of the configured items on the transition module, refer in this chapter to the sections titled *TMCPN710 Transition Module Preparation*, or to the respective user's manuals for the transition modules (listed in the *Related Documentation* appendix) as necessary.

The MCPN750A is factory tested and shipped with the configurations described in the following sections. The MCPN750A's required and factory-installed debug monitor, PPCBug, operates with those factory settings.

#### Flash Bank Selection (J7)

The MCPN750A baseboard has provision for 1MB of 16-bit Flash memory and 4MB of linear Flash memory.

The Flash memory is organized in two banks, Bank A is 64 bits wide and Bank B is 16 bits wide. Bank B contains the onboard debugger, PPCBug.

To enable Flash Bank A, place a jumper across header J7 pins 1 and 2. To enable Flash Bank B (1MB of firmware located in sockets on the baseboard), place a jumper across header J7 pins 2 and 3.

Flash Bank A Enabled (4MB Soldered)

Flash Bank B Enabled (1MB, Sockets) (Factory Configuration)

**Note** Placing a jumper on Flash programming header J9 has no affect. The Flash programming for Bank A is permanently enabled with onboard resistors.

#### **Stand-Alone Operating Mode (J8)**

The MCPN750A has a stand-alone operating mode that allows the MCPN750A to function without the clock from the system slot controller board. Installing a jumper across pins 1 and 2 of J8 enables the stand-alone mode. The J8 jumper must be removed for normal operation.

Note An MCPN750A configured for stand-alone mode should not be installed in a chassis with a system slot controller board. This will result in unpredictable system operation. See the section on *System Considerations* for additional information.

Figure 1-2. MCPN750A Switches, Headers, Connectors, Fuses, LEDs

## **System Considerations**

The MCPN750A is designed to operate as a CompactPCI non-system slot board. Consequently, the MCPN750A must be installed in the subrack system slot marked with the circle symbol.

The MCPN750A can operate properly, with or without a system slot controller board. In the standard operating mode (with a system slot board), the system slot board is used to provide clock and arbitration signals to the MCPN750A. In the stand-alone mode, a jumper must be set on the MCPN750A, in order to obtain clock signals from other on-board devices.

Installing a jumper on J8 routes an onboard PCI clock to the 21554 primary side clock input. This allows the MCPN750A to operate in a chassis without a system slot controller board installed. The chassis must provide +5V, +3.3V, +12V, -12V and VIO to the MCPN750A, and the BD\_SEL pin (P1-D15) in the chassis must be grounded. In addition, in the standalone mode, the MCPN750A cannot communicate over the CompactPCI backplane.

On the MCPN750A baseboard, the standard serial console port (COM1) serves as the PPCBug debugger console port. The firmware console should be set up as follows:

- □ Eight bits per character

- One stop bit per character

- □ Parity disabled (no parity)

- □ Baud rate of 9600 baud

9600 baud is the power-up default for serial ports on MCPN750A boards. After power-up you can reconfigure the baud rate if you wish, using the PPCBug **PF** (Port Format) command via the command line interface. Whatever the baud rate, some type of hardware handshaking — either XON/OFF or via the RTS/CTS line — is desirable if the system supports it.

## **TMCPN710 Transition Module Preparation**

The TMCPN710 transition module (Figure 1-3) is used in conjunction with all models of the MCPN750A baseboard:

The features of the TMCPN710 include:

- □ Two EIA-232-D asynchronous serial ports (identified as COM1 and COM2 on the transition module panel)

- ☐ Two USB Series A connectors for USB interface

- □ One 10/100BaseT connector for ethernet connections (requires MCPN750A Transition module/ethernet option)

- □ Two 68-pin .08 Series Subminiature D connectors for PMC I/O

- ☐ Two 50-pin on-board connectors for EIDE interface to one or two Compact Flash plug-in modules

Figure 1-3. TMCPN710 Connector and Header Locations

#### Serial Ports 1 and 2

On the TMCPN710, the asynchronous serial ports (Serial Ports 1 and 2) are configured permanently as data circuit-terminating (Figure 1-4) equipment (DTE). The COM1 port is also routed to a RJ-45 connector on the front panel of the processor board. A terminal for COM1 may be connected to either the processor board or the transition module, but not both.

Jumper J7 on the transition module must be configured to enable COM1 on either the transition module or the processor board. To enable the COM1 port on the transition module, connect pins 2-3 of J7. To enable COM1 on the processor board, connect pins 1-2 of J7.

**Note** If the J7 jumper is not present on the TMCPN710, the board automatically enables COM1 on the MCPN750A.

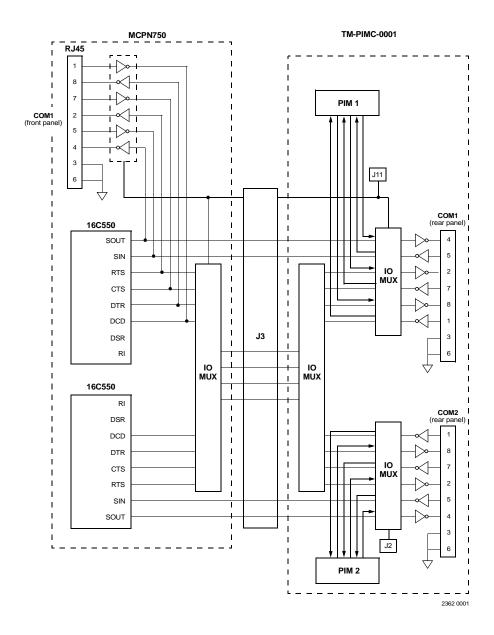

Figure 1-4. MCPN750A/TMCPN710 Serial Ports 1 and 2

#### **COM3 and COM4 Asynchronous Serial Ports**

The signals for COM3 and COM4 serial ports are routed to headers on the TMCPN710 Transition Module. These headers are intended for debug purposes only. Figure 1-5 depicts this configuration.

Figure 1-5. TMCPN710 Serial Ports 3 and 4

## TM-PIMC-0001 Transition Module Preparation

The TM-PIMC-0001 transition module (Figure 1-6) is used in conjunction with all models of the MCPN750A baseboard. The features of this transition module include:

- □ Connections for two single wide, or one double wide PIM card.

- □ Two asynchronous serial ports using RJ-45 connectors labeled as COM1 and COM2.

- ☐ Two asynchronous serial ports using 10-pin headers labeled as COM3 and COM4.

- □ One ethernet port using an RJ-45 connector

- □ One IDE Flash connector using a standard 50-pin CompactFlash socket.

Figure 1-6. TM-PIMC-0001 Connector and Header Locations

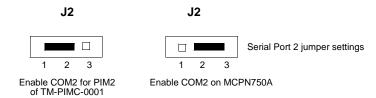

#### **COM1 and COM2 Asynchronous Serial Ports**

On the TM-PIMC-0001, the asynchronous serial ports (COM1 and COM2) are configured permanently as data circuit-terminating (Figure 1-7) equipment (DTE). The COM1 port is also routed to an RJ45 connector on the front panel of the processor board. A terminal for COM1 may be connected to either the processor board or the transition module, but not both.

Jumper J11 on the transition module must be configured to enable COM1 on the processor board. If J11 is not configured, COM1 is automatically routed to PIM 1 on the transition module. Jumper J2 on the transition module must be configured in the same way for the COM2 port.

Figure 1-7. MCPN750A/TM-PIMC-0001 Serial Ports 1 and 2

#### **COM3 and COM4 Asynchronous Serial Ports**

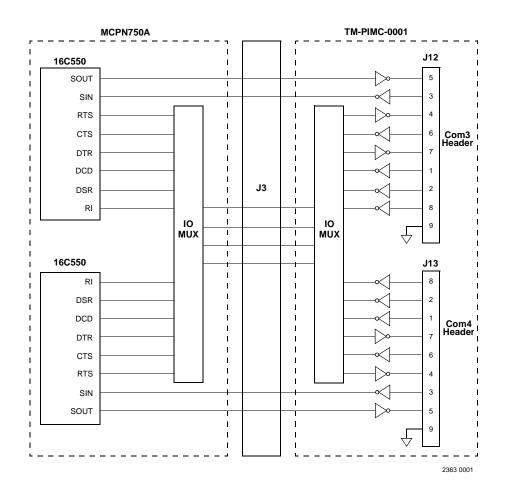

The signals for COM3 and COM4 serial ports are routed to 10-pin headers on the TM-PIMC-0001 Transition Module (J12 and J13). These headers function as I/O connectors for the MCPN750A and are permanently configured as DTE. Figure 1-8 depicts this configuration.

Figure 1-8. TM-PIMC-0001 Serial Ports 3 and 4

## Hardware Installation

The following sections discuss the placement of PMC mezzanine cards on the MCPN750A baseboard and the installation of the complete MCPN750A assembly into a CompactPCI chassis. Before installing the MCPN750A, ensure that all header jumpers are configured as desired.

In most cases, PMC modules ordered with the baseboard are installed on the MCPN750A at the factory and the order is shipped as a single unit. The user-configured jumpers on the PMCs are accessible with the mezzanines installed.

If it is necessary to install mezzanines on the baseboard, refer to the following sections for a brief description of the installation procedure. Note: the procedure assumes the MCPN750A has already been installed in the chassis. If not, begin with Step 4.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

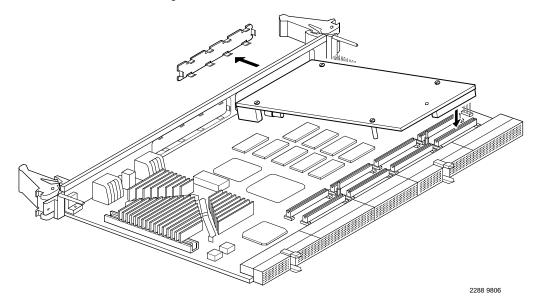

## Installing PMC Modules on the MCPN750A SBC

One dual wide, one single wide or two single wide PCI mezzanine (PMC) modules can be mounted on top of the MCPN750A baseboard. The MCPN750A is designed to accept only +5V or Universal PMCs. Due to pin current limitations, the MCPN750A can supply up to 4.5 amps to a single PMC on each of the +3.3V and +5V supplies. The MCPN750A can supply a maximum of 500mA at +12V and -12V to each PMC. Refer to the table on page 1-31 for the total current available to PMC's and transition modules. To install a PMC module, refer to Figure 1-9 PMC Carrier Board Placement on MCPN750A, and proceed as follows:

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

- 2. Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system.

3. Remove chassis or system cover(s) as necessary for access to the CompactPCI.

Figure 1-9. PMC Module Placement on MCPN750A

Inserting or removing modules in a non-hot swap chassis with power applied may result in damage to module components. The MCPN750A is a hot swappable board and may be inserted in a hot swap chassis, such as a CPX2000 or a CPX8000 series chassis with power applied.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

4. Carefully remove the MCPN750A from its CompactPCI card slot and lay it flat, with connectors J1 through J5 facing you.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

- 5. Remove the PMC filler from the front panel of the MCPN750A.

- 6. Slide the edge connector of the PMC module into the front panel opening from behind and place the PMC module on top of the baseboard. The four connectors on the underside of the PMC module should then connect smoothly with the corresponding connectors (J11/12/13/14) on the MCPN750A.

- 7. Insert the four short Phillips screws, provided with the PMC, through the holes on the bottom side of the MCPN750A into the PMC front bezel and rear standoffs. Tighten the screws.

- 8. Reinstall the MCPN750A assembly in its proper card slot. Be sure the module is well seated in the backplane connectors. Do not damage or bend connector pins.

- 9. Replace the chassis or system cover(s), reconnect the system to the AC or DC power source, and turn the equipment power on.

**Note** If the PMC provides rear I/O, refer to Chapter 7, *Connector Pin Assignments* for the pin assignments. Connectors on the TMCPN710 and TM-PIMC-0001 provide rear panel access to these signals.

## Installing the MCPN750A Baseboard

With mezzanine board(s) installed (if applicable) and headers properly configured, proceed as follows to install the MCPN750A in the CompactPCI chassis:

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

- In a non-hot swap system, perform an operating system shutdown.

Turn the AC or DC power off and remove the AC cord or DC power

lines from the system. Remove chassis or system cover(s) as

necessary for access to the CompactPCI modules.

Inserting or removing modules in a non-hot swap chassis with power applied may result in damage to module components. The MCPN750A is a hot swappable board and may be inserted in a hot swap chassis such as a CPX2000, or a CPX8000 series chassis with power applied.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

- 3. Remove the filler panel from the appropriate non-system card slot.

- 4. Set the VIO on the backplane to either +3.3V or +5V (the MCPN750A is a Universal board), depending upon your cPCI system signaling requirements and ensure the backplane does not bus J3, or J5 signals.

- 5. Slide the MCPN750A into the appropriate non-system slot. Grasping the top and bottom injector handles, be sure the module is well seated in the P1 through P5 connectors on the backplane. Do not damage or bend connector pins.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits

- 6. Secure the MCPN750A in the chassis with the screws provided, making good contact with the transverse mounting rails to minimize RF emissions.

- 7. Replace the chassis or system cover(s), making sure no cables are pinched. Cable the peripherals to the panel connectors, reconnect the system to the AC or DC power source, and turn the equipment power on.

## Installing a TMCPN710 or TM-PIMC-0001 Transition Module

The TMCPN710 or TM-PIMC-0001 Transition Module may be required to complete the configuration of your particular MCPN750A system. If so, perform the following install steps to install this board. For more detailed information on the TMCPN710 or TM-PIMC-0001 Transition Module refer to the corresponding users guide, i.e., *TMCPN710 Transition Module Installation and Use* (TMCPN710A/IH) or *TM-PIMC-0001 Transition Module Installation and Use* (TMPIMCA/IH) manual.

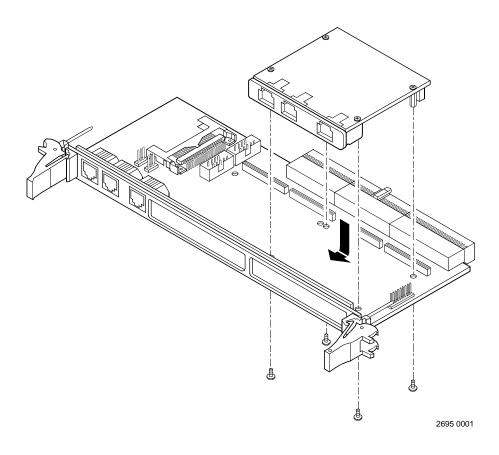

#### Installing PIMs on the TM-PIMC-0001 Transition Module

If PIMs have already been installed on the TM-PIMC-0001, or you are installing a transition module as it has been shipped from the factory, disregard this section, and proceed to the main installation section titled "Installing the Transition Module in the Chassis." For PIM installation perform the following steps:

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

- 2. Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system.

- 3. Remove chassis or system cover(s) as necessary for access to the CompactPCI.

Figure 1-10. Installing a PIM on the TM-PIMC-0001 Transition Module

Inserting or removing modules in a non-hot swap chassis with the power applied may result in damage to the module components. The TM-PIMC-0001 is not a hot swap board, but it may be installed in a hot swap chassis with power applied, if the corresponding MCPN750A is removed before the TM-PIMC-0001 board is installed.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

- 4. Carefully remove the TM-PIMC-0001 from its CompactPCI card slot and lay it flat on a stable surface.

- 5. Remove the PIM filler from the front panel of the TM-PIMC-0001 transition module.

- 6. Slide the face plate (front bezel) of the PIM module into the front panel opening from behind and place the PIM module on top of the transition module, aligned with the appropriate two PIM connectors. The two connectors on the underside of the PIM module should then connect smoothly with the corresponding connectors (J10/J14 or J20/J24) on the TM-PIMC-0001.

- 7. Insert the four short Phillips screws, provided with the PIM, through the holes on the bottom side of the TM-PIMC-000 into the PIM front bezel and rear standoffs. Tighten the screws.

- 8. Reinstall the TM-PIMC-0001 assembly in its proper card slot. Be sure the module is well seated in the backplane connectors. Do not damage or bend connector pins.

- Replace the chassis or system cover(s), reconnect the system to the AC or DC power source, and turn the equipment power on, or if hot swapping, you may now install the MCPN750A.

#### Installing the Transition Module in the Chassis

- 1. Attach an ESD strap to your wrist. Attach the other end of the strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

- Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system. Remove chassis or system cover(s) as necessary for access to the chassis backplane.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

- 3. With the TMCPN710 or TM-PIMC-0001 in the correct vertical position that matches the pin positioning of the corresponding MCPN750A board carefully slide the transition module into the appropriate slot and seat tightly into the backplane. Refer to Figure 1-11. TMCPN710 or TM-PIMC-0001/MCPN750A Mating Configuration for the correct board/connector orientation.

- 4. Secure in place with the screws provided, making good contact with the transverse mounting rails to minimize RF emissions.

- 5. Replace the chassis or system cover(s), making sure no cables are pinched. Cable the peripherals to the panel connectors, reconnect the system to the AC or DC power source, and turn the equipment power on.

Figure 1-11. TMCPN710 or TM-PIMC-0001/MCPN750A Mating Configuration

# **MCPN750A Module Power Requirements**

The MCPN750A board draws +5V, +3.3V and VIO power from the J1 connector. The +12V and -12V voltages are monitored by the MCPN750A hot swap controller and provided for use by the PMCs and transition modules. The MCPN750A contains an electronic circuit breaker that limits the total +5V, +3.3V, +12V and -12V current drawn by the MCPN750A. Refer to the table below for the electrical current available to the PMCs and transition modules and Appendix A for other specs.

| Voltage | Current Available to PMCs & Transition Modules |

|---------|------------------------------------------------|

| +5.0V   | 6 Amps                                         |

| +3.3V   | 6 Amps                                         |

| +12.0V  | 1 Amp                                          |

| -12.0V  | 0.4 Amp                                        |

## Introduction

This chapter supplies information for use of the MCPN750A family of Single Board Computers in a system configuration. Here you will find the power-up procedure and descriptions of the switches and LEDs, memory maps, and software initialization.

# **Applying Power**

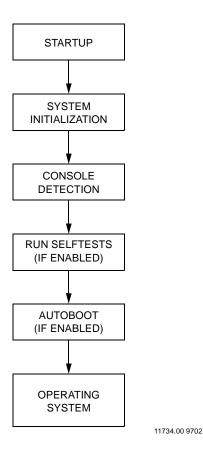

After you have verified that all necessary hardware preparation has been done, that all connections have been made correctly, and that the installation is complete, you can power up the system. The MPU, hardware, and firmware initialization process is performed by the PowerPC<sup>TM</sup> PPCBug power-up or system reset. The firmware initializes the devices on the SBC module in preparation for booting the operating system.

The firmware is shipped from the factory with an appropriate set of defaults. In most cases there is no need to modify the firmware configuration before you boot the operating system.

The following flowchart shows the basic initialization process that takes place during PowerPC system startup.

For further information on PPCBug, refer to Chapters 3 and 4 in this manual, or to the *PPCBug Firmware Package User's Manual*.

2-1

Figure 2-1. PPCBug System Startup

The MCPN750A front panel has one ABORT/RESET switch and three LED (light-emitting diode) status indicators (BFL, CPU, and HOT SWAP STATUS). For more information on front panel operation refer to Chapter 6, *Functional Description*.

# **Memory Maps**

There are three points of view for memory maps:

- ☐ The mapping of all resources as viewed by the processor (MPU bus memory map)

- ☐ The mapping of onboard resources as viewed by PCI local bus masters (PCI bus memory map)

- ☐ The mapping of onboard resources as viewed by the CompactPCI bus.

The following sections give a general description of the MCPN750A memory organization from the above three points of view. Detailed memory maps can be found in the *MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide* (MCPN750A/PG).

## **Processor Memory Map**

The processor memory map configuration is under the control of the Raven bridge controller ASIC and the Falcon memory controller chip set. The Raven and Falcon devices adjust system mapping to suit a given application via programmable map decoder registers. At system power-up or reset, a default processor memory map takes over.

#### **Default Processor Memory Map**

The default processor memory map that is valid at power-up or reset remains in effect until reprogrammed for specific applications. Table 2-1 defines the entire default memory map (\$00000000 to \$FFFFFFF).

Table 2-1. Processor Default View of the Memory Map

| Processor Address |          | Size           | Definition        | Notes |

|-------------------|----------|----------------|-------------------|-------|

| Start             | End      | Size           | Deminion          | Notes |

| 00000000          | 7FFFFFF  | 2GB            | Not Mapped        |       |

| 80000000          | 8001FFFF | 128KB          | PCI/ISA I/O Space | 1     |

| 80020000          | FEF7FFFF | 2GB-16MB-640KB | Not Mapped        |       |

| FEF80000          | FEF8FFFF | 64KB           | Falcon Registers  |       |

Table 2-1. Processor Default View of the Memory Map (Continued)

| Processor Address |          | Size                 | Definition                 | Notes |  |

|-------------------|----------|----------------------|----------------------------|-------|--|

| Start             | End      | Size                 | Deminion                   | Notes |  |

| FEF90000          | FEFEFFF  | 384KB                | Not Mapped                 |       |  |

| FEFF0000          | FEFFFFF  | 64KB Raven Registers |                            |       |  |

| FF000000          | FFEFFFFF | 15MB                 | Not Mapped                 |       |  |

| FFF00000          | FFFFFFF  | 1MB                  | ROM/Flash Bank A or Bank B | 2     |  |

#### Notes

- 1. Default map for PCI/ISA I/O space. Allows software to determine whether the system is MPC105-based or Falcon/Raven-based by examining either the PHB Device ID or the CPU Type register.

- 2. The first 1MB of ROM/Flash Bank A (soldered 4MB Flash) appears in this range after a reset if the **rom\_b\_rv** control bit in the Falcon's ROM B Base/Size register is cleared. If the **rom\_b\_rv** control bit is set, this address range maps to ROM/Flash Bank B (socketed 1MB ROM/Flash).

For detailed processor memory maps, including suggested PREP-compatible memory maps, refer to the *MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide* (part number MCPN750A/PG).

## **PCI Local Bus Memory Map**

The local PCI memory map is the PCI memory map as viewed by the MCPN750A base board. This is also the secondary bus side of the 21554 on the MCPN750A. This map is controlled by the Raven ASIC and the 21554 PCI-to-PCI bridge. The Raven and the 21554 PCI-to-PCI bridge have flexible programmable map decoder registers to customize the system for a wide range of applications.

After a reset, the Raven ASIC map decoders are in their default state. Software must program the appropriate map decoders for a specific environment. The 21554 bridge map decoders default state is determined by the SROM values loaded.

For detailed PCI memory maps, including suggested PREP-compatible memory maps, refer to the *MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide* (MCPN750A/PG).

## **CompactPCI Memory Map**

The MCPN750A uses the 21554 non-transparent PCI-to-PCI bridge to interface between the local PCI bus and the CompactPCI bus. The 21554 is different from traditional PCI-to-PCI bridges in that it uses address translation instead of a flat address map between primary and secondary PCI buses. In the MCPN750A configuration, the primary bus is the CompactPCI bus and the secondary bus is the MCPN750A local bus. Downstream transactions are those that are initiated on the primary bus and are forwarded to the secondary bus. Upstream transactions are those initiated on the secondary bus and forwarded to the primary bus.

#### Address Decoding with the 21554

The 21554 implements multiple base address registers on both the primary and secondary interfaces that denote separate address ranges for both downstream and upstream transactions. It also has base registers for access to its Control and Status Register (CSR) space. Consequently, on the primary interface (CompactPCI bus) the 21554 responds only to those transactions which are in the address range defined by one of the base address ranges. All other addresses are ignored. The same is true for transactions on the secondary interface (local PCI bus).

The address ranges defined by the primary base address registers reside in the primary or system address map. The address ranges defined by the secondary base address registers reside in the secondary or local address map. Each of these address maps is independent of each other. The 21554 provide address translation between these two address maps when forwarding transactions upstream or downstream.

Recommendations for CompactPCI mapping, including suggested PREP-compatible memory maps, can be found in the *MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide* (MCPN750A/PG).

#### L2 Cache

The MCPN750A SBC uses a backside L2 cache structure via the MPC750 processor chip. The MPC750 L2 cache is implemented with an onchip 2-way set-associative tag memory and external direct-mapped synchronous SRAMs for data storage. The external SRAMs are accessed through a dedicated 72-bit wide (64 bits of data and 8 bits of parity) L2 cache port. The MPC750 will support 256KB, 512KB or 1MB of L2 cache SRAMs. The L2 cache can operate in copyback or writethru modes and supports system cache coherency through snooping. Parity generation and checking may be disabled by programming the MPC750 accordingly. Refer to the MPC750 Data Sheet and the MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide (MCPN750A/PG) for additional information.

## **System Clock Generator**

The system clocks for the processor, Raven/Falcon chipset (66 MHz) and each of the onboard PCI devices (33 MHz) are generated by a 66 MHz oscillator and distributed by the MPC949 clock buffer. Separate oscillators are provided as follows: 14.31818 MHz for the PBC internal timer; 20 MHz for the ethernet MAC interface; 25 MHz for the ethernet PHY device; 48 MHz for the USB interface; 1.843 MHz for the serial ports.

#### **PPC Bus Arbitration**

The arbitration control for the PPC bus is provided by a Programmable Logic Device (PLD). There are only two potential PPC masters, Raven and MPC750, with Raven having the highest priority. See the following section titled "PCI Arbitration" for a description of arbitration control of onboard PCI devices.

#### **PCI Host Bridge**

The Raven ASIC provides the bridge function between the PPC60X bus and the onboard PCI Local Bus. Raven is a PCI 2.1 compliant 64-bit PCI implementation for 32/64-bit data transfers. Dual Address Cycle is not

supported. The Raven supports PowerPC processor external bus frequencies up to 66 MHz and PCI frequencies up to 33 MHz. The Raven is connected to the processor data parity signals to provide processor data bus parity generation and checking.

There are four programmable map decoders for each direction to provide flexible address mappings between the PPC/DRAM and the PCI Local Bus. Refer to the *MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide* (MCPN750A/PG) for additional information and programming details.

#### **PCI** Arbitration

The MCPN750A has six potential local PCI bus masters:

- □ the Raven ASIC.

- □ the PBC device (VT82C586B),

- □ the Ethernet device (21143),

- □ the PCI-to-PCI bridge device (21554),

- □ and each of the two PMCs.

The local PCI arbiter is implemented in an onboard PLD. This arbiter implements a rotating priority scheme with equal priorities. Since the PBC device does not support bus parking, the arbiter will park on the Raven when the bus is idle.

## **Interrupt Handling**

The Raven ASIC provides a Multi-Processor Interrupt Controller (MPIC) to handle various interrupt sources. This MPIC supports up to two processors and 16 external interrupt sources. There are also six other interrupt sources inside the MPIC: Two cross-processor interrupts and four timer interrupts. All ISA interrupts go through the 8259 pair in the Peripheral Bus Controller (PBC). The output of the PBC then goes through the MPIC in Raven.

Since the MCPN750A board is designed to support processor data bus parity, the Raven uses some of the pins normally used as external interrupt inputs as parity pins. Therefore, an Interrupt Multiplexer device, implemented in a PLD, is used to scan the external MPIC interrupts into Raven as a serial bit stream using the Raven SISTA and SIDAT pins. This operation is automatic and transparent to the software. A maximum delay of 240 nanoseconds should be expected from the time that the external interrupt is generated and when it is presented to the MPIC. Sources of interrupts may be any of the following:

☐ The Raven ASIC itself (four MPIC timer interrupts or transfer error interrupts)

- ☐ The Processor 0 (processor self-interrupts)

- ☐ Transfer Error Interrupt (from the Raven ASIC)

- ☐ The Falcon chip set (memory error interrupts)

- ☐ The PCI bus (interrupts from PCI devices)

- ☐ The CPCI bus (interrupts from CPCI devices)

- Power monitor interrupts

- □ Watchdog timer interrupt

- ☐ The ISA bus (interrupts from ISA devices)

The ISA interrupts are handled as a single 8259 interrupt from the VT82C586B PBC device.

For details on interrupt handling, refer to the MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide (MCPN750A/PG).

#### ISA DMA Channels

The PBC supports seven 8237 compatible DMA channels. ISA compatible type A, B and F timing is supported. These DMA channels are not used since there are no ISA DMA devices.

#### **Sources of Reset**

The MCPN750A SBC provides reset control from various sources and identifies the source of the reset in a software readable register. Hard or soft resets may be generated. A hard reset is defined as a reset of all onboard circuitry including the PowerPC hard reset and reset of all onboard peripheral devices. A soft reset is defined as a reset of the PowerPC. The MCPN750A SBC has seven potential sources of reset:

- 1. Power-on/Undervoltage Reset.

- 2. Front Panel RESET switch (will generate a hard reset when depressed).

- 3. CompactPCI Push Button Reset (RST#) from the CompactPCI backplane.

- 4. Watchdog timer Reset function controlled by the SGS-Thomson MK48T559 Watchdog Timer or the Raven Watchdog Timer.

- 5. Software Hard Reset (PBC Port 92 Register)

- 6. 21554 PCI-to-PCI bridge Secondary Reset Bit

- 7. 21554 PCI-to-PCI bridge Chip Reset Bit.

The following table shows which devices are affected by the various types of resets. For details on using resets, refer to the *MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide* (part number MCPN750A/PG).

Table 2-2. Classes of Reset and Effectiveness

| Device Affected                           | Processor | Raven<br>ASIC | Falcon<br>Chip Set | 21554<br>Bridge | ISA<br>Devices | Other PCI<br>Devices |

|-------------------------------------------|-----------|---------------|--------------------|-----------------|----------------|----------------------|

| Reset Source                              |           |               |                    |                 |                |                      |

| Power-On/undervoltage                     | √         | √             | √                  | √               | √              | √                    |

| Front Panel Reset switch                  | √         | √             | <b>√</b>           | √               | √              | √                    |

| CompactPCI PRST#                          | √         | √             | <b>√</b>           | √               | √              | √                    |

| Watchdog Timer reset                      | √         | √             | <b>√</b>           | √               | √              | √                    |

| S/W Hard Reset (PBC<br>Port 92 Register)  | √         | √             | √                  |                 | √              | <b>V</b>             |

| CompactPCI Reset* (21554 Secondary Bit)   | √         | √             | √                  | #               | <b>V</b>       | <b>√</b>             |

| CompactPCI Reset** (21554 Chip Reset Bit) | √         | √             | √                  | <b>V</b>        | √              | <b>V</b>             |

# 21554 Secondary Reset Bit does not reset the 21554 register state but does reset the 21554 data buffers.

<sup>\*</sup> A configuration write is required to clear the Secondary Reset Bit after it has been written so this bit must not be set by the local MCPN750A processor or else the board will lock up.

\*\* If the Chip Reset Bit is set to a 1, the bit will clear itself after the chip reset is complete.

#### **Power-On Reset**

The MCPN750A SBC generates a hard reset at power-on. During power up, reset is maintained for 140 to 560 milliseconds after the voltages have reached the minimum threshold.

#### **Undervoltage Reset**

The MCPN750A SBC generates a hard reset when the Hot Swap power control chip (LTC1643) detects a supply voltage +5V, +3.3V, +12V or -12V fall below minimum thresholds of +4.75V, +3.135V, +10.8 and -10.8 volts respectively. The reset is maintained for 140 to 560 milliseconds after the voltages have returned to the minimum threshold. For undervoltage, the Vcc threshold to reset delay is typically 10 microseconds.

#### Front Panel Push Button Reset

The front panel RESET switch generates a hard reset when depressed for more than three (3) seconds. The reset is maintained as long as the switch is depressed.

#### CompactPCI Reset (RST#)

The CompactPCI reset signal RST# is monitored by the 21554 PCI-to-PCI bridge chip as the primary bus reset input. The bridge will generate a secondary bus reset that is used to generate a board hard reset.

#### Watchdog Timer Reset

Both the Raven ASIC Watchdog Timer 2 and the M48T559 watchdog timer may generate a hard reset when the associated timer expires, if this function is enabled.

#### **Software Resets**

The software is able to generate a 200 millisecond hard reset by programming the PBC Port92 register or a soft reset by writing to the Processor Init Register of the Raven MPIC. Note that the Port 92 reset will reset every device on the board except the 21554 bridge chip. Refer to the *MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide* (MCPN750A/PG) for register details. A board hard reset may also be generated by writing to the 21554 Bridge Control register from the PCI address space. This allows the System Slot processor to do a software controlled reset of the MCPN750A SBC. Refer to the Intel 21554 Data Sheet for details.

#### **Reset Source Identification**

The source of any hard reset can be identified following the reset by reading the Reset Source register. Refer to the *MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide* (MCPN750A/PG) for bit assignments.

#### **Endian Issues**

The MCPN750A supports both little-endian and big-endian software. The PowerPC is inherently big-endian, while the PCI bus is inherently little-endian. The following sections summarize how the MCPN750A handles software and hardware differences in big- and little-endian operations. For further details on endian considerations, refer to the MCPN750A CompactPCI Single Board Computer Programmer's Reference Guide (MCPN750A/PG).

#### **Processor/Memory Domain**

The MPC750 processor can operate in both big-endian and little-endian mode. However, it always treats the external processor/memory bus as big-endian by performing *address rearrangement and reordering* when running in little-endian mode. The PPC registers in the Raven PCI bus bridge controller ASIC and the Falcon memory controller chip set, as well as DRAM, ROM/Flash, and system registers, always appear as big-endian.

#### Role of the Raven ASIC